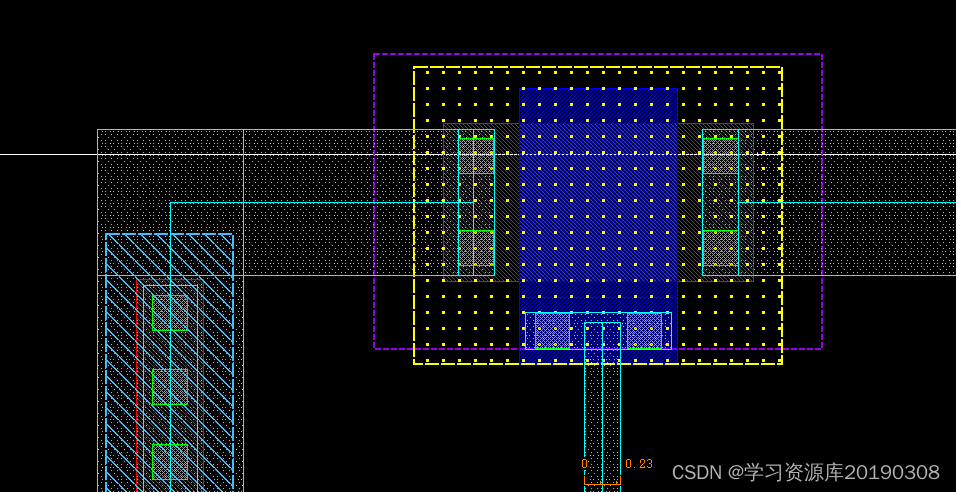

1、问题:cadence中,绘制完layout,下一次直接点击打开layout时,layout无法显示器件节点

,如图

解决方法:

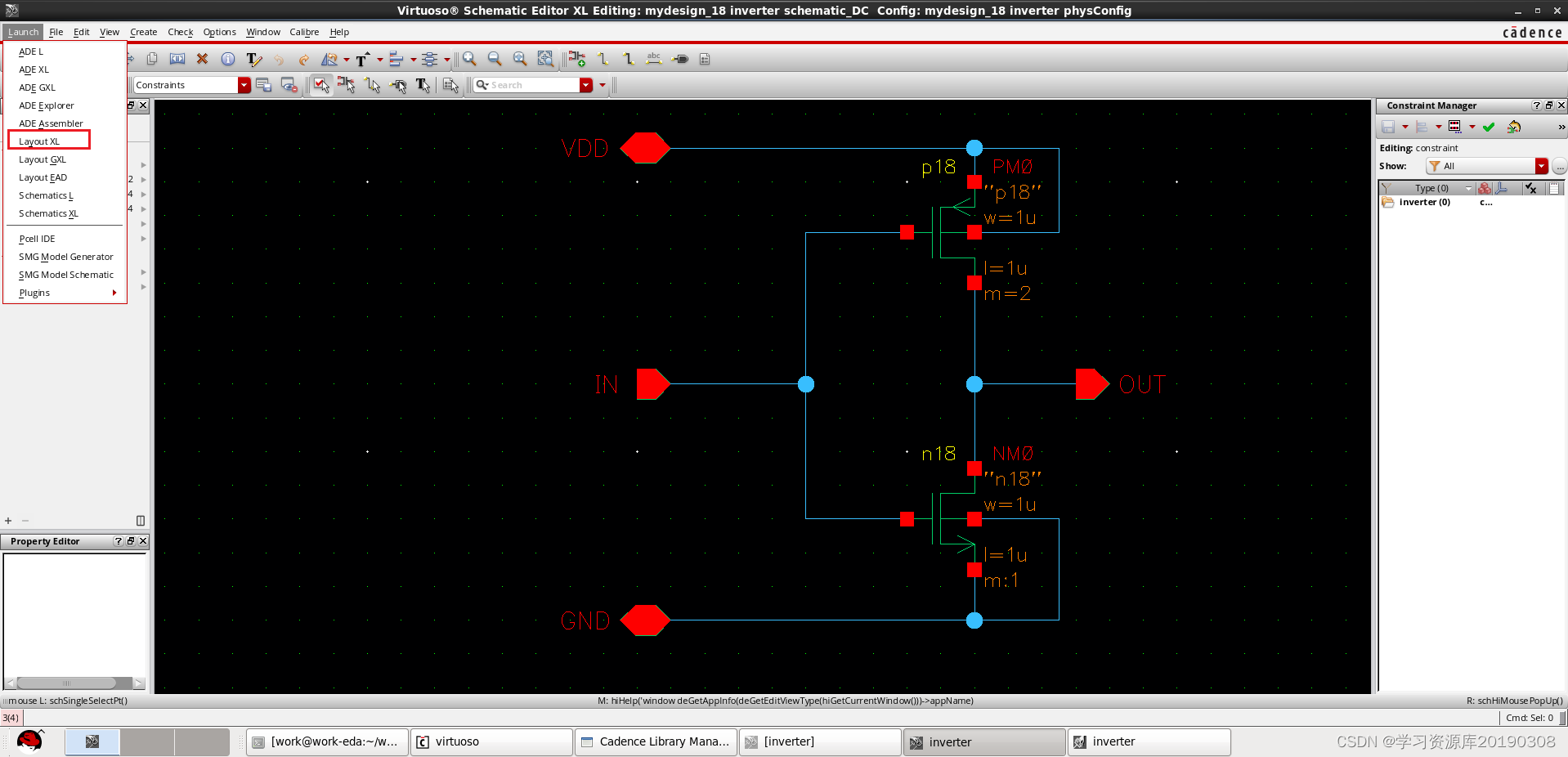

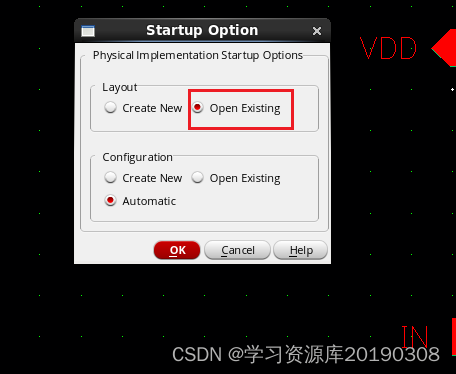

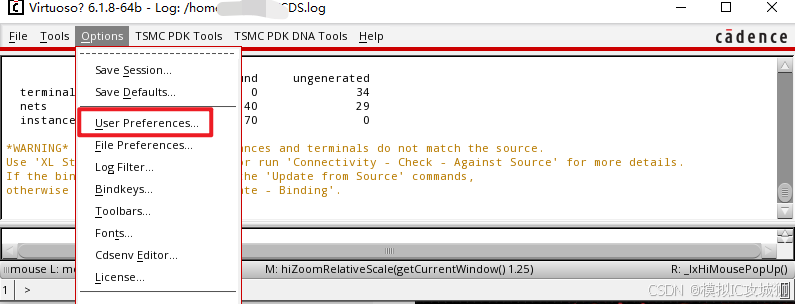

先打开layout对应的schematic,按下图操作

注意选择 Open Existing,从这里打开之后就能够显示器件节点名称了

注意选择 Open Existing,从这里打开之后就能够显示器件节点名称了

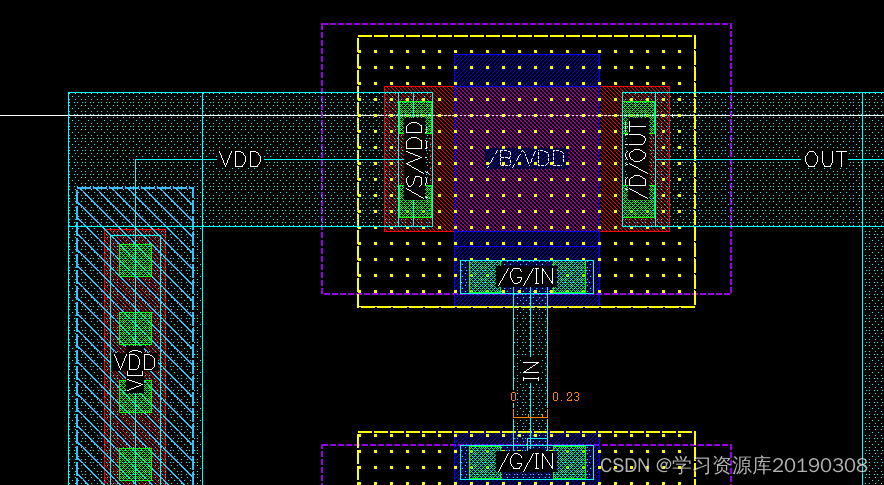

成功显示!

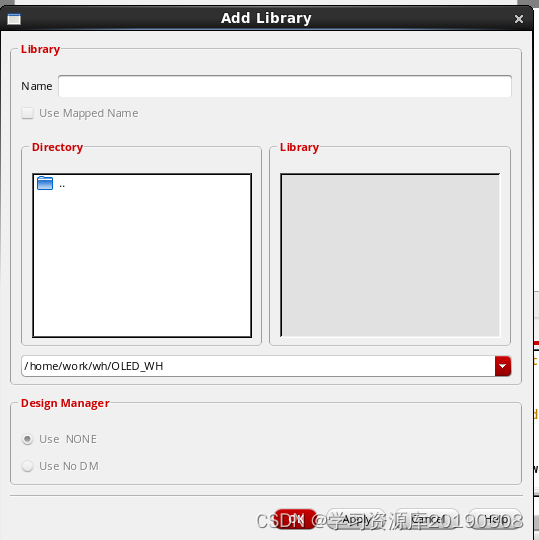

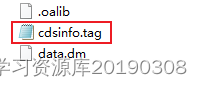

2、问题:cadence中在virtuoso中,添加自己创建的library,在文件夹中找不到,如图

解决方法,查看之前添加的其他库文件夹,里面有一个名称为 cdsinfo.tag的文件,将此文件复制到需要添加的library文件夹中即可

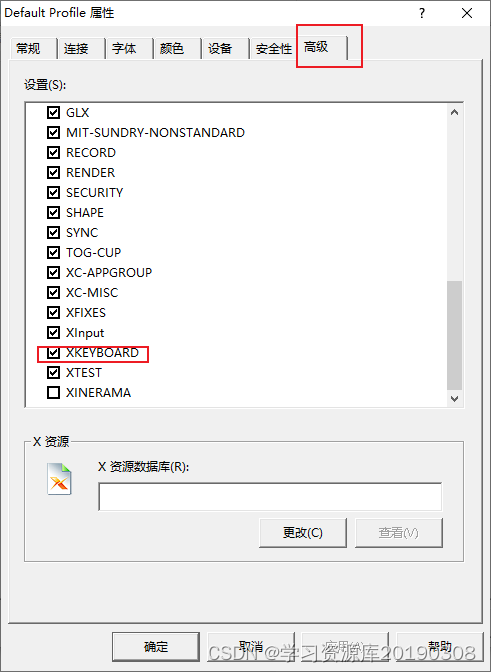

3、问题:用Xshell 登录服务器,进入Virtuoso 中键盘输入乱码

登录Xstart

输入账号密码,点击高级

点击配置

选择高级,勾选XKEYBOARD

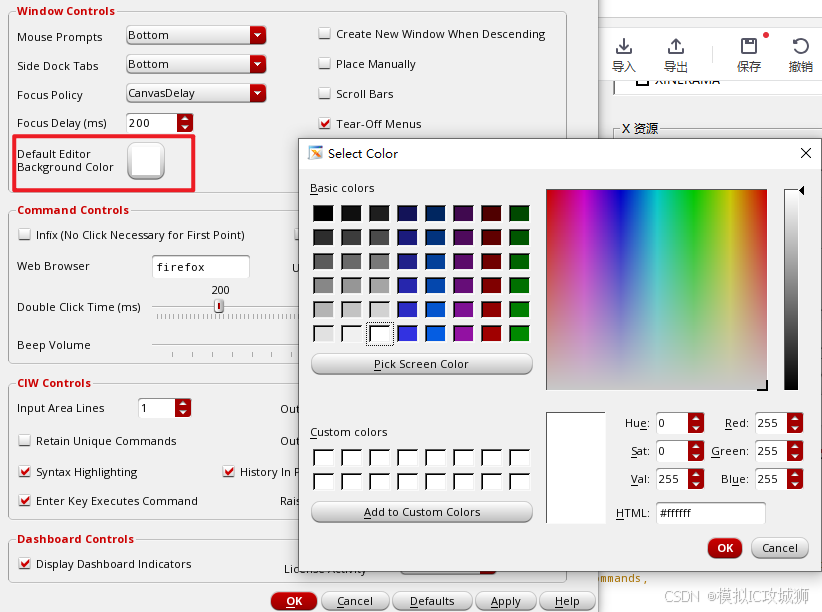

4、修改cadence版图绘制底色背景为白色

四 、个人宣传——几个已经完成的SAR ADC项目

4.1、10bit 20MHz SAR ADC

10bit SAR ADC 设计,smic18工艺,有工艺库,有效位数ENOB为9.8

常用栅压自举开关Bootstrap,Vcm_Based开关时序,上级板采样差分CDAC阵列,两级动态比较器,比较器高速异步时钟,动态sar逻辑,10位DFF输出,10位理想DAC还原做DFT。

包括详细仿真文档,原理介绍,完整电路图,仿真参数已设好,可直接使用,在自己的电脑上就可以运行仿真。适合入门SAR ADC的拿来练手

4.2、12bit 100MHz Pipelined ADC

12bit 100MHz pipelined ADC 设计

65nm工艺,电源电压1.2V,ENOB=11.6

结构:

栅压自举开关

CDAC

两级动态比较器

第一级6位SAR ADC

余量放大器

第二级8位SAR ADC

同步和异步SAR logic都有

4.3、李福乐老师8bit SAR ADC

清华大学李福乐8bit SAR ADC设计

结构:

分段式电容阵列

经典两级动态比较器

工艺库+电路+设计文档;

工艺库和电路均转成OA版本,可直接导入

送李老师的课件,包含详细设计思路

有matlab代码,FFT,计算ENOB SNDR SFDR SNR THD

适合入门SAR ADC的拿来练手

SAR ADC 详细介绍

SAR ADC详细介绍传送门

1799

1799

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?