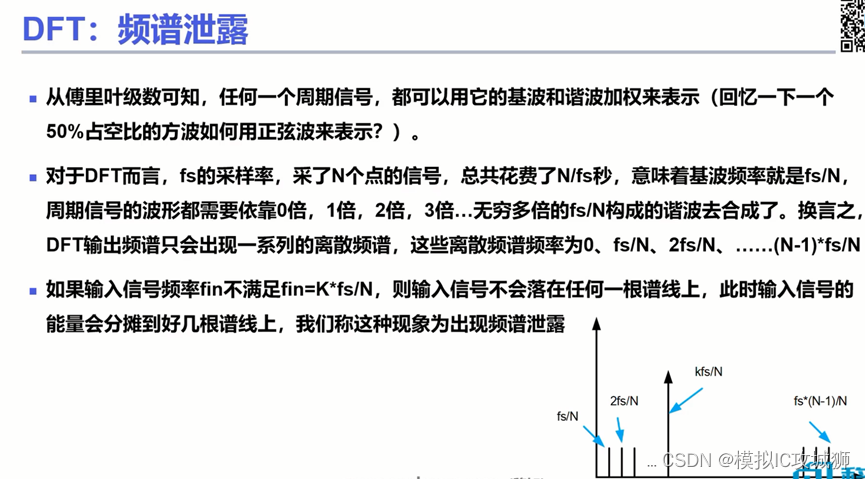

频谱泄露的出现以及如何规避?

为什么要相干采样?

1.分析ADC输出信号的频谱工具:DFT(Discrete Fourier Transform)

重点:DFT相邻频谱频率间隔为fs/N

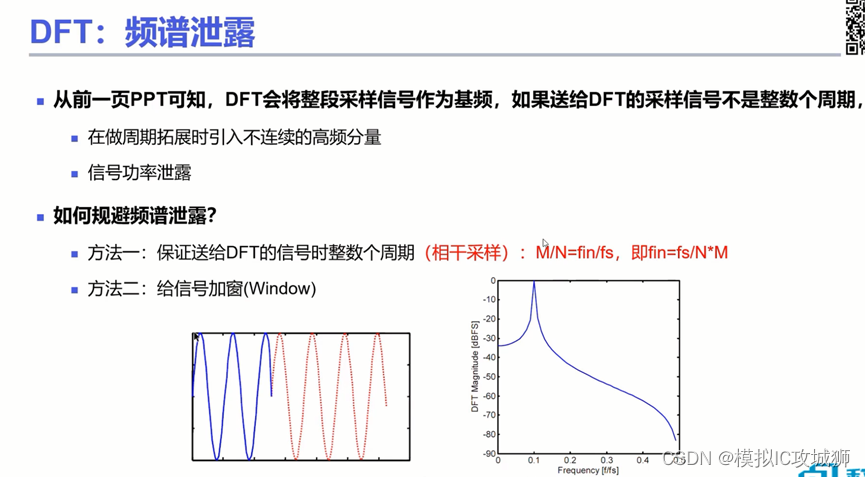

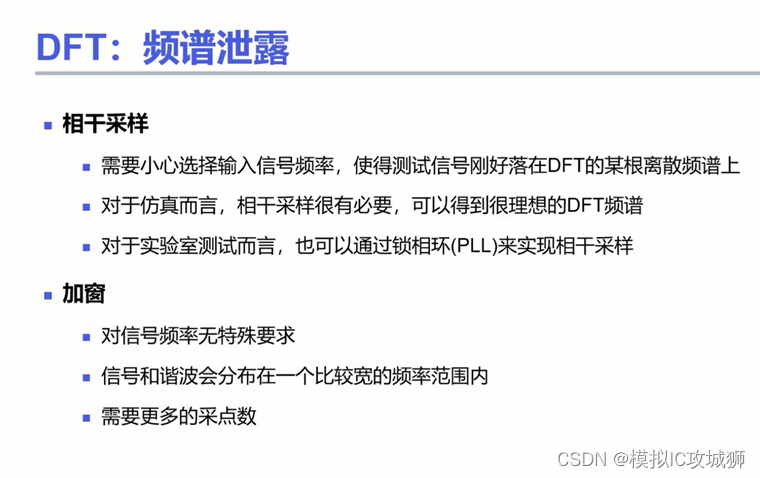

如何规避频谱泄露?

对于DFT,它对于接收到的信号只是机械性的重复延展,所以采样的信号需满足整数个周期

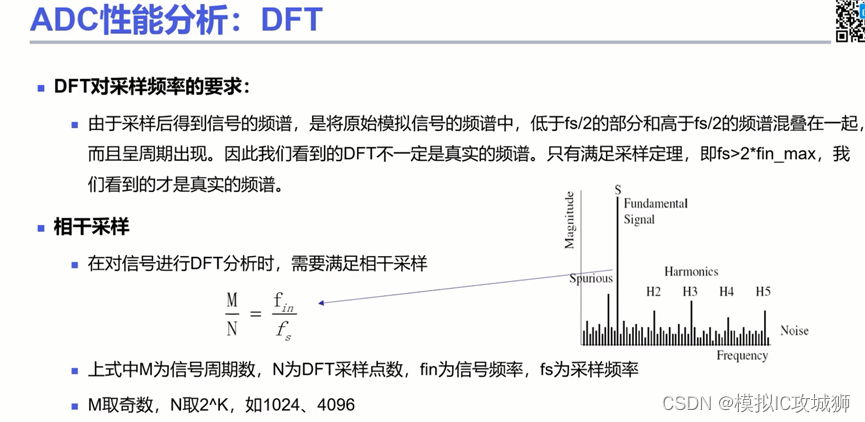

相干采样的要求

根据相干采样设置确定fin,(在采样频率fs确定的情况下):

fin=M*fs/N

在cadence下进行DFT仿真的方法

进行瞬态仿真,得到输出信号,进行FFT仿真主要有两个方法:

1.Cadence Spectrum工具

打开Spectrum,选定输出信号,设置一个稳定的采样起点t0,终点时间设置为t0+N/fs;

采样点数为N;谐波设置可以设置多点

——plot

得到FFT频谱图,以及ADC相关的动态性能参数。

2.MATLAB计算

选中仿真出的输出信号波形-右键-send to-export,选择格式为csv,start从一个稳定时刻开始,end默认就可以,step就是1/fs,比如50M,step就是20n,然后导出文件。打开matlab代码main,修改读取的文件,运行得到ADC的输出频谱图及相关动态性能参数值。

在满足相干采样时,DFT输出的结果

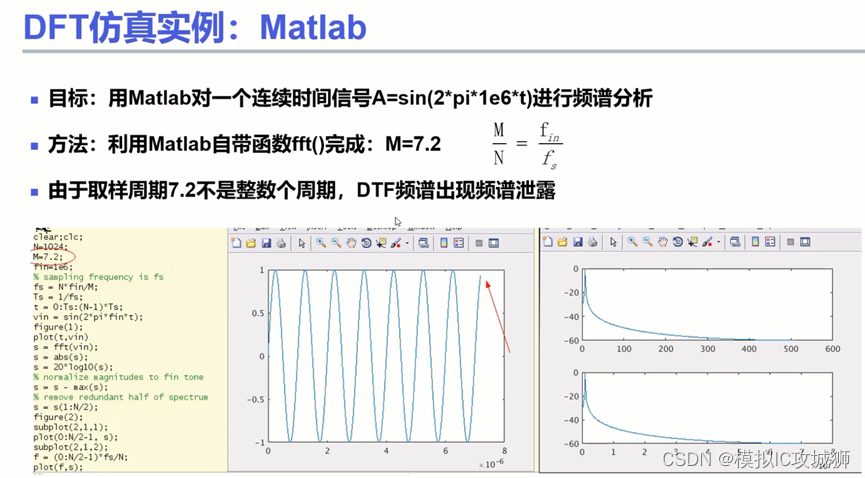

在不满足相干采样时,DFT输出的结果

4382

4382

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?