目录

1. 特权级

一个 RISC-V 硬件线程(hart)是运行在某个特权级上的,这个特权级被编码到一个或者多个 CSR(control and status register,控制和状态寄存器)中的一种模式。

当前定义了四种特权级,如下所示。

| 级别 | 编码 | 名字 | 缩写 |

| 0 | 00 | 用户模式 | U |

| 1 | 01 | 管理员/监管者模式 | S |

| 2 | 10 | 保留 | H |

| 3 | 11 | 机器模式 | M |

- 特权级的作用:被用于在不同的软件栈部件之间提供保护;

- 现象:试图执行当前特权模式不允许的操作, 将导致一个异常的产生。这些异常通常会导致下层执行环境或者 HAL 产生自陷(trap)。

机器级是最高级特权,也是 RISC-V 硬件平台唯一必须的特权级。

- 机器模式(M-mode):代码是固有可信的(inherently trusted),因为它可以在低层次访问机器的实现;

- 用户模式(U-mode):被用于传统应用程序;

- 管理员模式(S-mode):被分别用于操作系统;

所有硬件实现必须提供M-mode,因为这是唯一的模式,可以不受限制地访问整个机器。 最简单的RISC-V实现可以仅提供M-mode,虽然这样做不能为防止不正确的、恶意应用代码提供保护。许多RISC-V实现还支持至少一个用户模式(U-mode),以对系统的其他部分进行保护,防止被应用程序代码破坏。管理员模式(S-mode)可被加入,以在管理员级操作系统和SEE、HAL之间提供隔离。

一个 hart(硬件线程)通常在 U-mode 下运行应用程序,直到某些自陷(例如一个管理 员调用或者一个定时器中断)强制切换到一个自陷处理函数(trap handler),这个自陷处理 函数通常运行在更特权的模式下。然后这个线程将执行这个自陷处理器函数,它最终在 U-mode 下,在引起自陷的指令处或之后,继续线程执行。提升特权基级别的自陷称为垂直 自陷(vertical trap),而保持在同样特权级别的自陷称为水平自陷(horizontal trap)。RISC-V 特权体系结构提供了将自陷灵活地路由到不同的特权层。

2. 控制和状态寄存器(CSR)

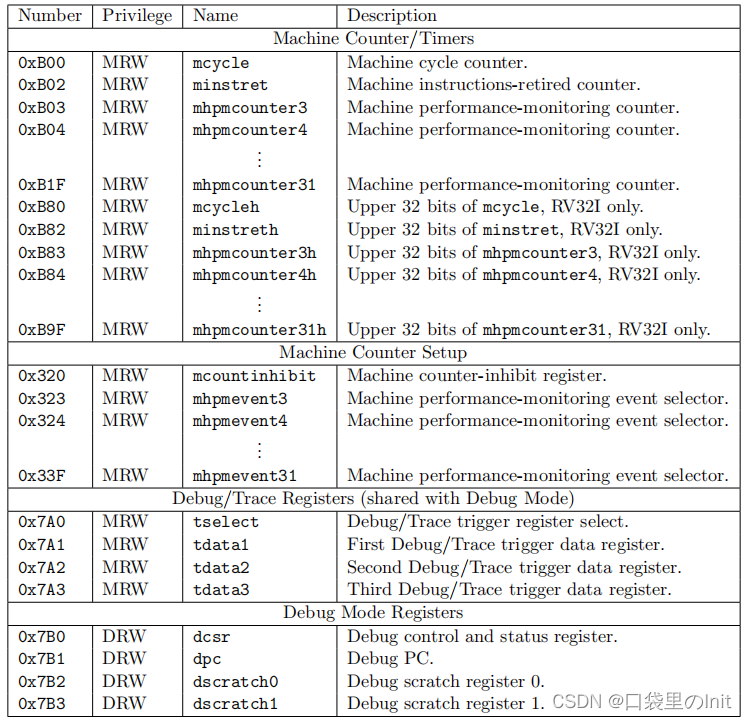

2.1 分类

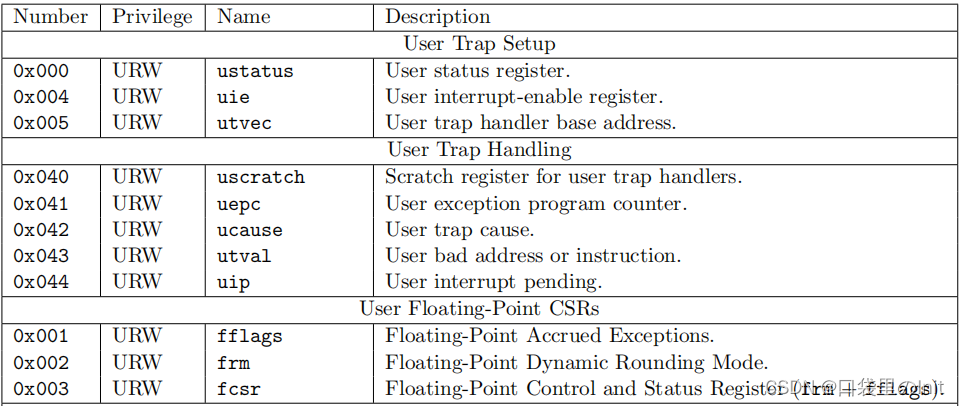

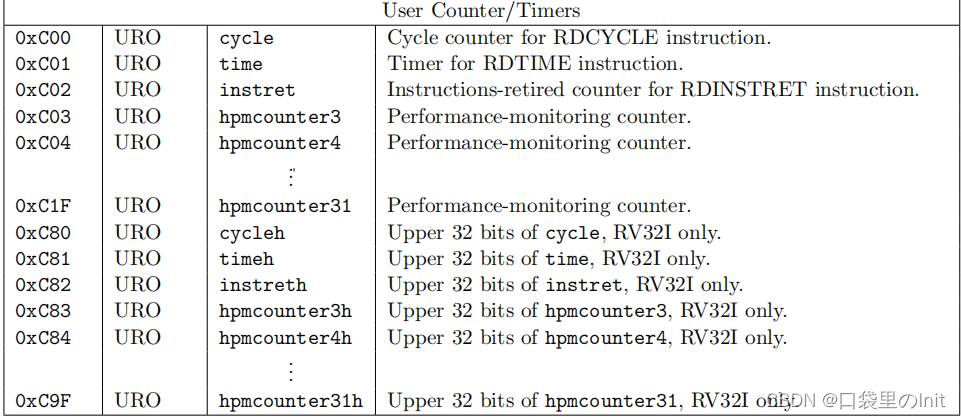

用户级:

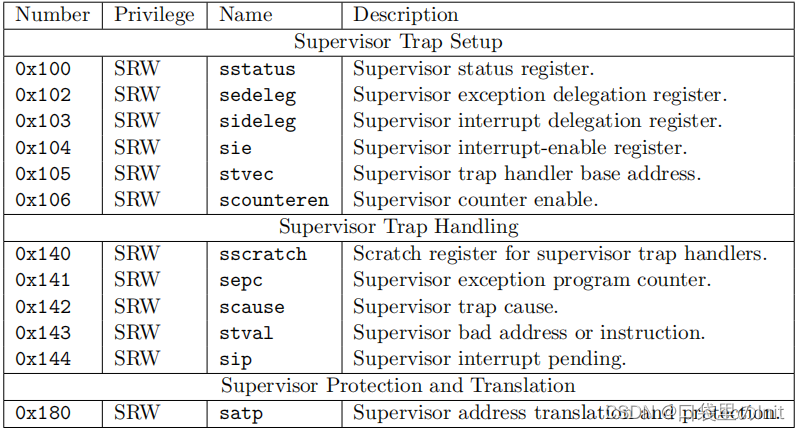

管理员级:

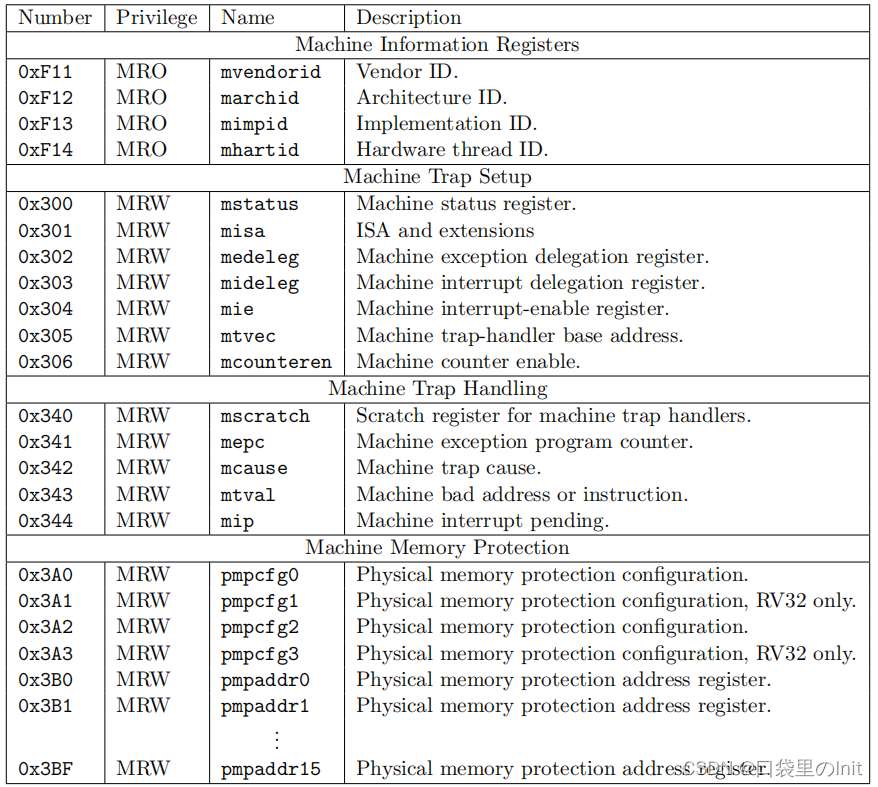

机器级:

2.2 分析

高权限模式通常可以使用权限较低的模式的所用功能,并且它们还有一些低权限模式下不可用的额外功能,例如:

- 处理中断和执行 I/O 的功能

- 处理器通常大部分时间都运行在权限最低的模式下

- 处理中断和异常时会将控制权移交到更高权限的模式

RISC-V 特权体系结构定义的所有指令的指令集:

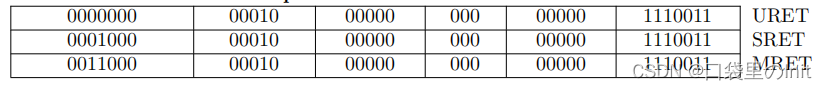

(1)mret、sret、uret

mret、sret或uret指令用于从m模式中的自陷重定向。

(2)sfence.vma

supervisor-mode fence.virtual memory addreee,刷新当前CPU下的TLB,在多核系统中,如果一个hart修改了页表,执行sfence.vma之后,仅仅是刷新了当前hart的TLB,无法刷新其他hart的TLB。

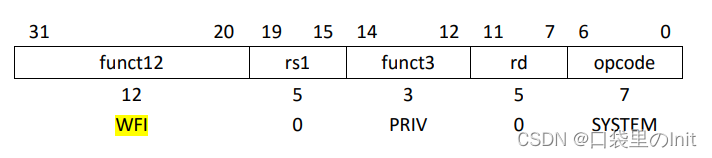

(3) wfi

等待中断指令。

等待中断指令(WFI)用于提供提示,即当前的hart可以暂停,直到有需要处理的中断。WFI指令的执行也可以用于通知硬件平台适当的中断应该优先路由到该hart。WFI可在所有特权模式下使用,也可选择在U模式下使用。

当在mstatus中TW=1时,此指令可能引发非法指令异常。

如果当硬件线程被暂停时,出现一个使能的中断或者后来出现了一个,将会在下一条指 令处执行中断异常,即自陷处理函数继续执行,并且 mepc=pc+4。

(4)寄存器操纵

csrr,读取一个 CSR 的值到通用寄存器。如:csrr t0, mstatus,读取mstatus的值到t0中。csrw,把一个通用寄存器中的值写入 CSR 中。如:csrw mstatus, t0,将t0的值写入mstatus。csrs,把 CSR 中指定的 bit 置 1。如:csrsi mstatus, (1 << 2),将mstatus的右起第 3 位置 1。csrc,把 CSR 中指定的 bit 置 0。如:csrci mstatus, (1 << 2),将mstatus的右起第 3 位置 0。csrrw,读取一个 CSR 的值到通用寄存器,然后把另一个值写入该 CSR。如:csrrw t0, mstatus, t0,将mstatus的值与t0的值交换。csrrs,读取一个 CSR 的值到通用寄存器,然后把该 CSR 中指定的 bit 置 1。csrrc,读取一个 CSR 的值到通用寄存器,然后把该 CSR 中指定的 bit 置 0。

本文详细解释了RISC-V架构中的特权级概念,包括四种不同级别(用户、管理员、保留和机器),以及控制和状态寄存器(CSR)的分类和功能,如中断处理、寄存器操作等。

本文详细解释了RISC-V架构中的特权级概念,包括四种不同级别(用户、管理员、保留和机器),以及控制和状态寄存器(CSR)的分类和功能,如中断处理、寄存器操作等。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?