将cable通过usb连接到linux下,通过lsusb查看,可以列出和枚举所有 USB 设备,如下所示:

[IC@IC bin]$ lsusb

Bus 001 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hub

Bus 002 Device 001: ID 1d6b:0001 Linux Foundation 1.1 root hub

Bus 003 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hub

Bus 004 Device 001: ID 1d6b:0003 Linux Foundation 3.0 root hub

Bus 003 Device 002: ID 0e0f:0003 VMware, Inc. Virtual Mouse

Bus 003 Device 006: ID 336c:1001

Bus 003 Device 004: ID 0e0f:0002 VMware, Inc. Virtual USB Hub

Bus 003 Device 005: ID 0e0f:0002 VMware, Inc. Virtual USB Hub

[IC@IC bin]$

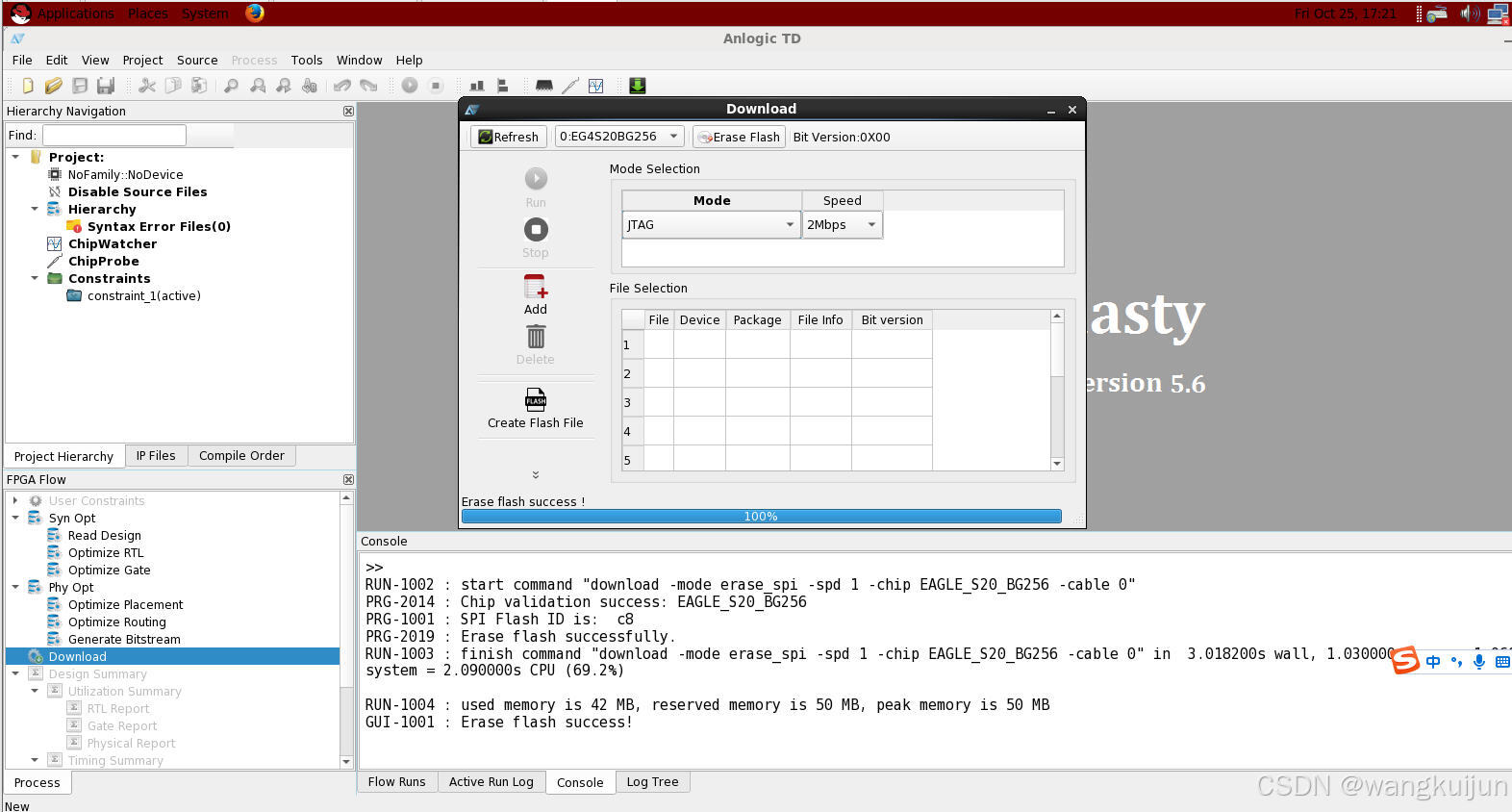

获取设备权限并运行TD软件

chmod 0666 /dev/bus/usb/003/006 ./td.sh -gui &

打开download后,正常识别到芯片。

1648

1648

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?