这是一个真实的Case。

系统描述:使用FPGA普通IO做LVDS接收,一共四路,每一路有4路数据和一路时钟,数据速率约为700Mbps。LVDS接收部分的设计采用Xilinx XAPP585参考设计的源代码,基本没有做改动。

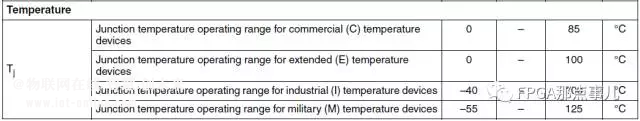

所用器件:Kintex7,-3速度等级,商业档

现象描述:在做高温测试时,在芯片结温超过100°C之后(芯片结温可以用JTAG实时监测),四路LVDS之一接收到的数据开始出现明显的误码,此时其它几路还能正常工作。

从Xilinx器件本身来说,商业档的芯片,手册标称的温度范围是0-85℃,即使是-E等级的芯片,标称也不过是0-100℃。

从测试现象来说,LVDSrx在100℃以后出问题,其实已经超过了普通商业档芯片的标称工作范围,似乎继续追究下去已经没什么太大意义。

但凡事无绝对,尤其是像FPGA这样具有极大灵活度的芯片。按照以往的经验,FPGA芯片的标称范围,一般不是一个绝对的指标,跟硬件和软件设计都有莫大的相关性。本着死马当活马医的态度,姑且继续尝试一下,没准我们能发现一些更深层次的问题,能继续深挖潜能呢!

分析过程:

先从最基本的可能影响LVDS接口的因素一点点排查。

1. 电源

用示波器分析了不同温度下电源的文波范围,主要的核压,辅助电压,和IO电压在100℃及以上,也仍然在许可范围内。先暂时排除电源的影响。

2. 终端电阻

测试不同的终端电阻匹配,内部电阻 or 外部匹配电阻,现象没有太大差异。

3. 测量信号完整性

用高速示波器抓取LVDS信号的波形,通过眼图来看,即使在100℃以上,眼图特性也是不较好的。也暂时排除信号完整性的问题。

至此外部的因素基本排查完毕,没有发现特别的疑点。那么会不会是FPGA逻辑设计的问题呢?

4. 先精简代码,把无关紧要的内部处理模块都去除,只保留LVDS接口,DDR控制器,以及原始设计的时钟网络部分。现象无改善。

5. 分析LVDS设计部分的源代码,基本是基于XAPP585。其内部的动态校准逻辑代码,完全是参考设计,没有发现可以优化的地方。

6. 分析布局布线后的网表,有一个疑点显现出来。

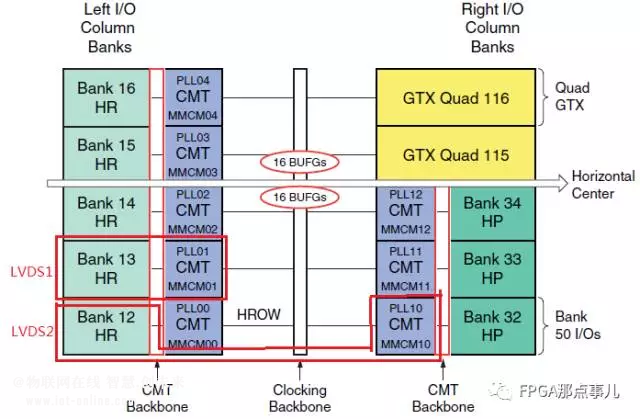

所使用的FPGA,从内部结构上看,分为2个column。在100℃仍能工作正常的那三路LVDS,其IO所在的bank和其所配合的PLL(CMT),都处于同一列IO Column之中。出问题的那一路LVDS,其IO bank在12,但是其配合的PLL,却被放置在了Bank32(RIght Column),有没有可能是由于时钟布线距离过远,造成采样时钟质量的恶化呢?

解决办法:

通过在xdc中,添加位置约束,强制每一路LVDS所调用的PLL,走放置在其相邻的位置。重新布局布线后,实测结温上升到120℃,LVDS仍然能够正常工作。

转载:实战分享:LVDS接收在高温(≥100°C)不稳定的问题,分析及解决 _物联网在线

364

364

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?