摘要:在数字设计中,需要持续关注模拟网络上的串扰风险问题,传统流程中通常不会分析此问题。本文将介绍一种利用PrimeTIme-SI来生成由数字信号在模拟网络上引起的串扰上限的技术。如果此技术揭露出潜在的问题,则会通过HSPICE进行进一步分析。

1. 简介

与过去相比,现代SoC设计的利润空间更低、掩膜成本更高。这两点增加了对一次投片成功率的要求。过去使用的专门方法已经不足以确保一次投片成功率,因此需要新的分析方法。SoC设计的诸多领域都遇到了这一问题并已得到妥善解决,因此,芯片的数字部分与模拟部分间的交互便成为最后的棘手问题之一。

本文将介绍一种利用PrimeTIme-SI(PT-SI)来测量芯片数字部分对模拟部分产生的串扰的分析方法。内容包括使用此方法时遇到的问题以及各种限制和优势。

2. PrimeTIme-SI中的噪声

PT-SI用于计算两种形式的串扰延迟变化和噪声。近年来,延迟变化功能受到广泛的关注,而噪声影响则未得到如此多的注意。

2.1 PT-SI如何计算噪声

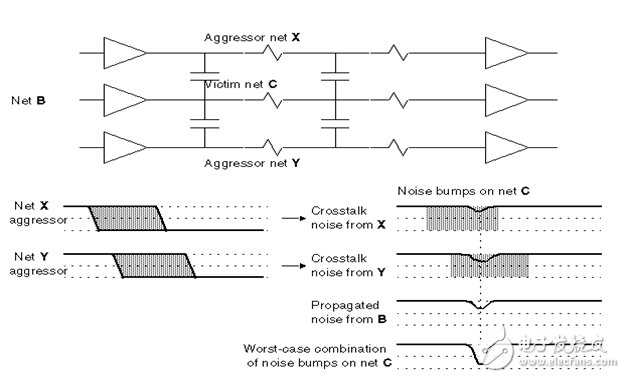

下面的图1是来自SOLVNET的图像,说明了PT-SI如何计算噪声。如图所示,干扰源在被干扰网络中引入了一个噪声冲击,当干扰源的时序重叠时,噪声冲击便会叠加在一起。尽管这是一种简化的说明,但足以达到我们的目的。

本文介绍了如何利用PrimeTIme-SI分析芯片数字部分对模拟部分产生的串扰,特别是在模拟网络上的噪声计算。通过设置和实验,揭示了PT-SI在处理模拟网络噪声计算的能力及其限制,为模拟网络噪声分析提供了一种新方法。

本文介绍了如何利用PrimeTIme-SI分析芯片数字部分对模拟部分产生的串扰,特别是在模拟网络上的噪声计算。通过设置和实验,揭示了PT-SI在处理模拟网络噪声计算的能力及其限制,为模拟网络噪声分析提供了一种新方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?