前介绍了电源噪声和衬底噪声的产生机理(数字模拟混合电路电源芯片衬底噪声的形成机理 SOC芯片电源完整性PI片上IRdrop分析-IRdrop产生机理),还有一些芯片因素对PI的影响(SOC芯片Power Gating对电源完整性的影响 SOC芯片Clock Gating电路对电源完整性的影响),那这些电源噪声的产生对芯片性能有什么影响呢?这一篇就来介绍下,电源噪声和衬底噪声两种形式的噪声的出现是由于数字电路中的开关电流,以及它们相对电源电压的大小有望使低压高集成度变为可能。

在数字电路中,电源噪声影响表现为信号延迟变化,衬底噪声影响更少一些。由于动态供应噪声引起的间歇时序错误被归为电气缺陷,其根本原因分析及解决方法在超大规模集成电路设计( VLSI)和测试中得到越来越多的关注。

另一方面,对于模拟电路,电源噪声和衬底噪声对性能是不利的。电源和地电压通常是专门提供的,由数字电路诱发的电源噪声不会影响模拟电路。即使在这种情况下,在器件封装和印制电路板的制备过程中,数字和模拟电源之间的耦合也会诱发噪声。另外,硅衬底通常由数字和模拟电路共享,衬底噪声降低模拟电路的性能。

电源噪声和衬底噪声

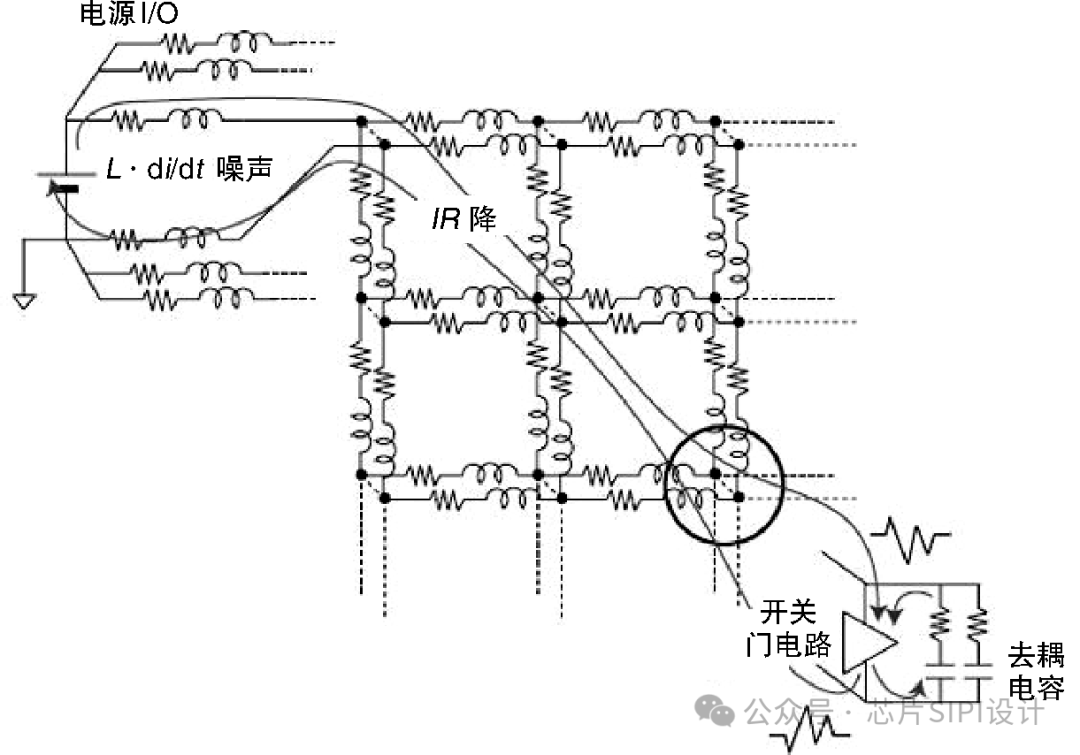

在超大规模集成电路设计中,配电网络( PDN)将电源电压分发到所有电路元件,例如逻辑门和触发器,PDN是用来产生一个稳定的电源电压。在一个超大规模集成电路 ( VLSI) 封装芯片中,如下图,电源和地通过 PDN 供电,PDN由电源I/O(外壳引线和焊接)和芯片上的线组成。尽管PDN 的设计是对电流产生很低的阻抗,因为CMOS电路开关电流流经电源线包括寄生电阻、电容和电感。电源电压必须减少与/或波动,这种减少的与/或波动称为电源噪声。

片上电源噪声主要由IR降和L·di/dt噪声组成。加宽电源线是减小IR降的主要技术,却使得信号布线变得复杂并消耗芯片金属资源。然而,该技术并不能减少由封装寄生元素带来的L·di/dt噪声,也不能解决由高频电流带来的片上电感噪声,而该高频电流由趋肤效应和电流拥塞带来的。另外,更宽的线减小了阻尼效应但增加了L·di/dt噪声。为了抑制IR降峰值和L·di/dt噪声,因为去耦电容提供本地供电电流和旁路高频部件的开关电流,所以是必须的。

减少片上电感噪声的方法:通过增加VDD-VSS总线的数量而不是增加VDD-VSS总线的宽度。

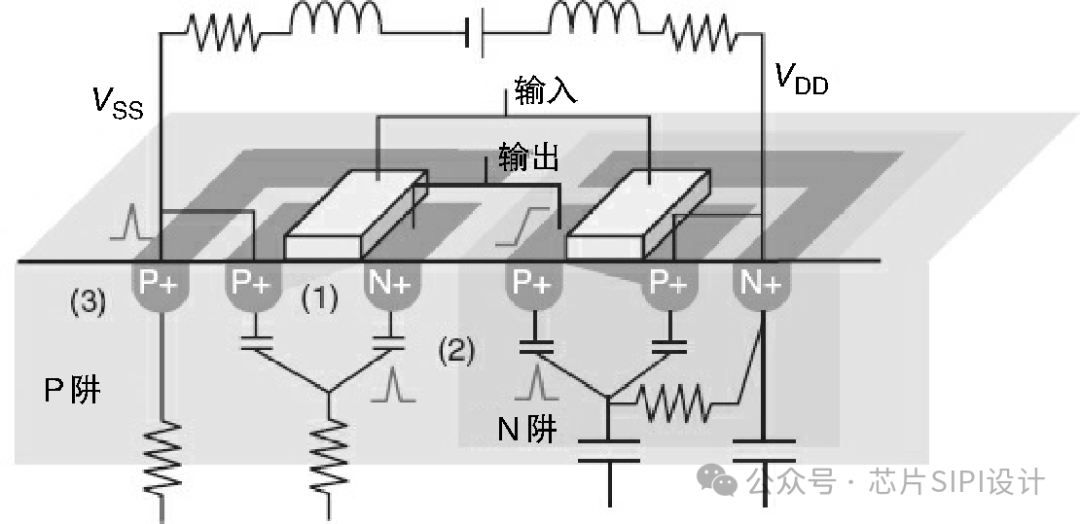

另一个问题是衬底噪声。前面几篇文章介绍了衬底噪声形成机理,可以参考下(数字模拟混合电路电源芯片衬底噪声的形成机理 数字模拟混合芯片电源衬底噪声的影响和优化)。下图说明了三个能引起换流器衬底噪声的机制:(1)碰撞电离(2)源漏耦合(3)电源耦合。碰撞电离电流就是空穴电流由于热电子效应从漏极转移到衬底。在源/漏节点通过PN节电容在晶体管源/漏区和衬底/阱开关噪声注入到衬底。在P型衬底上,电源噪声通过N阱结电容和电阻使衬底电容增加。

衬底噪声的主要机制是定量的,随着缩放技术发展,当芯片衬底直接偏置到数字地,由于电源耦合造成的衬底噪声变成了主导耦合机制。接下来,随着缩放技术发展,电源耦合噪声的峰值更依赖于开关电容相比较于非开关电容的比率,它是由电路耦合和非开关电路元素形成的,而不是L·di/dt噪声。I/O缓冲区的开关能够带来很大的衬底噪声,增加了核心数字模块开关的噪声。

因此,电源噪声和衬底噪声是密切相关的。随着电源噪声越来越突出,衬底噪声也增加了,这暗示着电源噪声抑制会导致衬底噪声的减少。

路径以及延迟单元和电源噪声

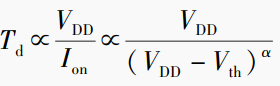

随着技术发展和电源电压的减小,过载电压VDD-Vth减小,这使得门延迟变得对电源电压越来越敏感。通常,延迟Td和电源电压VDD之间的关系是

式中,Ion是开启电流;Vth是阈值电压;α是载流子速度饱和系数。式表明随着电源电压接近阈值电压,延迟迅速增大。因此,电源噪声对时序的影响可望变成一个非常严重的问题,尤其是当电源电压下降的时候。

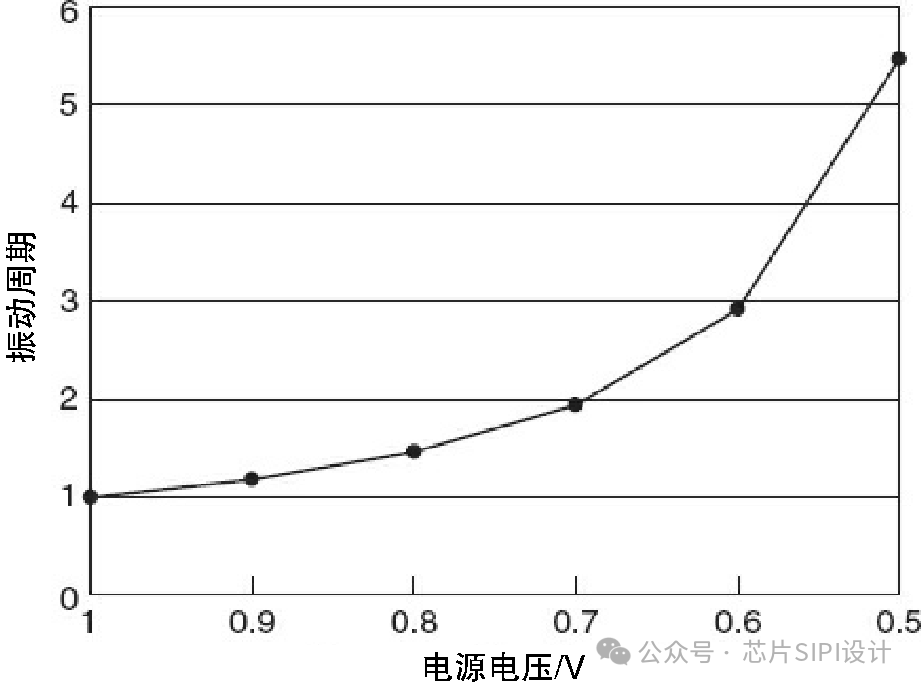

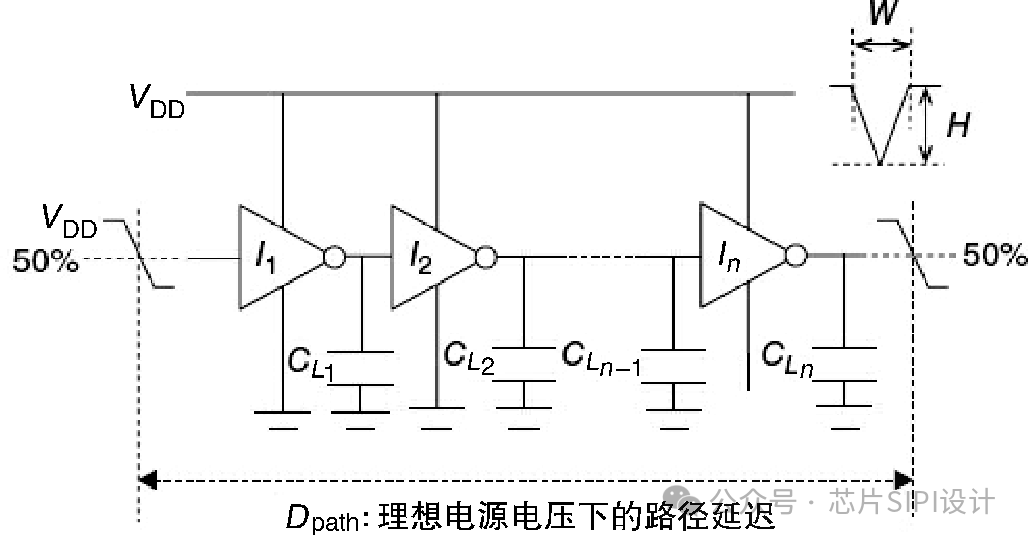

下图显示了电源电压和震荡周期之间的关系。这里,环形振荡器的周期,90nm标准单元库中包含9个逆变器,图展示了电源电压低于1. 0V时振荡的周期时间,可视为电路延迟,随着电源电压的增加呈现线性增长。对于低电压设计,电源噪声是性能下降的主要因素之一。

路径延迟和电源噪声之间的关系

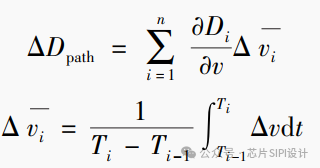

在芯片设计流程中,一个循环周期内的平均电压,即静态IR降,通常计算检查芯片上的布线是否足够提供直流电流,因为它的计算比瞬态噪声分析简单多了。静态IR降通常注释为静态时序分析,因为它的注释和门延迟计算是比较容易的,然而它的电源噪声的动态特性不容易估算。由于PG噪声ΔDpath引起的路径延迟波动,通过每个例子中的电压延迟敏感性的式子表示:

基于时序的平均电源电压分析对于建立时间来说是可行的方法,考虑到数字电路对积分噪声更敏感相比较确切的噪声幅度或者波形。

噪声的下降,是由电流和功率输出网络过滤阶段之间的共振相互作用引起的,因此可能合理地估计半高宽(FWHM),是指吸收谱带高度最大处高度为一半时谱带的全宽,也即峰值高度一半时的透射峰宽度。FWHM 是基于简单倒三角形的面积近似整合下垂的远足。

上式不适用于短路径延迟,它通常用于检查保持约束,因为积分的时间间隔完全不同于循环周期。更重要的是,在这种情况下,静态噪声电压不可用来估测时间波动。例如,大延迟缓存器故意插入高速时钟线以调整相位相对于外部信号时序。通常情况下,大的延迟缓存器往往对电压有更高的延迟敏感度。当使用多个Vth单元时这个问题会加重。如果插入的缓冲器与路径中其他部件敏感性差别很大,由于噪声将会导致时序故障。随着技术缩放灵敏度变得更高。为了预测和防止时序故障,时序分析中动态电压降的问题已经变成设计中不可或缺的一部分。

组合单元延迟

组合单元的传播延时特点是事先使用电路仿真器并存储在标准单元库。对于电源电压角, 每个单元角都有各自的电压显示。当单元延迟是一个中间电压时,就要使用插值。当所有单元电源电压相同且暂时恒定时该方法十分有效,并且地电平是固定的。这种情况有时候是正确的,但是多数情况下并非如此。

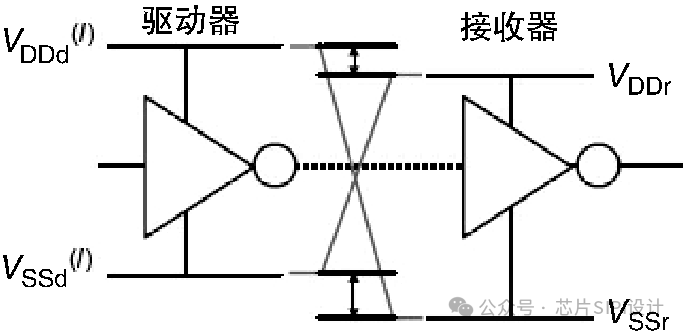

第一个方面是驱动器和接收器之间电源和地的不匹配。上面的方法假设了驱动器和接收器的地电平是相同的。当驱动端和接收端都被放置在给定的电源附近时是正确的。然而,当它们被放置的很远时,因为电源/地(PG)电平在空间内变化,地电平和电源电平变得不同。下图说明了不匹配的问题:VDDr/VSSr是接收端的电源/地电压比例。相似的,V(DlD)d /V(SSl)d是驱动端的电源/地电压比例。图种在接收端只有一个扇入,但是通常有多个驱动门。即使非开关型输入改变了接收端的传输延迟的电压水平,因为充电/放电电流依赖于它们。

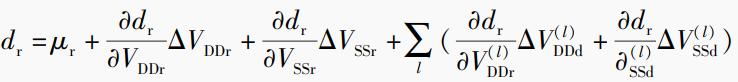

一种处理不匹配问题的可能的方法是使用门延迟模型,该模型是由使用灵敏度的一阶扩张导出的。接收端门延迟dr的表达式是基于敏感度模型中的一个。

这里的μr是当电压值不变时的延迟。上式右边的第二项和第三项符合由于接收端电压变化引起的延迟变化。后面几项符合由于驱动端电压变化引起的延迟变化。在多输入单元, 有很多输入。稳定(非开关)的电压输入影响了传输延迟,因此关于驱动端所有电压变化的项都包含在内。只要电压值变化不大,该方法就是合理的。

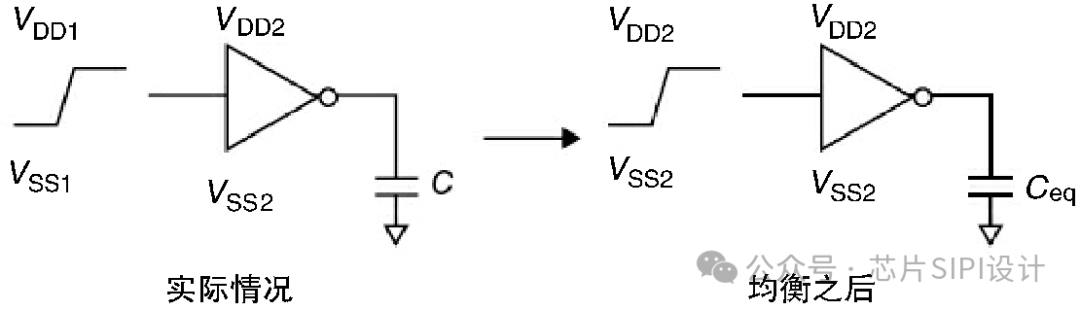

另一种方法,叫做PG级均衡,该方法旨在当保持鉴定成本最小时覆盖更大范围的电压值变化。下图说明了PG级均衡的概念。PG级的输入波形被设置为VDD2和VSS2。PG级均衡是由输出负载的调整完成补偿的。该方法计算了等效输出负载Ceq,用Ceq代替 Cactual。当满足关系Iactual:Ieq=Cactual∶Ceq时门延迟不变,这里的Iactual是实际充电/放电电流, 是PG级均衡之后的充电/放电电流。均衡之后,时序分析基本与传统方法相同。因为延迟依赖于VD(= VDD2-VSS2)通常在库里做好准备,因此其与传统静态时序分析(STA)框架兼容。

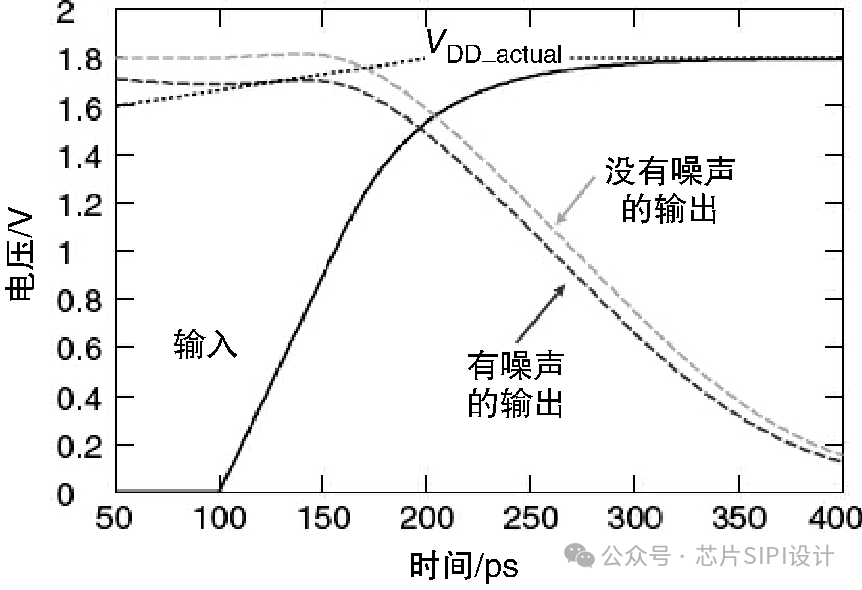

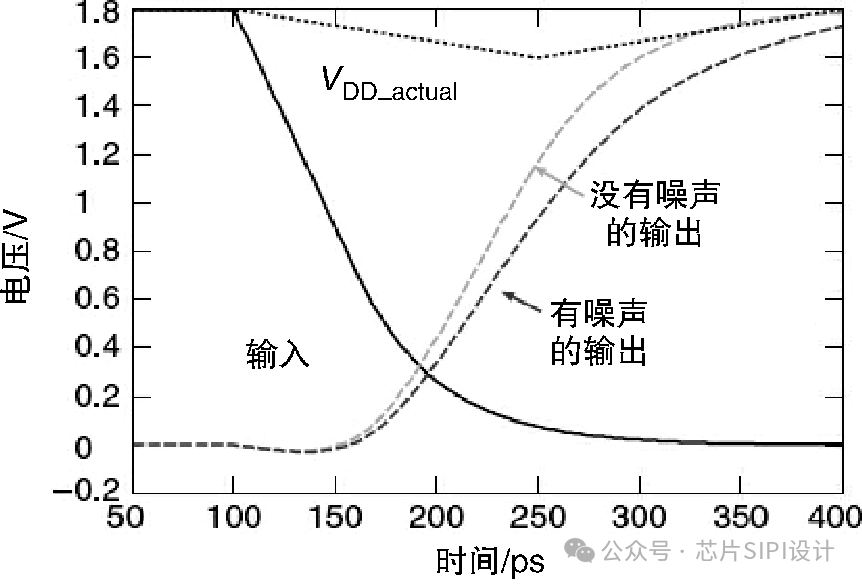

传统分析的另一个问题是暂时的电压变化,这时持续时间陡峭的电源电压的变化类似于门传输延迟,该问题不包含在内。下俩图指出有两种能改变VDD传播延迟的机制。这里, 在180nm工艺中供给反相器三角形功率或者地噪声,估测了输出波形。

下图显示了有电源噪声和没有电源噪声时的过渡波形。在这种情况下,有噪声和没有噪声的50-50百分比传输延迟分别是122ps和132ps。有噪声的延迟比没有噪声的延迟缩短了8% 。因为电源噪声在输入转变刚开始就注入了,当输入转变开始时输出电压低于VDD。电荷量必须通过NMOS放电以变得更少(门输出的电压水平跟随电源电压)当输入门驱动保持在更高的电源水平时,因此传播延迟变得更短。

另外一个例子如下图所示,电源噪声注入对输出转变产生一个上升的变化。在这种情况下,电源噪声降低了PMOS的充电能力,这是因为PMOS栅源电压Vgs改变了。传播延迟从81ps增加到97ps,增长了20%。这些例子说明需要考虑电源噪声的时间特性。

为了方便的考虑时间噪声,一种叫做等效电源/地电压的方法用于处理噪声对时间的高灵敏度。该方法用等效的电源/地电压替代当时的电源/地噪声,使得传播延迟等效于原来的噪声延迟。这种替代使得电源/地噪声转变成单一参数的电源/地电压,需要考虑的参数数量减少了。

触发器时间特性

当设计数字电路时,触发器或二进制状态存储单元的时序特性对于满足时间规范是至关重要的。

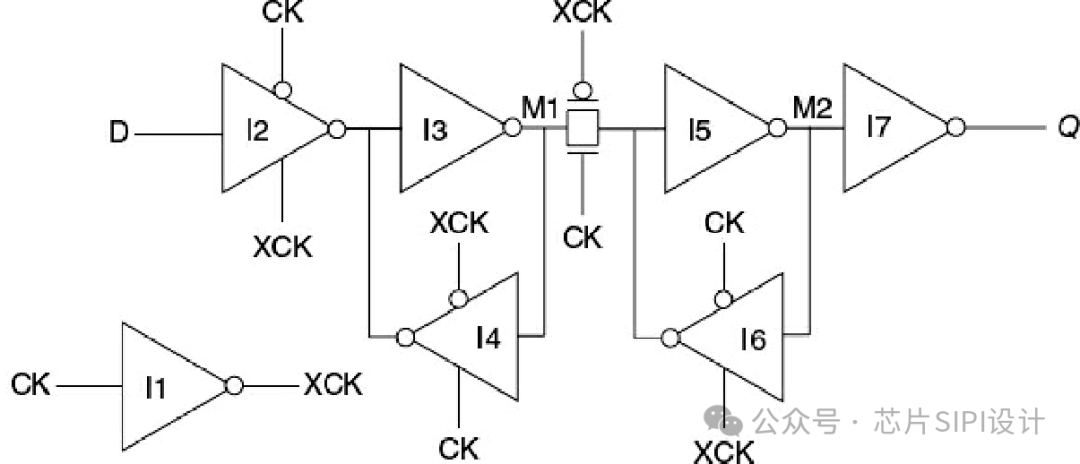

下图展示了一个正边沿触发器的电路图。该单元有一个时钟信号输入端CK,一个数字输入端 D,一个输出端Q。当CK信号为低电平时,由I2和I3组成的信号通路将内部节点 M1的值更新到给定的输入信号D,由I5和I6组成的从锁存器输出内部存储值为Q。当CK 信号为高电平时,I2失效,储存在由I3和I4组成的主锁存器通过I5和I7输出到Q。

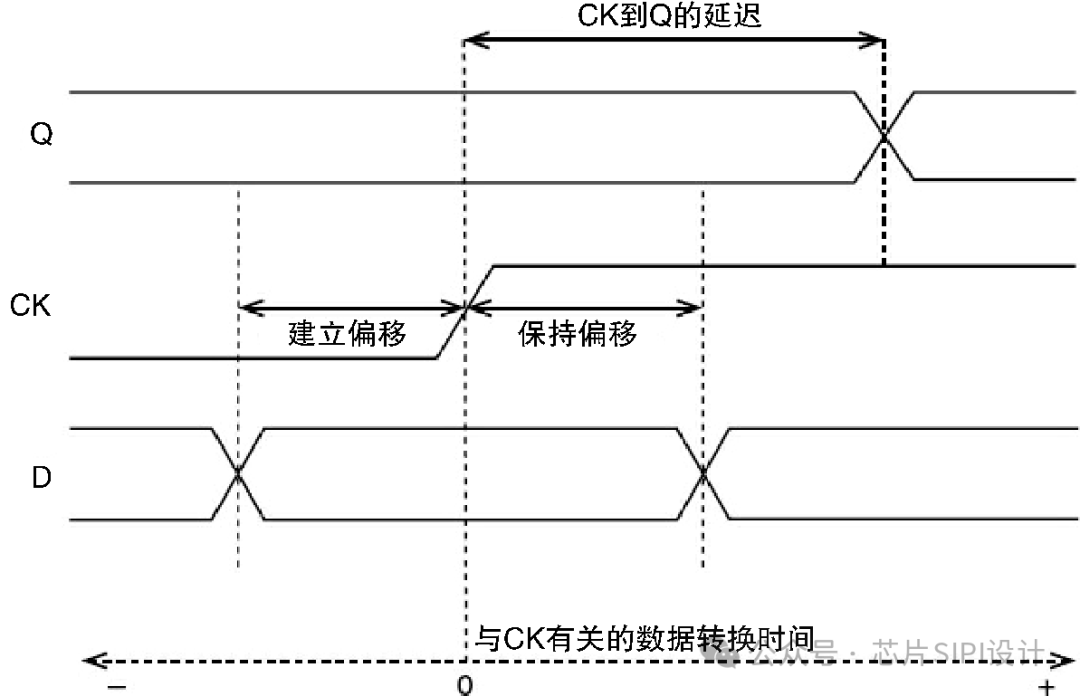

下图说明了建立时间和保持时间之间的关系。建立偏移被定义为D和CK之间到达时间差,保持偏移被定义为CK和D之间到达时间差。建立偏移和保持偏移分别被定义为一个给定的数据信号在获取时钟边缘之前,以及获取时钟边缘之后必须保持稳定的时间量。建立时间和保持时间通常是独立地作为建立偏移和保持偏移以便CK到D增加的延迟能够保持在一定的比例(10% )。以后,延迟增加的允许值被称为CK到Q的退化标准。

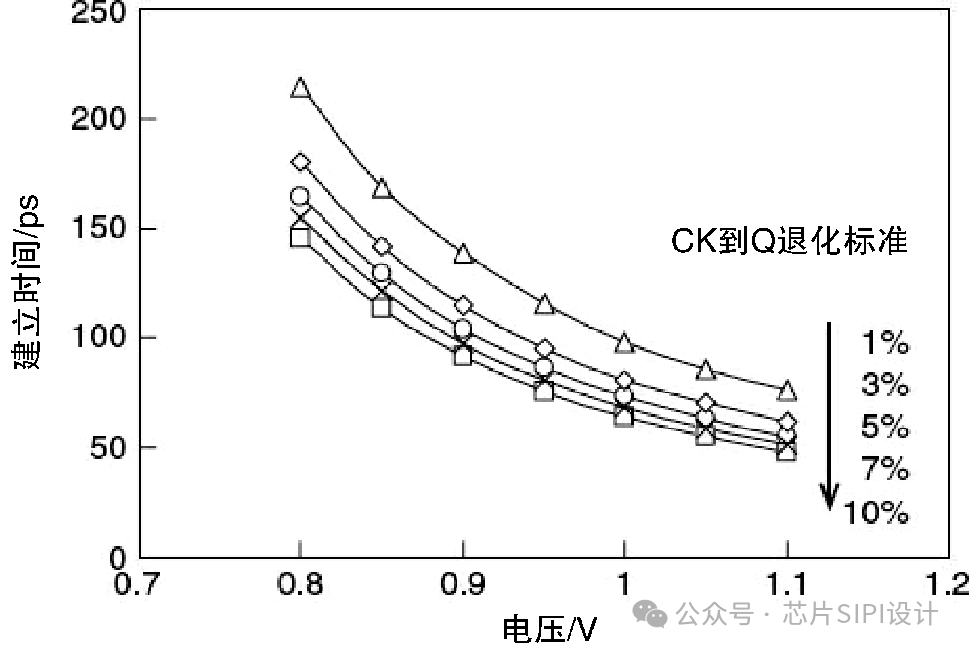

下图描述了在不同的CK到D劣化标准下,建立时间对电源电压的依赖性。图显示建立时间对电源电压十分敏感,且当电源电压从1V下降到0.8V时,建立时间增大了2~3倍。观察到的趋势独立于CK到Q退化标准。从而,额定电源电压下的建立时间是最没有约束的。因此,建立时间对电源电压的依赖性需要仔细考虑,必须给静态时序分析提供一个适当的建立时间。

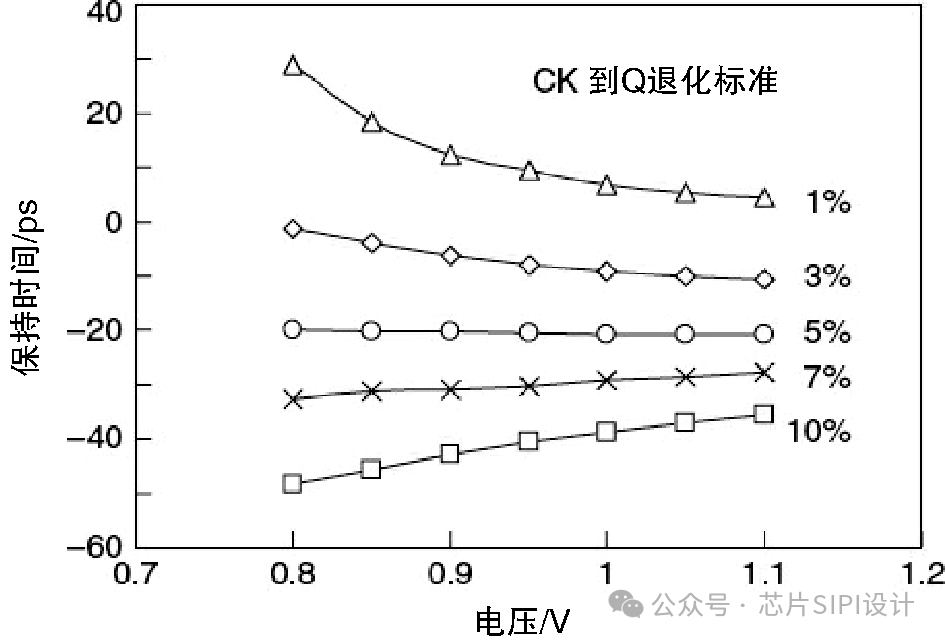

下图展示了在不同的CK到Q退化标准下保持时间对电源电压依赖性。当CK到Q退化标准为1%,当电源电压很低时,保持时间是正的且随着I1延迟的增加变大,这与之前的介绍是一致的。然而,随着CK到Q退化5%的标准,保持时间对电源电压不敏感,超过5%相反,这意味着随着电源电压的下降保持时间变大。

在CK到Q退化标准分别是7%和10%的情况下,不完整的存储在主锁存器在CK捕捉边缘是可接受的,只要额外的时间需要稳定存储值在CK到Q退化标准下。假设I1的级延迟不够大以主宰CK到Q的延迟在典型范围(5%到10%)。在这种情况下,保持时间可以解释为允许主锁存器在捕捉时间边缘之前稳定所需的时间,这时保持时间是负的。

这里的关键点在于允许延迟下降的数量能够在要求的时间内消耗以使主锁存器稳定, 这导致保持时间限制变宽。当电源电压变低时,CK到Q的延迟增加,这意味着CK到Q下降范围的绝对值增加。因此,额外的时间用于稳定主锁存器是可行的。这就是随着电源电压的下降保持时间松弛的原因。

校正保持时间低于动态电压降乍一看似乎不是很重要,因为在额定电源电压(这里是 1V)下的保持时间不一定是悲观的;另一方面,触发器特性一般与CK到Q工业上5%到10% 的退化标准有关。在这个范围内,额定电压下的保持时间达到上限,因为由于电源电压引起的保持时间的变化是很小的。因此,我们可得出额定电压下的保持时间适合静态时序分析。额定电压下的保持时间是,在大多数情况下,静态时序分析的目的足够的悲观;另一方面,建立时间必须在低功耗差分电压悲观值下预测。

2729

2729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?