转载于:http://blog.csdn.net/gtkknd/article/details/25437519

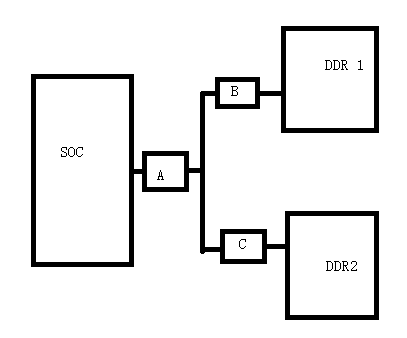

如图所示,以ARM,DSP等SOC为核心的电子系统中,经常存在两片或者以上的DDR/DDRII SDRAM。考虑到DDR/DDRII SDRAM的运行频率一般都比较高,在做PCB layout的时候需要等长布线来保证DDR/DDRII SDRAM的读写时序。对于包含两片及以上DDR/DDRII SDRAM的系统,这里要求的等长布线有两层含义。拿ADDRESS信号来讲,第一层含义要求从SOC的某一个ADDRESS的pad到每一块儿DDR/DDRII SDRAM对应的pad之间的长度要相等(A+B = A+C),第二层含义要求SOC的所有ADDRESS的pad到对应DDR/DDRII SDRAM的pad之间的长度要相等(所有的A+B = 所有的A+C)。

但在Altium Designer中,SOC的某一ADDRESS pad与对应DDR/DDRII SDRAM的pad之间的网络定义是唯一的(也就是A,B,C拥有同样的网络名称),网络的长度定义为(A+B+C),无法准确知道A,B和C的长度。那如何在Altium Designer中实现DDR/DDRII SDRAM的等长布线呢?

下面以一个项目中DRAM_A0 ~ A3四根信号线的等长设计为例,介绍在Altium Designer中实现DDRII SDRAM的等长布线。U23为CPU,U7和U8为两片DDRII SDRAM。DRAM_A0 ~ A3为低四位地址信号。

但在Altium Designer中,SOC的某一ADDRESS pad与对应DDR/DDRII SDRAM的pad之间的网络定义是唯一的(也就是A,B,C拥有同样的网络名称),网络的长度定义为(A+B+C),无法准确知道A,B和C的长度。那如何在Altium Designer中实现DDR/DDRII SDRAM的等长布线呢?

下面以一个项目中DRAM_A0 ~ A3四根信号线的等长设计为例,介绍在Altium Designer中实现DDRII SDRAM的等长布线。U23为CPU,U7和U8为两片DDRII SDRAM。DRAM_A0 ~ A3为低四位地址信号。

转载于:http://blog.csdn.net/gtkknd/article/details/25437519如图所示,以ARM,DSP等SOC为核心的电子系统中,经常存在两片或者以上的DDR/DDRII SDRAM。考虑到DDR/DDRII SDRAM的运行频率一般都比较高,在做PCBlayout的时候需要等长布线来保证DDR/DDRII SDRAM的读写时序。对于包含...

转载于:http://blog.csdn.net/gtkknd/article/details/25437519如图所示,以ARM,DSP等SOC为核心的电子系统中,经常存在两片或者以上的DDR/DDRII SDRAM。考虑到DDR/DDRII SDRAM的运行频率一般都比较高,在做PCBlayout的时候需要等长布线来保证DDR/DDRII SDRAM的读写时序。对于包含...

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2536

2536

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?