DDR等 布线/走线需要等长的原因

DDR所最遵守的规范为JEDEC相关的技术标准,如下所示:例如DDR的JEDEC对应的标准为JESD79E;该标准规定了相对应版本DDR需要的一些技术标准,使得各个半导体厂商遵从该标准进而开发DDR产品。

JEDEC标准与DDR版本:

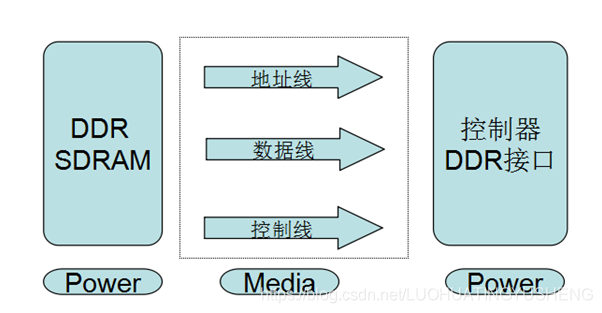

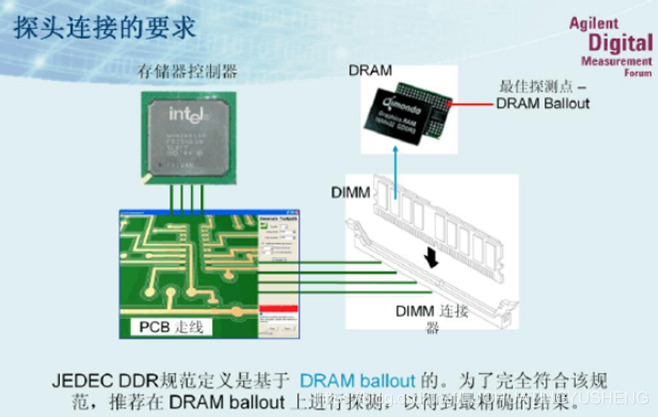

DDR与控制器之间的连接

DDR与控制器实际连接:

DDR实际上我们注意的一些参数,而改参数的指标受到以下指标的影响:

1、DDR器件本身;大部分我们认为DDR设备为“终端”;

2、DDR和控制器之间的连线;该介质主要是PCB板上的铜线;

3、控制器的接口。我们认为此部分为“源端”。

终端和源端简单理解就是“我给你东西,我就是源端,你就是终端”。也就是说地址信号和控制信号是CPU给DDR的,所以CPU是源端设备,而DDR是终端设备;当然数据线虽然是双向的,似乎很难区分,但是请注意数据的有效性是受控制信号控制的,所以不要纠结这个问题。

而最终的测试是需要测试的整个系统的合理性,该系统的合理性直接影响DDR电气参数指标与信号质量;合理性越高,则信号质量等越好。合理性越差,将会导致信号完整性出现问题,并且最严重的会导致系统出现故障。

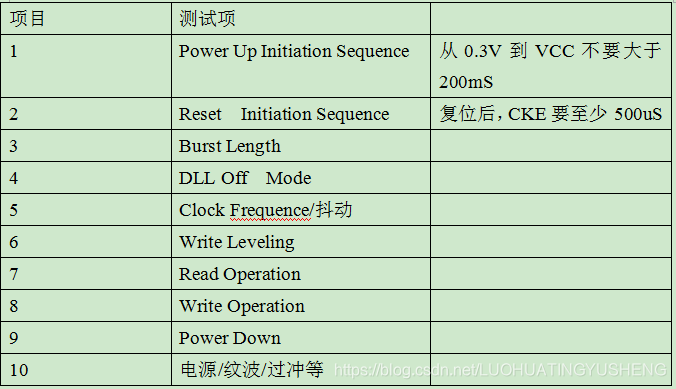

JEDEC标准规范了DDR相关的电气参数,而我们的目标是达到规定的电气参数指标。为此,当我们完成相关系统设计时,需要进行测试验证,来检验是否达到规范标准需求,达到标准说明该系统可以可靠地工作。JEDEC测试的参数项一般如下:

包含电气性能与信号质量:

项目 测试项

1 Power Up Initiation Sequence 从0.3V到VCC不要大于200mS

2 Reset Initiation Sequence 复位后,CKE要至少500uS

3 Burst Length

4 DLL Off Mode

5 Clock Frequence/抖动

6 Write Leveling

7 Read Operation

8 Write Operation

9 Power Down

10 电源/纹波/过冲等

其中最为重要的就是信号的完整性,信号完整性保证其时序的准确性以及各时间余量的充足,特别是建立时间和保持时间。

如下可参考:

https://max.book118.com/html/2018/0913/6031123213001215.shtm

http://www.doc88.com/p-1746977884652.html

为什么需要等长?

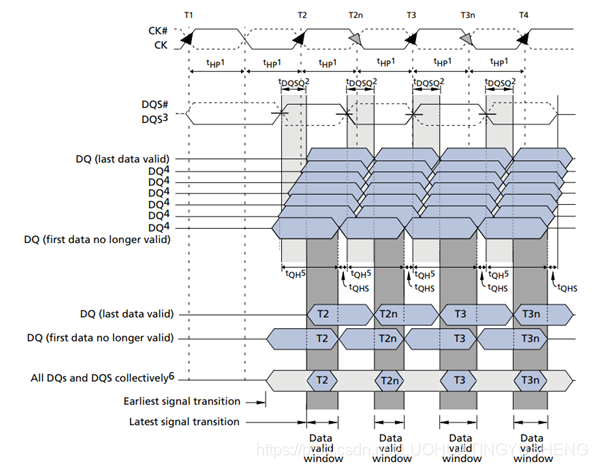

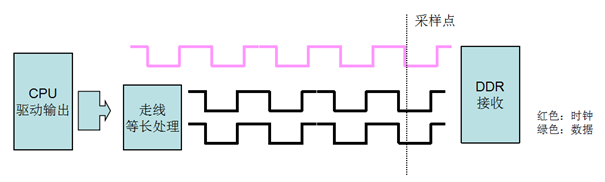

如下为数据操作的有效时序窗口,在满足如下时序要求时,数据才能正确的被读取,而不会发生错误。

如上图所示,假如16条数据线做了等长处理,而此时CPU的驱动强度一致,走线等长和阻抗一致,则此时数据传输应该是齐头并进的,这样的话在同一个时钟下到达DDR端的数据采样点是一致的。

如下图所示:

如上如果走线一致,长度相等,在同一时钟下,所以在时钟采样点处数据读到的为“00”,仅做说明,正常为16位。

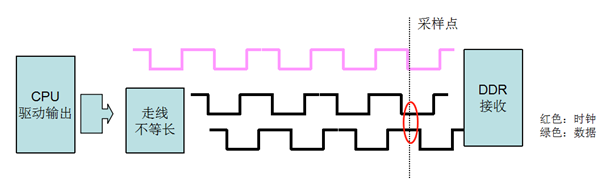

走线不等长?

可是一旦不等长处理,则可能导致如下问题:

还是和上面一样的数据传输,但是走线未经过等长处理,所以在实际传输中包含传输时间和延迟时间,因为没有做等长处理,则实际的长走线将需要更多的传输时间和多出来的延迟时间,此时就会出现上面的情况,在同一个采样点,由于延迟,长的走线数据由“0变为1”,而整个数据变为了“01”,此时传输的数据改变,发生数据错误问题。

走线等长,但是允许存在误差?

随着并行总线信号速率的不断提高,时序越来越紧张,为了缓解这一问题,DDR总线穿心行的引入了斜率补偿技术,而这一技术在DDR2器件上得到了进一步的发展。

DDR2的边沿斜率补偿技术的基本原理是动态调整输入的简历和保持时序参数,获得较大的时序余量。例如,当接受的数据信号相对于始终信号的边沿变缓时,数据时序窗口变小,系统会自动减小输入建立与保持时间的要求,使时序裕量变大。

1、当时钟信号斜率不变,地址/控制信号边沿变缓时,器件的建立和保持时间需求变小。

2、当时钟信号斜率不变,地址/控制信号边沿变陡时,器件的建立和保持时间需求变大。

3、当地址/控制信号斜率不变,时钟信号边沿变缓时,器件的建立和保持时间需求变大。

4、当地址/控制信号斜率不变,时钟信号边沿变陡时,器件的建立和保持时间需求变小。

正是由于上面的技术,我们在做等长控制时允许误差的存在,有时超过误差允许值但是还可以工作,并不是他们的允许值不对,而是厂商将该值裕量调小,使得客户设计时严格一些,这样才不会处于临界出错的地步。

以下请参考:

http://www.doc88.com/p-045804373776.html

所以,其他类型的走线等长处理原则的原因也差不多,类似于DDR的原理。

2976

2976

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?