串行序列检测器

序列检测器经常作为一些集成电路涉及公司的面试题目,为此,本文以一个简单的序列示意该序列检测器的设计实现,对于类似的序列监测器的设计有普适的作用。

【设计说明】

设计一个"10110"串行数据检测器,使得输出序列中出现"10110"时,结果中就输出1,输入/输出示例如下所示:

输入:1011 0101 1001 0100

输出:0000 1000 0100 0000

【设计目的】

1.用状态机实现序列检测器的设计;

2.了解一般状态机的设计与应用;

【设计思路】

序列检测器是一种同步时序电路,它用于搜索、检测输入的二进制代码串中是否出现指定

的代码序列。当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出为1,否则输出为0.由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。在检测过程中,任何一位不相等都将回到初始状态重新检测。

【设计分析】

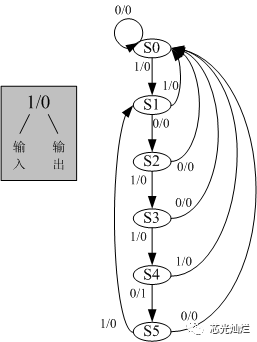

初始状态设为s0,此时检测数据序列为“0”,当再检测到一个0时,仍为s0,当检测到1时,进入下一个状态s1,此时序列为“1”;当在状态s1检测到0时,进入到状态s2,此时序列为“10”,当检测到1时,跳回s0;当在状态s2检测到1时,进入到状态s3,此时序列为“101”,当检测到0时,进入s0;当在状态s3检测到1时,进入s4,当检测到0时,进入状态s0,此时序列为“1011”;当在s4检测到0时,当检测到0时,进入状态s5同时输出1,当检测到1时,进入状态s0。状态图如下:

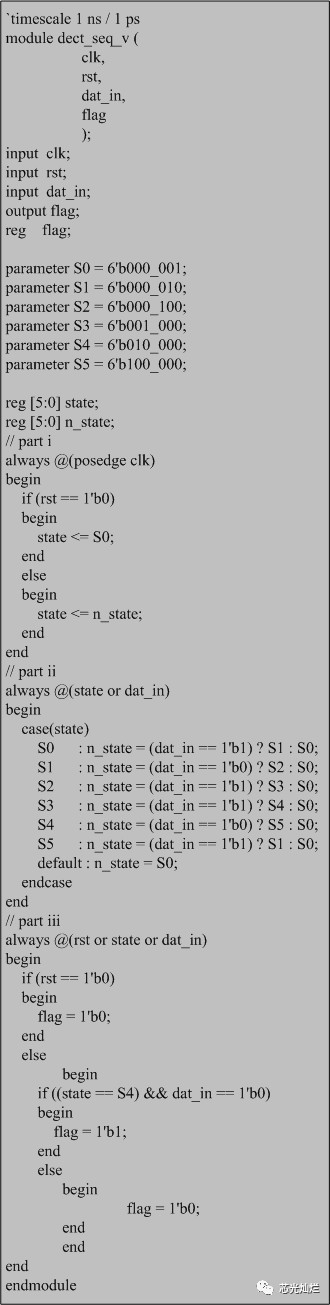

【源代码】

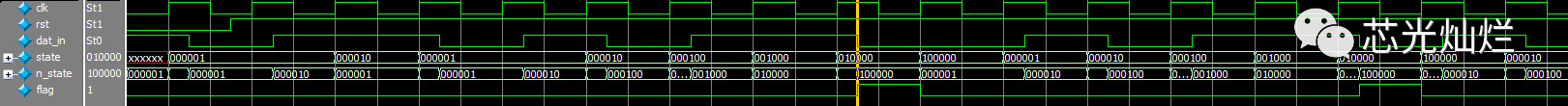

【仿真结果】

【进阶思考】

1.可利用序列检测器设计简易数字密码锁。

2.可考虑给本实验设计出的序列检测器去除毛刺。

3137

3137

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?