大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

今天给大侠带来基于FPGA的千兆以太网设计,话不多说,上货。

一、设计概述

由于设计比较复杂,本篇带来设计流程以及设计思路,仅供各位大侠参考。

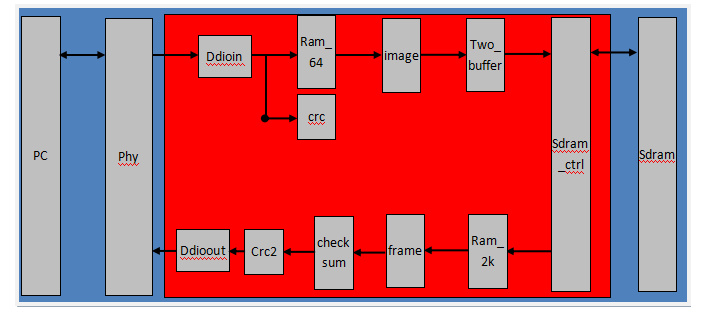

本篇通过管理数据输入输出MDIO配置PHY寄存器,使其工作在千兆通信模式下。FPGA通过ddio_out的IP核将数据单沿转双沿通过TX发送到PHY-A,PHY—B把收到的数据RX通过ddio_in的IP核双沿转单沿给FPGA采集,实现FPGA与PHY的交互通信。通过FPGA的SDRAM控制模块对SDRAM进行读写和刷新的操作,从而进行数据的存储与读取的操作。

根据UDP/IP协议将数据打包,并且通过IP源地址以及目的地址等来计算IP头部checksum和UDP头部checksum,在PC机上通过上位机软件Wireshark获取FPGA发送的1024byte的数据包,并且上位机显示通过UDP协议接收数据,数据位打包时加上CRC32冗余校验码,在FPGA的接收端可以加上CRC32解码操作,用来验证数据在传输过程中是否出错。

二、设计框架

整体模块比较复杂,自顶向下设计流程,分模块较多,需要注意各个端口信号,最好可以做成端口信号表,以免自己搞混淆。

注:复位省略,_t后缀表示数据或标志信号经过一级寄存器打拍操作。输入时钟25M,PLL倍频输出sclk125M,tx_data是偏移90度125M时钟。

三、数据流框图描述

四、DDIO模块简单描述

DDIO模块描述:

1、DDIO为调用的FPGA内部IP核;

2、ddioin是将双沿数转为单沿数据,ddioout是将单沿数据转化双沿数据。

ddioin时序图:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9959

9959

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?