真空管的发明是电子工业发展的重要动力。但是,在第二次世界大战之后,由于需要大量的分立元件,设备的复杂性和功耗显着增加,而设备的性能却不断下降,其中一个例子是波音B-29,由300~1000个真空管组成。每个附加组件会降低系统可靠性并增加故障排除时间。

1947年出现了一个重大突破,它来自于贝尔实验室的John Baden,William Shockley和Watter Brattain,他们发明了锗晶体管。1950年,Shockley开发了第一个双极结晶体管(BJT)。与真空管相比,晶体管更可靠,功效高,尺寸更小。

1958年,德州仪器的杰克·基尔比(Jack Kilby)搭建了第一个集成电路,由两个双极晶体管组成,该晶体管连接在单片硅片上,从而启动了“硅时代”。

早期IC使用双极晶体管。由于有更多的静态功耗,BJT的这一缺点是个老大难问题。这意味着即使在电路没有打开的情况下也会产生电流。这限制了可以集成到单个硅芯片中的晶体管的数量。

1963年,飞兆半导体的Frank Wanlass和CTSah公布了第一个逻辑门,其中n沟道和p沟道晶体管用于互补对称电路配置。这就是今天所谓的CMOS。它的静态功耗几乎为零。

在接下来的几年中,CMOS制程的改进使得电路速度不断提高,芯片的封装密度和性价比进一步改进。

下面,我们会讨论Bulk-Si CMOS技术、SOI和FinFET,以及相关的解决方案。我们还讨论晶体管材料的物理尺寸限制,以及高级技术节点中使用的新材料。

MOSFET概述

在这里,我们首先讨论CMOS的核心单元,即MOSFET或简单MOS的基本结构和重要的术语。

MOS结构

根据通道类型,MOS主要分为两种结构:n沟道和p沟道MOS。在这里,我们将仅概述NMOS晶体管。

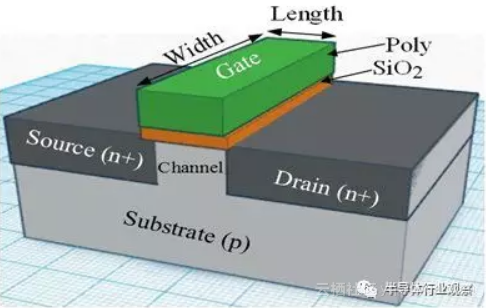

MOS晶体管是具有漏极、源极、栅极和衬底的4端子器件。图1显示了NMOS的3维结构。NMOS晶体管形成在p型硅衬底(也称为本体)上。在器件的顶部中心部分,形成一个低电阻率的电极,它通过一个绝缘体与本体分开。通常,使用n型或p型重掺杂的多晶硅作为栅极材料。这里,使用二氧化硅(SiO 2或简单的氧化物)作为绝缘体。通过将供体杂质植入基板的两侧,形成源极和漏极。在图1中,这些区域由n +表示,表示供体杂质的重掺杂。这种重掺杂导致这些区域的低电阻率。

如果两个n +区被偏置在不同的电位,则处于较低电位的n +区将作为源,而另一个将作为漏极。因此,漏极和源极端子可以根据施加到它们的电位进行互换。源极和漏极之间的区域称为具有宽度-W和长度-L的沟道,其在决定MOS晶体管的特性中起重要作用。

图1. NMOS晶体管的结构

为何用多晶硅作为栅极材料?

在半导体工业的早期,金属铝通常被用作MOS的首选栅极材料。但是后来,多晶硅被选为栅极材料。这主要出于两方面的考虑。

早期的MOS制造过程始于源和漏区域的定义和掺杂。然后,使用限定形成铝金属栅极的栅极氧化物区域的栅极掩模。

这种制造工艺的主要缺点之一是:如果栅极掩模未对准,则其产生寄生重叠输入电容C gd和C gs,电容C gd因为反馈电容而更为有害。作为铣刀电容的结果,晶体管的切换速度降低。

选择多晶硅的另一个原因是MOS晶体管的阈值电压与栅极和沟道之间的功函数差异相关。此前,当工作电压在3~5V范围内时,使用金属栅极。但是,随着晶体管的缩小,这确保了器件的工作电压也降低了。具有这种高阈值电压的晶体管在这种条件下变得不可操作。使用金属作为栅极材料导致与多晶硅相比更高的阈值电压,因为多晶硅将具有与体Si沟道相同或相似的组成。此外,由于多晶硅是半导体,因此其功函数可以通过调整掺杂水平进行调制。

技术不断演进

市场对电池供电的便携式电子产品的需求日益增加,包括助听器、手机、笔记本电脑等,这种应用的功耗更低,开发更便宜。对于这种便携式设备,功率消耗是重要指标,因为电池提供的功率相当有限。不幸的是,电池技术不能期望每5年将电池存储容量提高30%以上。这不足以应对便携式设备中增加的功耗。

1965年,戈登·摩尔(Gordon E. Moore)预测,集成电路中的晶体管数量将会每两年翻一番(广为人知的摩尔定律)。通过使晶体管更小,可以在硅晶片上制造更多的电路,因此电路变得更便宜。通道长度的减小可以实现更快的开关操作,因为电流从漏极流到源极需要更少的时间。

对于长通道器件,通道四边的“边缘效应”真的可以忽略不计。对于长通道器件,电场线垂直于通道的表面。这些电场由栅极电压和背栅极电压控制。但是,对于短通道器件,漏极和源极结构更靠近通道,特别是当通道中的纵向电场进入时。纵向电场由漏源电压控制。纵向电场平行于电流流动方向。如果通道长度不大于源极和漏极耗尽宽度的总和,则该器件称为短沟道器件。

由于短通道中二维电势分布和高电场,会产生各种不良影响。

载波速度饱和度和移动性降级

通道中的电子漂移速度与较低电场值的电场成比例。这些漂移速度往往会在高电场饱和。这称为速度饱和度。对于短通道器件,纵向电场通常也增加。在这样的高电场下,发生影响MOSFET的I-V特性的速度饱和。对于相同的栅极电压,MOSFET的饱和模式在较低的漏 - 源电压值和饱和电流降低的情况下实现。

由于较高的垂直电场,通道的载流子离开氧化物界面。这导致载流子迁移率的降低和漏极电流的降低。

本文深入探讨了半导体工艺技术的发展,从CMOS、FinFET到SOI和GaN工艺,详细阐述了各自的技术特点和优缺点。CMOS工艺在不断演进以应对短通道效应,FinFET提供了更好的栅极控制,而SOI技术则因减少寄生电容和更低功耗受到关注。GaN作为一种新型材料,因其高功率密度和高频性能在微波和毫米波应用中崭露头角。随着技术的推进,半导体行业正在寻找新材料和工艺以应对摩尔定律的挑战。

本文深入探讨了半导体工艺技术的发展,从CMOS、FinFET到SOI和GaN工艺,详细阐述了各自的技术特点和优缺点。CMOS工艺在不断演进以应对短通道效应,FinFET提供了更好的栅极控制,而SOI技术则因减少寄生电容和更低功耗受到关注。GaN作为一种新型材料,因其高功率密度和高频性能在微波和毫米波应用中崭露头角。随着技术的推进,半导体行业正在寻找新材料和工艺以应对摩尔定律的挑战。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?