有两种途径可以实现工艺特征尺寸进入到小于25nm工艺制程:

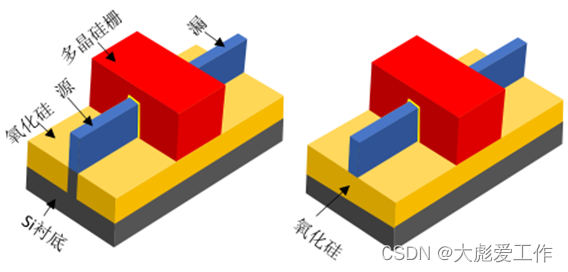

一种是采用三维立体型结构的FinFET晶体管代替平面结构的MOSFET作为集成电路的晶体管。FinFET晶体管凸起的沟道区域是一个被三面栅极包裹的鳍状半导体。沿源-漏方向的鳍与栅重合区域的长度为晶体管沟道长度。

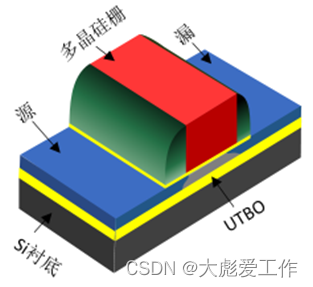

另外一种是基于SOI的超薄绝缘层上的平面硅技术,称为UTB-SOI,也就是FD-SOI晶体管,研究发现要使UTB-SOI正常工作,绝缘层上硅膜的厚度应限制在栅长的四分之一左右。对于25nm栅长的晶体管,UTB-SOI的硅膜厚度应被控制在6nm左右。

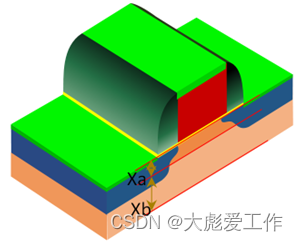

为什么FD-SOI和FinFET要把沟道的厚度制造的很薄,它的原理是什么呢?

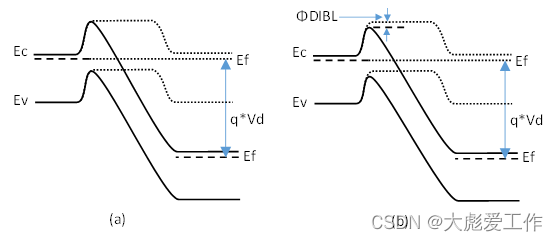

(1)沟道距离栅极Xa≤0.25*Lg的沟道区域的能带图,栅极对该区域的沟道形成有效的控制,漏端的电压Vd不足以导致沟道的势垒高度降低。

(2)距离栅极Xb > 0.25*Lg的沟道区域的能带图,它距离栅极较远,栅极对该区域的沟道形成没有形成有效的控制,由于短沟道效应中DIBL效应导致沟道区域的势垒高度降低了ФDIBL,虽然MOSFET处于关闭状态,但是电子依然很容易越过势垒,在沟道的正下方会形成漏电流。为了有效的抑制短沟道效应,必须设法使沟道中任何的点到栅的距离Xa≤0.25*Lg的范围内。

相关内容

本文介绍了半导体工艺制程中FinFET和FD-SOI技术如何通过减小沟道厚度来提升晶体管性能。FinFET采用三维结构增强栅极控制,而FD-SOI则依赖于超薄绝缘层来抑制短沟道效应。通过控制沟道厚度,这两种技术能够有效抑制漏电流,提高晶体管开关性能,进而推动25nm以下工艺制程的发展。

本文介绍了半导体工艺制程中FinFET和FD-SOI技术如何通过减小沟道厚度来提升晶体管性能。FinFET采用三维结构增强栅极控制,而FD-SOI则依赖于超薄绝缘层来抑制短沟道效应。通过控制沟道厚度,这两种技术能够有效抑制漏电流,提高晶体管开关性能,进而推动25nm以下工艺制程的发展。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?