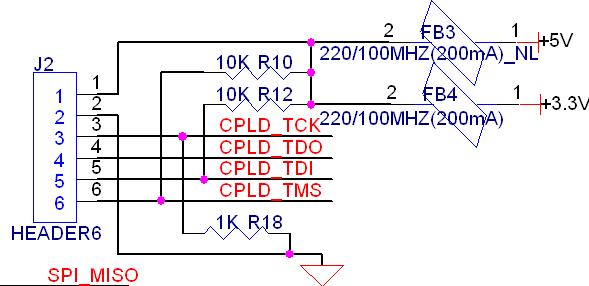

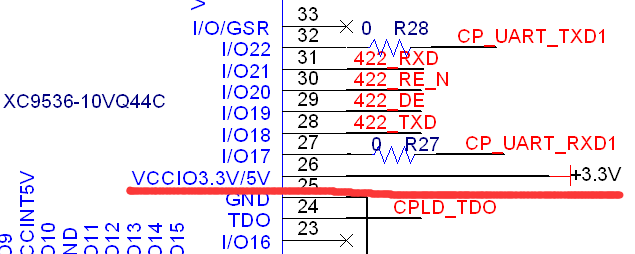

在初次的cpld电路设计的时候,遇到了这样的一个问题,整个系统是3.3V的系统,选用的cpld是XC9536-10VQ44C,芯片供电电压5V。他的io可以配置成3.3V和5V两种形式,因此,选用的时候,io口配置成了3.3V如下图,问题就有了,那在设计jtag的时候,上拉电阻应该上拉到那个电压呢?实验证明,jtag应该上拉到与io口相同的电平上。而上拉到供电电压的现象并不是损坏芯片,而是导致不能正常下载程序,具体到软件上的显示就是不能正确读出”Device IDCODE “。几幅关键的截图如下:

----------------------------------------------------------------------------------------------------------------------------------------------------------------

版权声明:本文为博主原创文章,未经博主允许不得转载。

905

905

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?