对应应届生来说,基本上学完前面三个项目,就可以直接降维吊打其他同学了。从2024年IC秋招就业情况看,只要有211工科相关专业背景,认真来学习做项目,offer自然会找上门来。

数字后端零基础入门系列 | Innovus零基础LAB学习Day10

数字后端教程之Innovus report_property和get_property使用方法及应用案例

十大课程体系

一.基于TSMC 28nm的ARM Cortex-A7数字后端实现

课程简介:主时钟频率:>= 1.1GHz ssg0p81v125c +rcworst125c

设计规模:19万instance

Power Domain数量:1个 (a7core做成一个PD)

Voltage Domain数量:0个

实现方式:模块Block Level的Flatten实现

项目成果:Timing Signoff Timing Clean,DRC,Antenna,LVS clean,IR Drop符合signoff要求

涉及EDA工具:Innovus,Starrc,PrimeTime,Calibre,redhawk

授课形式:录播+直播课+每日问题解答+远程协助。每周直播1次,每次近2小时。

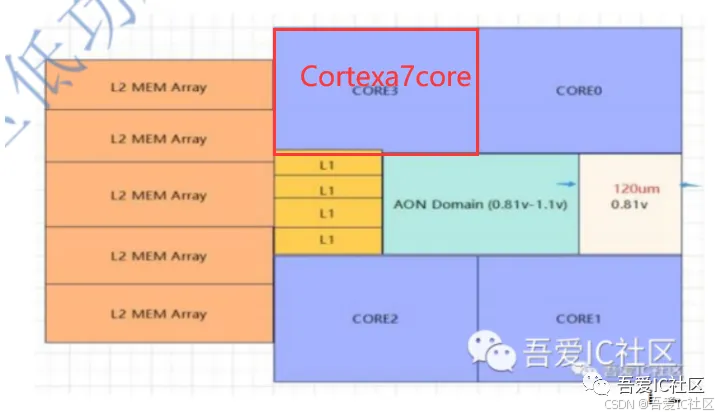

该模块级a7core为整个CPU子系统中的一个CPU处理器,如下图红框所示。

课程特色:

1)真实后端Block Level项目

2)理论结合实操授课方式

3)一线12年后端经验工程师亲自授课(星主本人),毫无保留分享自己做项目的思路和方法4)一对一答疑+远程VNC协助解决问题服务

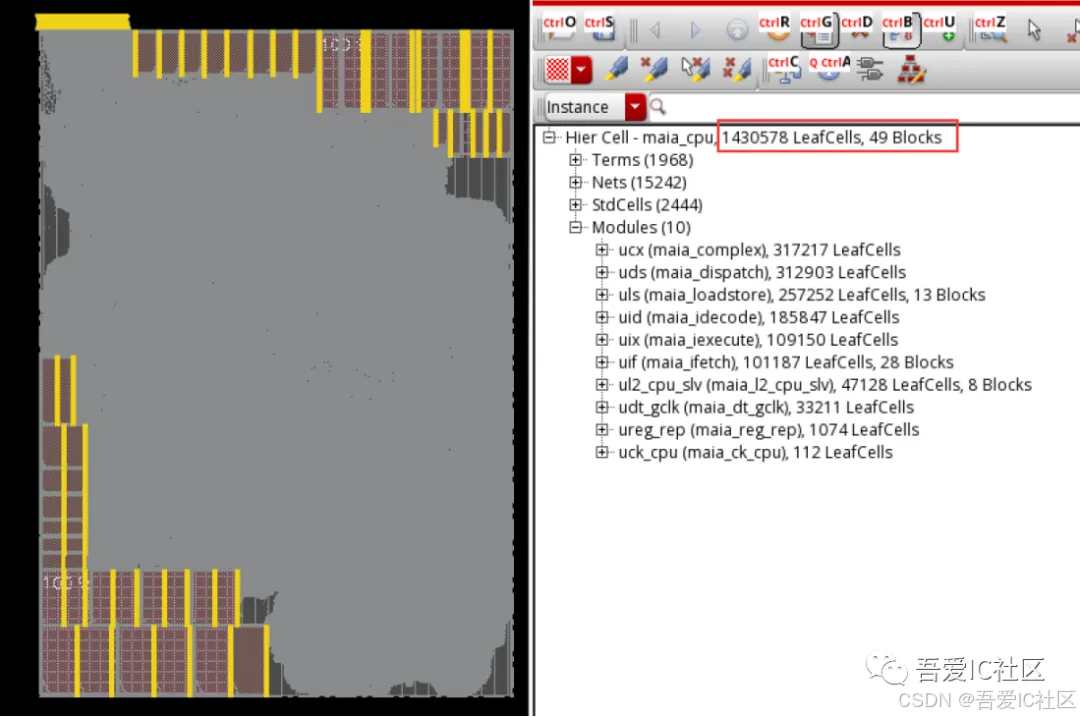

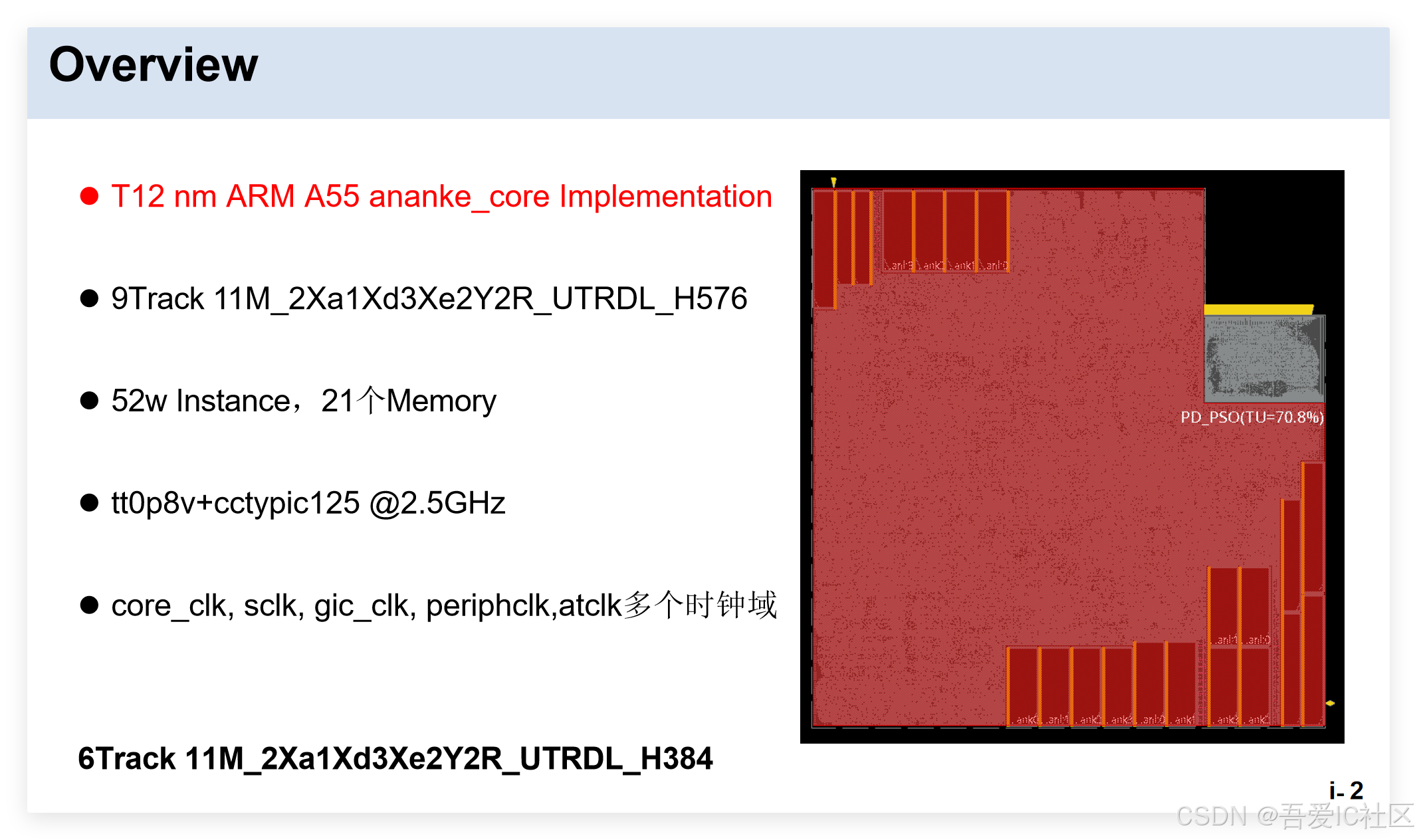

二.基于TSMC 12nm ARM A72 maia_cpu + A55 ananke_core 模块级的物理实现课程

课程简介:主时钟频率:>= 1.2GHz ssg0p81v125c +rcworst125c

设计规模:140万instance

Power Domain数量:1个

Voltage Domain数量:0个

实现方式:模块Block Level的Flatten实现

项目成果:Timing Signoff Timing Clean,DRC,Antenna,LVS clean涉及EDA工具:Innovus,Starrc,PrimeTime,Calibre

授课形式:录播+直播课+每日问题解答+远程协助。每周直播1次,每次近2小时。

课程特色:

1)真实后端Block Level项目

2)Double Pattern工艺

3)理论结合实操授课方式

4)一线12年后端经验工程师亲自授课(星主本人),毫无保留分享自己做项目的思路和方法5)一对一答疑+远程VNC协助解决问题服务

学习周期:视频课程和图文教程都是永久有效。服务器使用时间为2.5个月,一人一账号。

课程工艺和课程项目(一个TSMC28nm项目+一个TSMC12nm项目)

新一期的IC后端训练营将是包含两个工艺,两个不同的项目。即同时包含第一个课程和第二个课程。

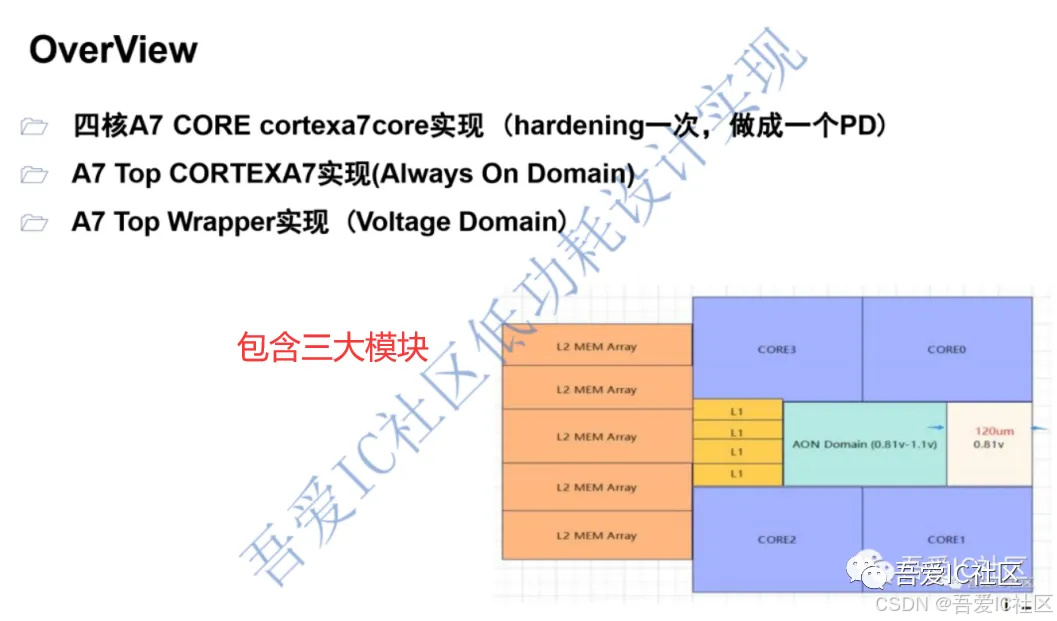

三.基于TSMC 28nm低功耗四核A7 Top Hierarchical Flow物理实现

课程简介:主时钟频率:>= 1.1GHz ssg0p81v125c +rcworst125c

设计规模:110万instance (包含若干个子模块和顶层设计)

Power Domain数量:4个

Voltage Domain数量:2个

实现方式:Hierarchical Flow +Low Power Flow

项目成果:Timing Signoff Timing Clean,DRC,Antenna,LVS clean,Redhawk IR Drop符合Signoff要求涉及EDA工具:Innovus,Starrc,PrimeTime,Calibre和Redhawk

授课形式:直播授课+实践课+每日问题解答+远程协助。

每周直播两次,每次近2小时。理论结合实操,一次理论课,一次实操课。

课程内容:

1)层次化Hierarchical Flow设计实现全流程全面解析Hierarchical Flow和传统Flatten Flow的区别,通过项目实战来诠释Hierarchical Flow同Flatten Flow在数字IC后端实现中的不同做法。

2)低功耗设计理论,熟悉常见低功耗cell(isolation cell,level shifter cell)的用法及其实现经验熟悉数字IC设计实现中所有低功耗技术手段,比如clock gating,power gating,Multi-VT等技术手段。并通过项目实操来掌握常见低功耗cell在数字IC后端实现中的相关技术经验及其checklist检查。比如如何确保isolation cell摆放到合适的power domain,isolation cell的input电气特性,level shifter cell secondary pg连接及secondary pg net的电阻检查等。

3)根据低功耗设计实现需求编写upf验证upf内容根据需求划分power domain,voltage domain,选择合适的isolation cell类型和level shifter cell类型。通过实际后端项目加载upf后进行verifyPowerDomain相关检查。

4)根据顶层release的top floorplan def进行cpu子系统各模块的partition以及pin assignment

5)子模块cortexa7core,A7 top以及A7top_wrapper的floorplan工作

6)整体cpu子系统的powerplan规划及实现(实现模块和顶层PG的allignment)

7)顶层top和CPU接口时序优化

8)顶层TOP isolation cell的placement以及isolation cell input电学特性检查

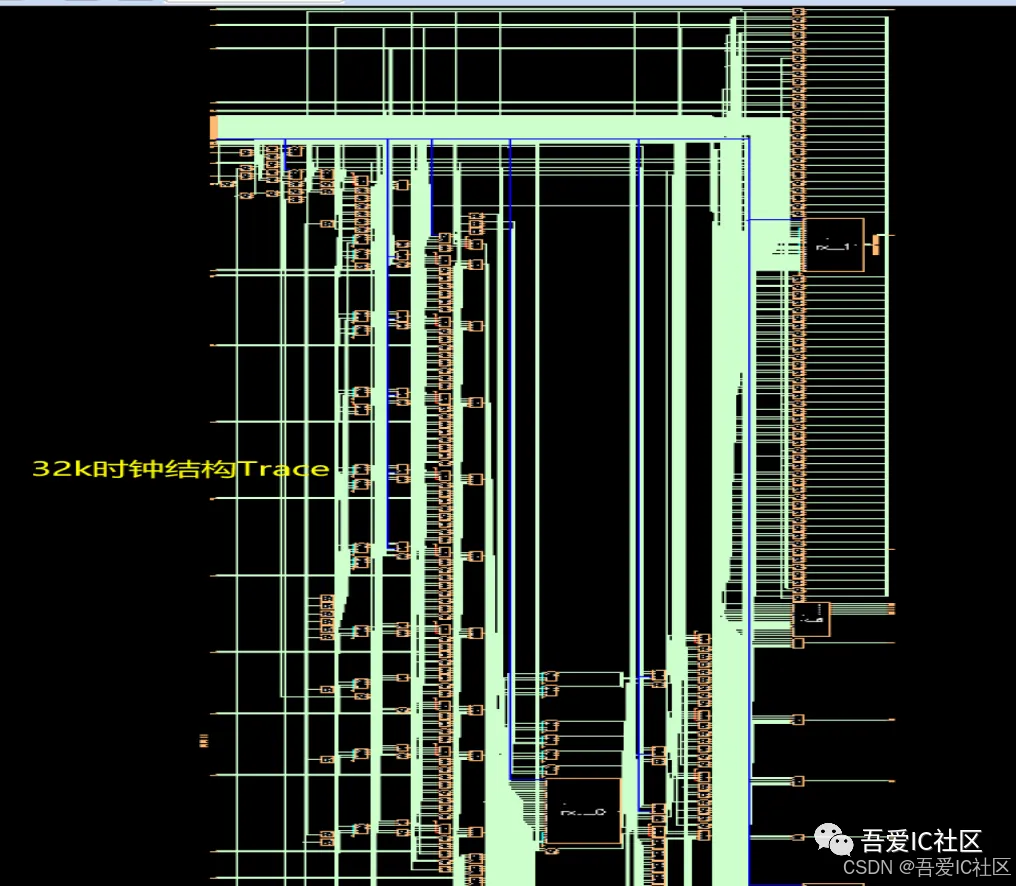

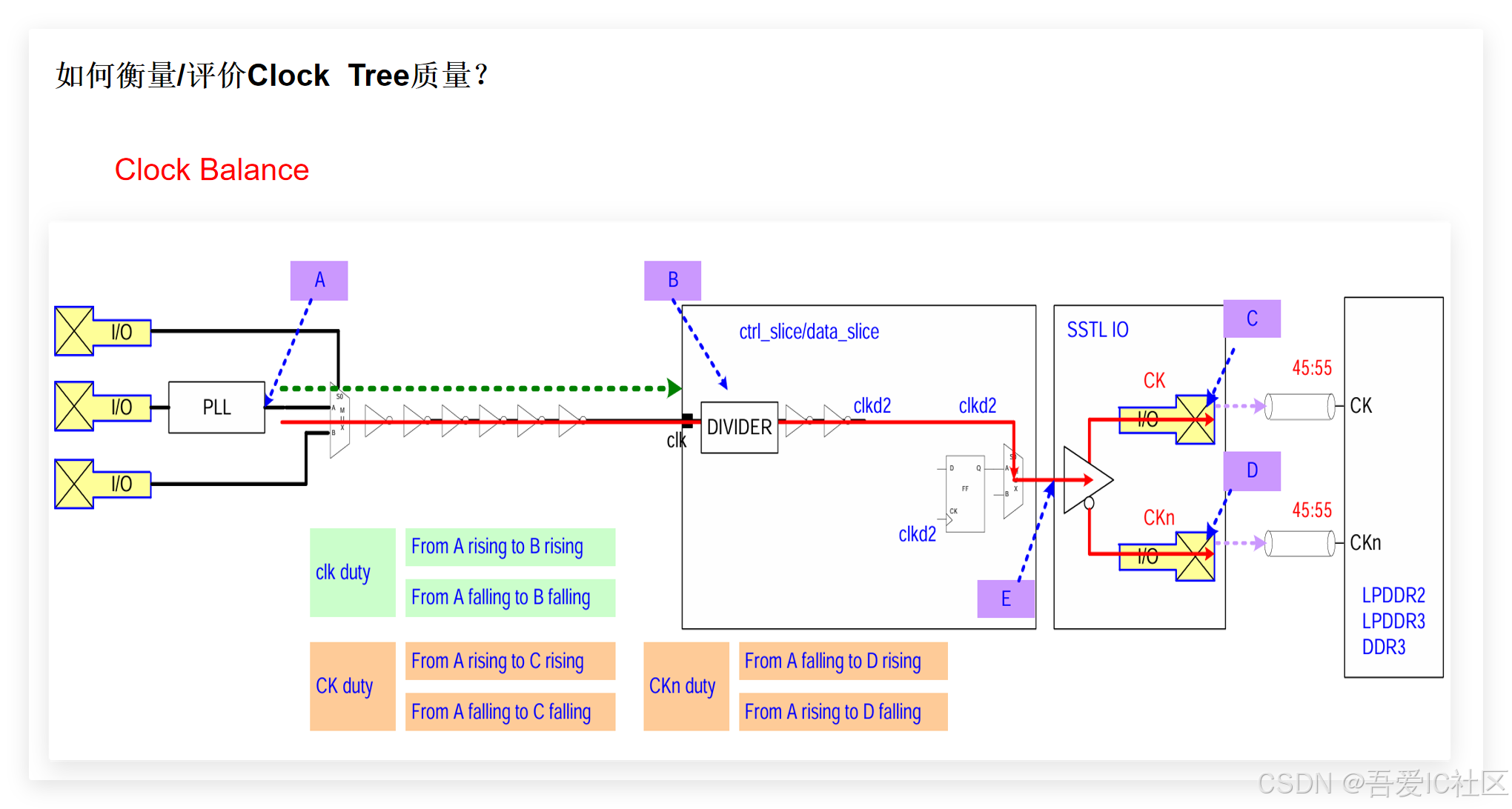

9)Cpu子系统时钟树结构trace和分析

10)顶层Top和子模块CPU Clock Tree Balance处理和common clock path处理

11)Timing时序和功耗优化方法理论和应用

12)静态时序分析中的Timing Exception

13)Fatten RC抽取流程及其checklist检查

14)根据Foundary Timing Signoff标准建立PT时序检查环境

15)PT Timing Signoff的Hierarchical和Flatten Timing检查

16)PT的Timing与PR Timing的差异性分析

17)CPU子系统的Dummy Insertion和with dummy的Timing分析流程

18)Hierarchical &Flatten LVS检查原理及其实现技术

19)A7 top wrapper层的Level Shifter Cell的选型及其摆放

20)A7 top wrapper层Level Shifter Cell Secondary PG连接方法及其roubust检查

21)整个CPU子系统的IR Drop数据准备及IR Drop结果分析

22)Function ECO原理及案例实现

课程特色:

1)真实Hierarchial项目

2)理论结合实操

3)一线12年后端经验工程师亲自授课(星主本人),毫无保留分享自己做项目的思路和方法4)一对一答疑+远程VNC协助解决问题

服务学习周期:视频课程和图文教程都是永久有效。服务器使用时间为3个月,一人一账号。

四.Clock Gen复杂时钟结构设计的时钟树综合(分段长tree)

课程周期:1.5个月授课方式:每周2次直播课 (服务器可以用8周时间)课程特色:全网独家,星主本人亲自授课,毫无保留分享自己13年后端长tree核心机密。

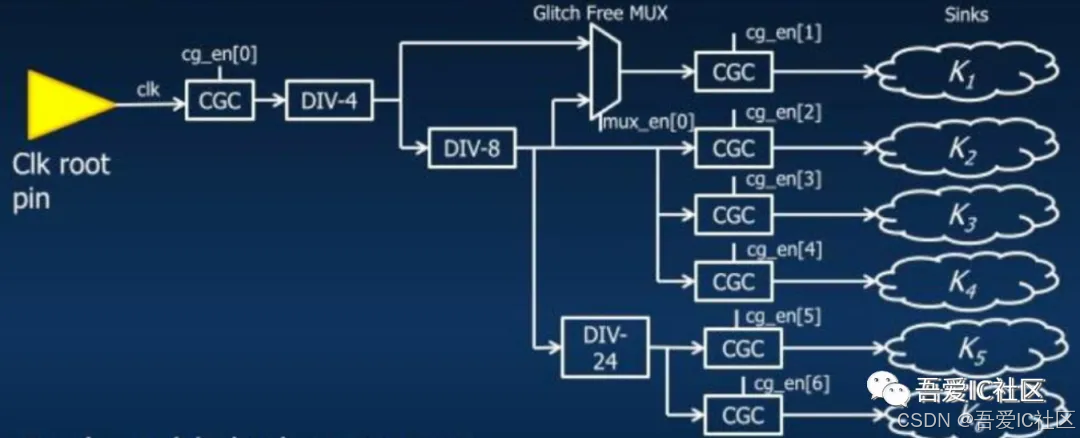

内容主要聚焦在以下几个方面:

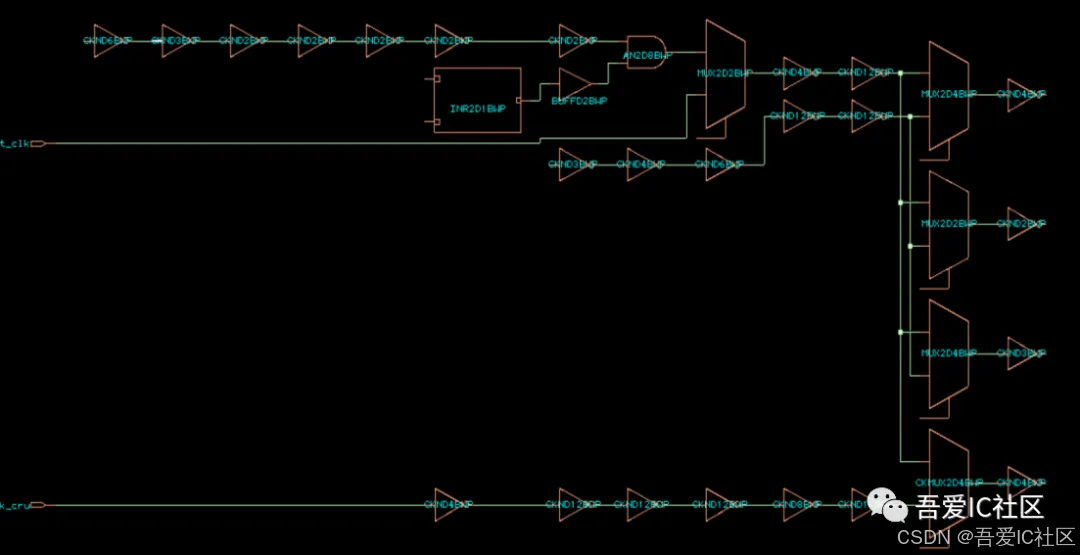

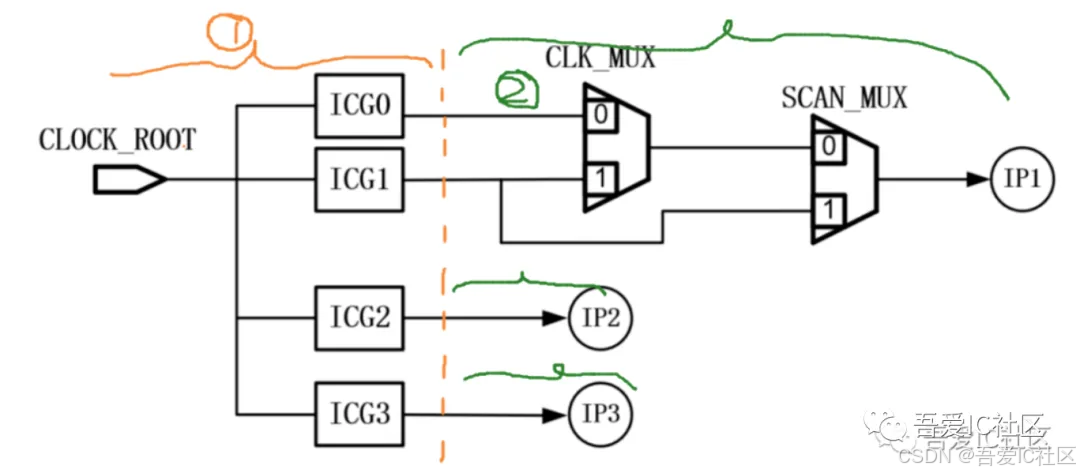

1)手把手教会Trace Clock Tree结构

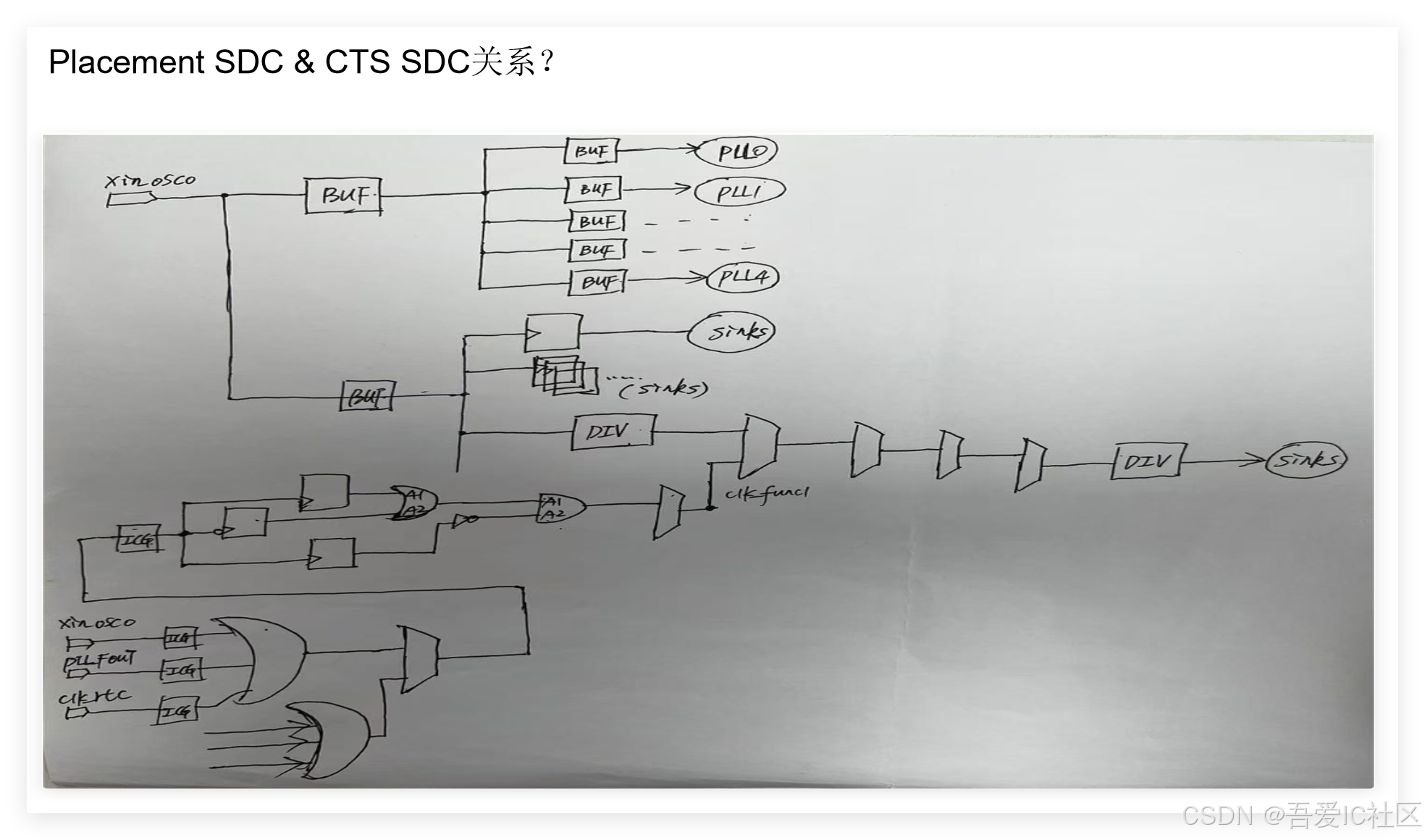

2)根据自己画的时钟结构图编写分段长Clock Tree的SDC

3)时钟树质量分析,Debug及结果优化

4)通过PrimeTime的Timing Signoff分析

5)Clock Tree功耗分析及优化时钟结构

- 时序约束文件sdc和长clock tree用的cts sdc编写方法及策略

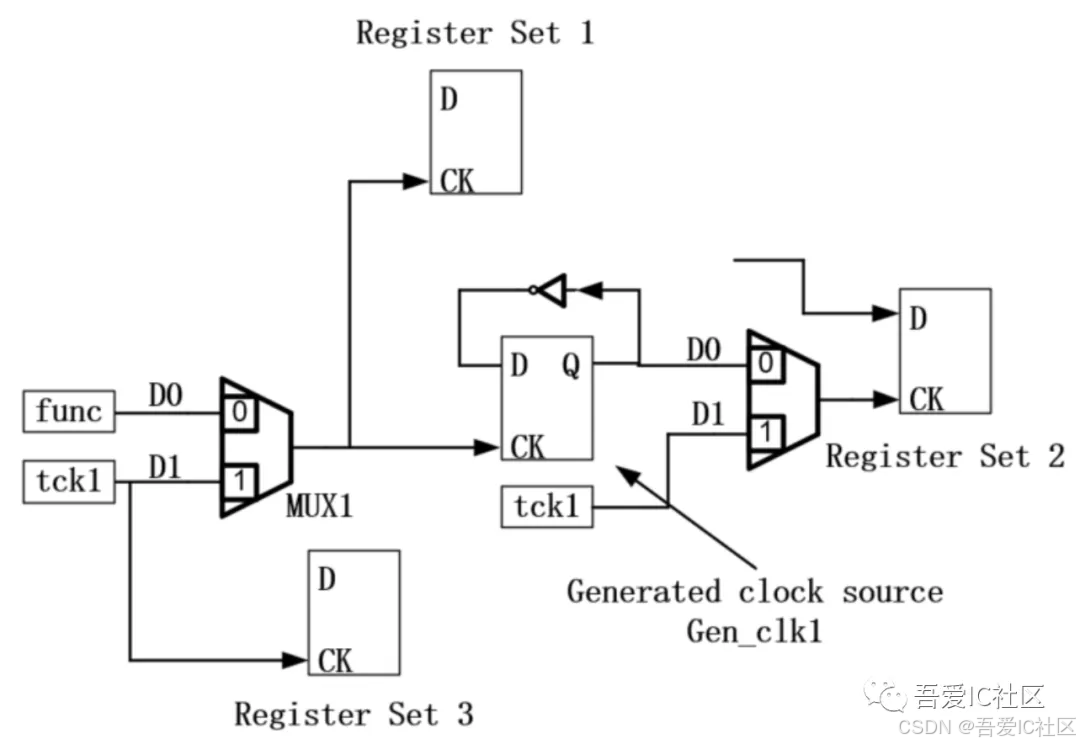

分频电路结构Trace

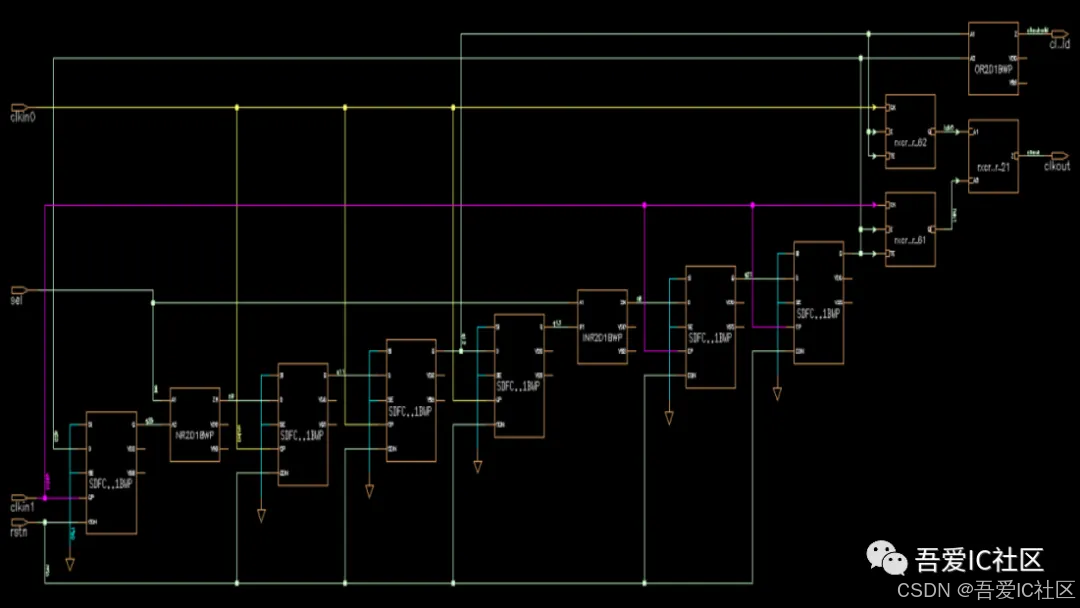

多时钟Mux切换结构Trace

以下几种SoC芯片中常见的时钟结构的长tree方法在本次课程中都会系统介绍到。

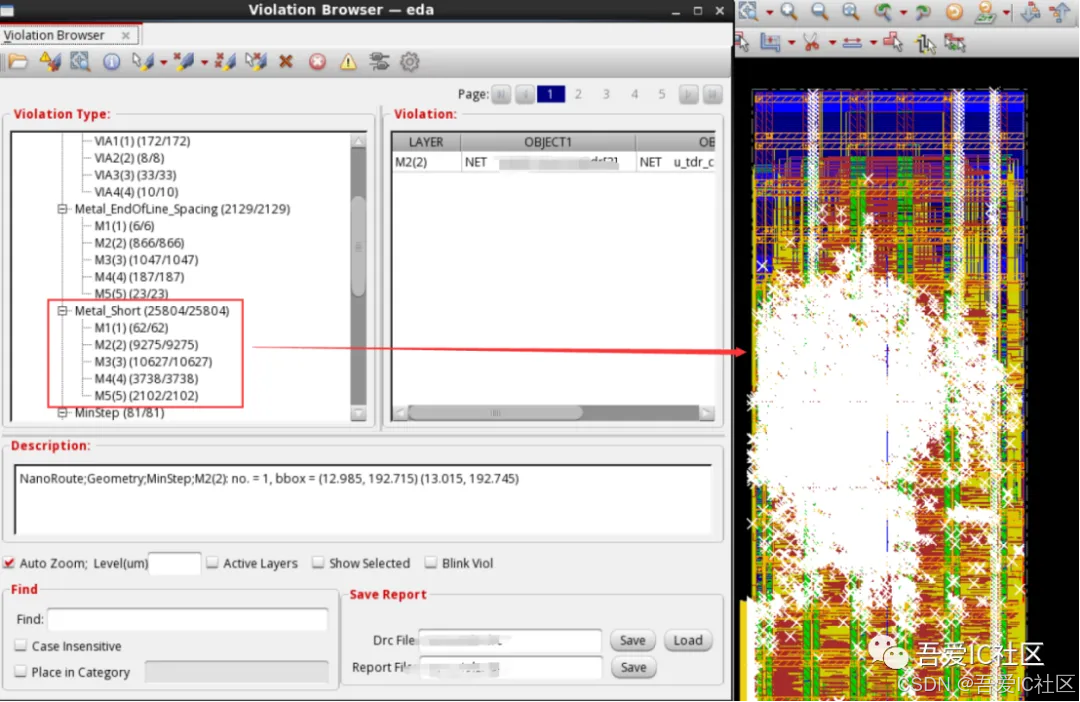

没有编写长clock tree sdc的route drc有八万左右,具体如下图所示。分析clock tree结构,采用分段长tree的方法,同样的设计,route drc是0。

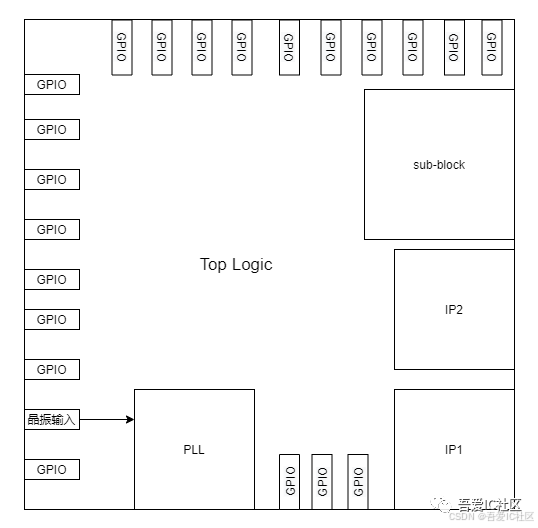

五.小规模SOC TOP数字后端实现

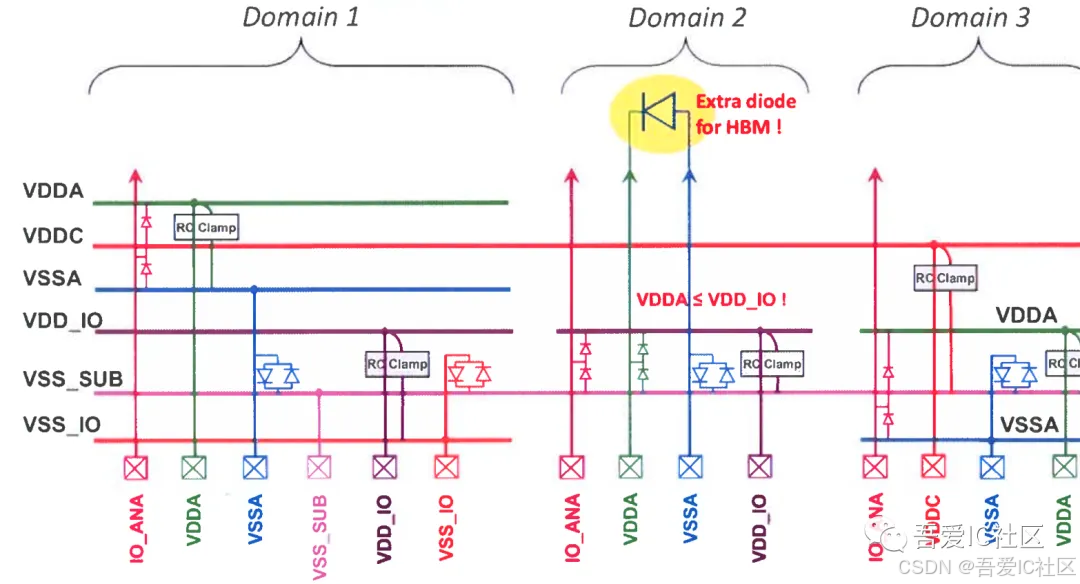

内容涉及IO PAD Ring设计,顶层和IP的powerplan,时钟结构分析和时钟树综合策略,顶层top的数字后端实现,DRC和LVS。

这个项目不仅仅有PR全流程的内容还涉及到physical方面的很多内容,比如IO选型,ESD设计,IO电源如何供电给IP,memory和标准单元等等。

六.物理验证PV(DRC,ERC,LVS,PERC)

先从理论上介绍PV,然后结合我们的四核A7 top项目来实操Flatten的DRC,ERC和LVS。

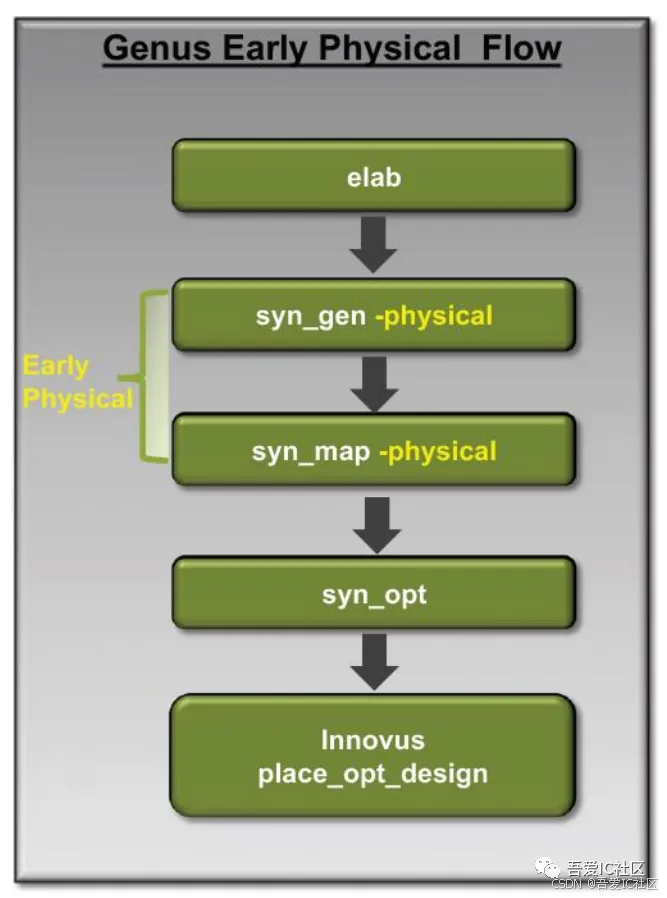

七.逻辑&物理综合(DC&Genus flow)

这部分内容作为目前Cortexa7core项目的延伸,从目前的PR往前push到逻辑综合阶段,从RTL阶段开始做逻辑综合。由于设计是高性能CPU,所以综合会引入物理综合DCT和Genus ispatial,实现最佳PPA的目的。

八.ESD基础及实践

ESD基础理论及SoC Top项目的ESD设计。

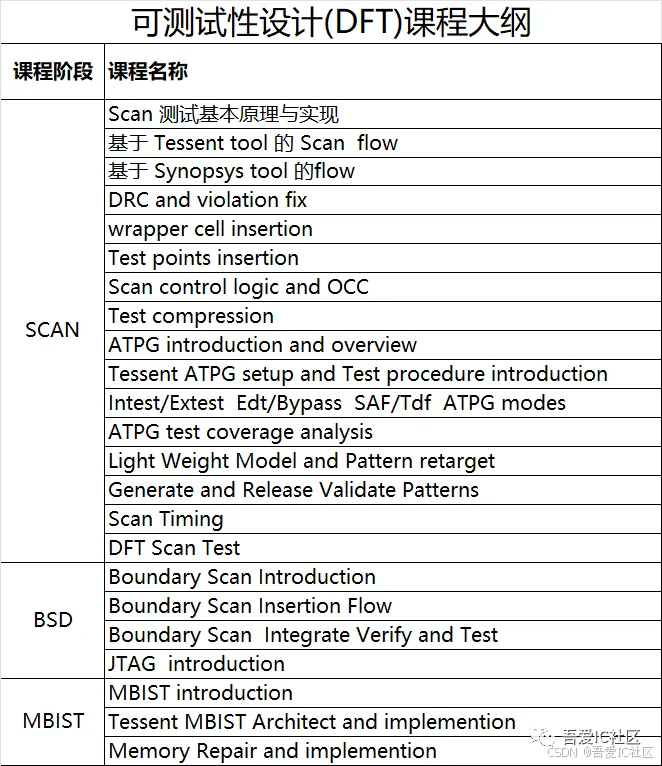

九.DFT课程

DFT课程主要是面向DFT工程师和想从事这方面的学生朋友们。

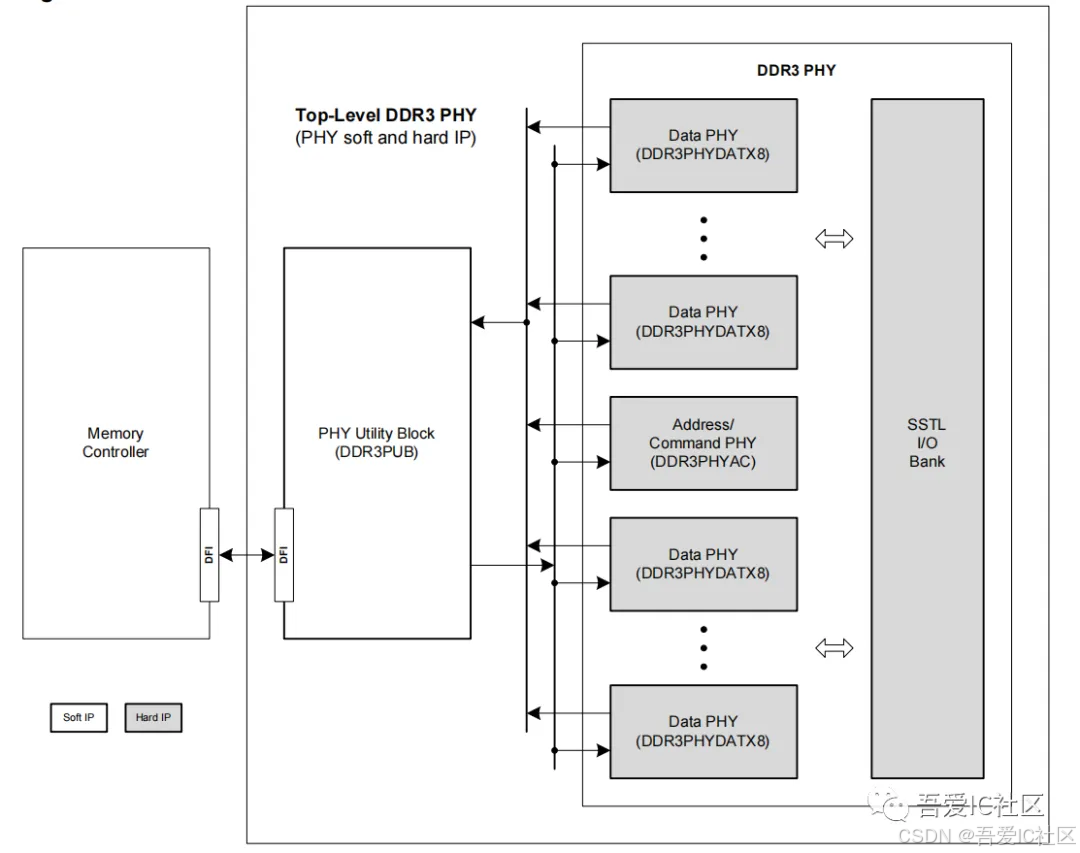

十.基于TSMC 28nm的DDR3PHY的后端实现全流程

1300

1300

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?