第一章 什么是PPA,它们之间的关系?

PPA 是芯片设计中一个非常重要的概念,分别代表性能(Performance)、功耗(Power)和面积(Area)。它们之间往往是相互制约,不可兼得,只能根据芯片的需求做一定的折中、取舍。通常在芯片设计前期需要通过PPA评估,进行前端设计的前期优化,确定选择芯片的工艺制成、工艺库类型,并基于此评估时钟频率跑到的极限、面积(die size)大小、功耗情况,进而预估性能、成本,并据此选择合适的封装形式。如果PPA评估中,存在不满足芯片规格需求的方面,则需要进行前端设计的改进或者芯片工艺制成的切换。在芯片完成前端设计后,进行后端设计时,也会不断收集PPA数据,进一步确定对芯片规格的达成,并可能产生对前端设计的迭代。

1.1 性能(Performance)

性能通常指的是芯片处理信息的速度和效率,主要由时钟速度、延迟和数据吞吐量等指标来衡量。提高性能通常涉及:1)增加时钟频率:提升芯片的计算速度,但可能会增加功耗和发热量。2)优化电路设计:使用更高效的逻辑门和更短的路径来减少信号传播延迟。

1.2 功耗(Power)

功耗是芯片在工作时消耗的电能,分为动态功耗和静态功耗。

动态功耗:与信号切换频率和电压有关,通常随着时钟频率和电压的增加而增加。

静态功耗:主要由漏电流造成,涉及晶体管在非活动状态下仍然消耗的电能。在现代技术中,随着工艺节点的缩小,静态功耗的重要性日益增加,尤其对于移动端设备,静态功耗大的控制要求更加严格。

1.3 面积(Area)

面积指的是芯片在硅片上所占的物理空间,通常以平方毫米(mm²)来表示。面积的大小直接影响生产成本和集成度。设计中需要考虑:1)逻辑单元的数量和布局,增加逻辑门和存储单元会占用更多面积。(2)互连长度:较长的连线会占用更多空间并引入更多延迟。

1.4 PPA 之间的权衡

在设计过程中,通常需要在性能、功耗和面积之间进行权衡。例如:提升性能(提高时钟频率)通常会导致功耗的增加和面积的增大。减少功耗可能会导致性能下降,或者需要使用面积更大的设计来满足时钟频率要求。面积的增加虽然可以改善性能和降低功耗,但会提高制造成本。相互之间存在矛盾,需要更具芯片定位进行折中选择。

第二章 如何选择Fab、工艺制程、工艺库选项

需要综合考虑多方面的因素,选择Fab厂、工艺制程以及某一工艺制程下的工艺库选项。芯片可以针对不同工艺库进行PPA分析为上述选择提供数据支撑。

2.1 如何选择Fab

目前全球主要的Fab厂包括台积电(TSMC)、三星(Samsung)、中芯国际(SMIC)、联华电子(UMC)以及华虹等。 Fab选择首先要考虑的是流片周期。价格因素在Fab选择中也占据重要位置,特别是对于小公司来说。对于大公司而言,投入与产出的平衡是决策的关键。研发预算与产出周期的考量,以及芯片自研与外采的矛盾,都是在选择Fab时需要权衡的因素。量产能力是另一个不容忽视的因素。Fab的量产能力差,甚至没有量产能力,对于希望实现量产的公司而言是极大的挑战。即使设计阶段表现优秀,也无法确保后续的量产顺利进行。

在技术细节方面,每个Fab提供的解决方案都有其特点,设计人员在选择Fab时需要考虑到关键器件的性能,如端面耦合、光栅耦合、波导、MZM调制器、GeSi探测器等。这些问题不仅涉及理论设计,还涵盖了实际应用中的非线性、可靠性、阻抗匹配、带宽、色散等问题,因此在设计阶段必须全面考虑。流片的持续性同样值得关注,包括中美关系、Fab产线更迭、硅光业务比重以及Fab对硅光未来发展的重视程度。这些因素都可能影响到流片的成本和可能性,因此需要提前评估和规划备份方案。此外,Fab的开放度和工艺稳定性也是决策时需要考虑的因素。低开放度的Fab可能限制了设计的灵活性,而工艺稳定性则关乎最终产品的良率和一致性,对产品性能有直接影响。

2.2 如何选择工艺制程

工艺制程选择,即芯片工艺节点的选择,需要考虑很多方面的因素。首先是根据芯片的规格预估满足PPA要求的工艺节点,可以根据经验(也可以参考竞品采用的工艺)进行大致的判断。其次是芯片的产品定位,高端先进 /中端主流 / 低端低成本 / testchip,不同的产品定位选择不同的工艺。一般而言,高端先进工艺的NRE费用和wafer成本高,低成本工艺的NRE费用和wafer成本低。在满足芯片规格需求的工艺中,按照产品定位和研发投入选择合适的工艺。最后在现在这个全球大环境下更需要考虑供应链安全的因素,有没有被禁的风险、Fab的重视和配合度、工艺下有没有足够的ip vendor和design service vendor。归根结底,选择工艺其实没那么容易,但是也没想象的那么难,它更多的还是一本经济帐。不过不同工艺代差还是非常明显的,指望靠架构/微架构/工程实现把它弥补回来的难度很大,需要三思而后行。

最后是工艺选择的逻辑,在芯片可实现的前提下,工艺一般分成三种:低成本工艺、主流工艺、领先工艺。

低成本工艺:在性能和功耗上有劣势,优点是NRE费用低,常用来MPW做demo或者做第一代产品原型,一般是主流工艺落后一代

主流工艺:芯片上市的时候预估的竞品工艺,芯片从工艺上没有收益也没有劣势,上市的芯片正常选择这个比较保险

领先工艺:芯片上市的时候比预计竞品领先一代的工艺,芯片依靠工艺优势就可以领先竞品,PR价值高,适合芯片量大时,缺点是先进工艺NRE费用高投入风险大

2.3 如何选择工艺库选项

某一工艺节点下,Fab还会提供不同的工艺库选项。以TSMC 28nm为例,具体如下:

| Process option | Description |

| HP | High-performance |

| HPM | High-performance mobile |

| HPC | High-performance computing |

| HPL | High-performance,low-power |

| LP | Low-power |

| HPC+ | High-performance computing plus |

| ULP | Ultra-low power |

用户需要根据自己的产品定位,选择不同的工艺库选项。例如:非常强的性能需求,那就选择HP,极低功耗要求,就选择ULP。

第三章 如何选择STD cell中track/channel length/ VT

在确定了Fab厂、工艺制程和工艺库选项后,在进行PPA分析时,需要选择track、VT和channel length,也可基于不同选择的进行PPA对比,最终确定实际芯片使用的工艺库。

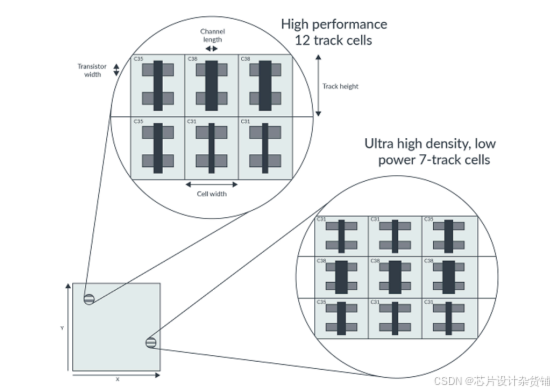

3.1 TRACK选择

7T/9T/12T分别对应ultra-high-density(for lowest power)、high-density(for highest density)、high-speed(for highest performance)。T代表track,是单元库的版图规则,作为一个计量单位。标准单元库的单元高度,基本都是固定的,方便版图的布局;高度,通常以track作为计量单位。

track单元通常被认为是标准尺寸,带有tap(n/pwell pickup),适用于一般设计需求。7-track单元尺寸较小,适用于低功耗设计,但速度较慢。12-track单元适用于高速设计,金属1的rail更宽,能够承载更多电流,从而提高速度,但也增加了功耗。

设计者可以根据具体的设计目标选择合适的track。例如,如果设计需要低功耗,可以选择7-track单元;如果需要高性能,可以选择12-track单元。在某些情况下,设计者可能会选择混合使用不同track的单元,以达到最佳的性能和功耗平衡。

通常在芯片设计中根据需要选择一种track,但在SOC中也会使用多种track混合使用,例如:SOC中CPU时钟12T,其他部分使用9T或者7T。

虽然9-track和12-track标准单元可以混合使用,但在实际操作中需要注意以下几点:1)布局和布线(Layout and Routing):混合使用不同track的单元可能会增加布局和布线的复杂性。设计者需要确保不同高度的单元在布局上不会产生冲突,并且布线能够有效地连接这些单元。2)电源和地线(Power and Grounding):不同track的单元可能有不同的电源和地线要求。设计者需要确保电源和地线的分配能够满足所有单元的需求,避免出现电源噪声或其他问题。3)兼容性和验证(Compatibility and Verification):混合使用不同track的单元可能会带来兼容性问题。设计者需要进行充分的验证,确保混合使用不会影响电路的功能和性能。

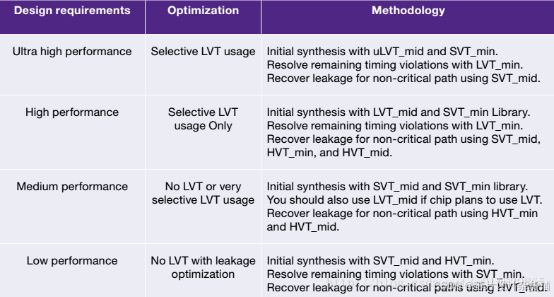

3.2 VT选择

工艺库中standard cell 的LVT、HVT、SVT的区别在于它们的阈值电压和性能与功耗之间的权衡。HVT代表High V threshold,其功耗最低,适用于非关键时序路径,以节省功率。LVT代表Low V threshold,适用于关键时序路径,因其速度快,但在泄漏电流作用下功耗较高。SVT(或RVT)代表Standard V threshold,是两者之间折中选择,提供中等的延迟和功耗需求。在综合逻辑设计时,设计人员根据具体应用的性能和功耗需求,选择HVT、LVT或SVT逻辑门。

在进行逻辑综合时可以分别进行完全不使用LVT、使用5%以内LVT、完全放开限制使用LVT等不同的VT使用策略进行PPA评估,对比面积、功耗、性能三方面的表现。针对不同VT比例限制,可以在Design Compiler中通过命令set_multi_vth_constraint设置。

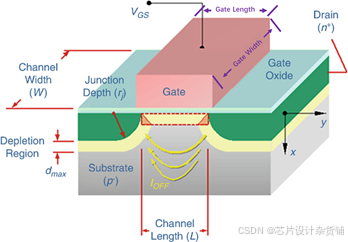

3.3 Channel length 选择

Channel length对应不同的gate-length,即沟道长度。随着沟道长度的依次增加,速度依次降低,漏电依次减少。同一TRACK下不同的沟道长度,cell面积是相同的。同一TRACK下不同沟道长度的cell是可以一块使用。例如TSMC 28nm channel length可选择C31和C38。

在确定TRACK后,可以选择channel-length和VT,且channel-length和VT在综合时,它们是兼容的,可以混合使用。例如:某一芯片性能要求较高,但还需要控制功耗,但对面积要求很低。以SMIC 40nm为例,通常可能会选择12TRACK,C40和C50 channel-length混合使用,HVT,RVT,LVT全使用,但会控制LVT比例(例如5%以内),一定程度上控制功耗。上述的选择过程就是基于不同的选择,进行try run之后对比频率是否可收敛,功耗和面积是否满足要求,最终选择适合目标芯片的工艺库以及standard cell。

第四章 PPA分析中如何选择PVT library

在进行综合和功耗仿真时,工艺库PVT选择。PVT是工艺(process)、电压(voltage)和温度(temperature)的缩写。通常在进行综合时会选择最差时序的PVT:SScorner,低电压,高温或者低温(有时有反温度效应,需要选择低温)。WCS (Worst Case Slow) : slow process, high temperature, lowest voltage;WCL (Worst Case @ Cold) : slow process, lowest temperature, lowest voltage。

在进行功耗分析时,一般会关心最大功耗以及typical功耗情况。组合如下:ML (Maximal Leakage ) : fast process, high temperature, high voltage。TL (typical Leakage ) : typical process, high temperature, nominal voltage。

第五章 Memory选择

在现有芯片设计中,通常Memory 的占比都比较大,对全芯片的功耗和面积有关键性影响。在系统设计时,就要优化memory数目和大小,同时设计上通过控制memory使用,减少memory反转,降低memory功耗。在这个过程中,需要对不同memory设计方案进行PPA评估,进而给出最优的memory组合。

通常单块memory越大,时序就越差。为评估出最优的memory组合,可能涉及到memory拆分与合并。从面积和功耗角度看,拆分memory会增加功耗和面积,对于较小的sram,能合并建议尽量合并;从频率角度来看,随拆分memory后word和bit 的位数降低,可以增加单块memory 的工作频率。这就需要在memory拆分和合并中进行权衡。

第六章 功耗分析中方法

通常进功耗分析可以通过PTPX,它是基于primetime环境(简称pt),对全芯片进行power静态和动态功耗分析的工具。包括RTL级和门级的平均功耗和峰值功耗。

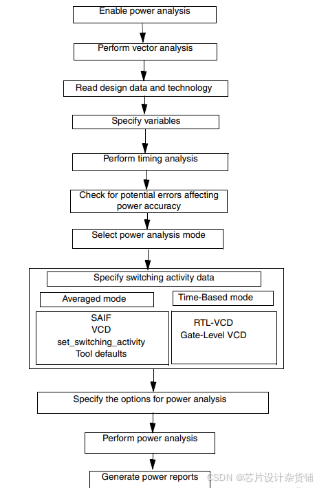

6.1 功耗分析流程

下面是功耗分析流程图:

总结起来主要8个步骤。

- step0: 使能功耗仿真,就是个开关,总要打开的。

- step1: 选择仿真模式。PTPX有两种功耗仿真模式。一种是算平均功耗(averaged), 另一种是根据波形详细算(time_based), 这两种模式具体怎么算我们后面详细讲。

- step2: 读入设计数据和库文件。其实主要是两部分,网表文件(verilog,.v)和库文件(synopsys database,.db, 提供NLPM或者CCS模型)

- step3: 设置仿真条件。主要是仿真温度和电压。PTPX根据温度和电压,根据db文件中提供的参数来计算功耗。

- step4: 指定翻转率数据。这个地方,average模式和time_based模式提供的文件有区别。后面我们详细讲这两种模式下怎么提供文件。

- step5: 这一步提供一些额外仿真设置,按需设置,没什么特殊的。

- step6: update power。真正开始跑仿真。

- step7: report_power。将报告报出来。

6.2 功耗分析模式

PrimeTime PX支持两种功耗分析模式: averaged mode和time-based mode。

6.2.1 Averaged Power Analysis

平均功耗,是基于翻转率toggle rate来分析的。翻转率的反标,可以是默认翻转率、用户定义switching activity、SAIF文件或者VCD文件。功耗结果期望准确的话,首先要保证翻转率的标注要准确。前期做功耗分析,可能只是一个评估作用,没有那么准确。

工具支持基于仿真的switching activity文件类型,包括:

- VCD

- FSDB

- VPD

- SAIF

如果没有上述文件,那可以使用user-define switching activity commands,来建模一个虚拟的activity去精确power结果。

所需文件:

- logic库文件,必须是.db格式;

- 网表文件,支持verilog、vhdl网表,db、ddc、Milkyway格式的网表也可以;

- sdc文件,为了计算平均功耗;

- spef文件,寄生参数信息;

- VCD/saif文件,记录翻转率(若没有,需要人为设置翻转率)

6.2.2 time-based power analysis

在该模式下,需要提供VCD或FSDB文件,工具会分析峰值功耗,并生成功耗波形等。SAIF格式对此不支持。

第七章 总结

总之,PPA分析需要基于不同的组合进行仿真,获得面积、功耗、性能数据,选择最终的组合进行设计并流片。

2124

2124

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?