DDR4简介

DDR4(double data rate 4)是一种高性能存储器标准,用于计算机和服务器的内存模块。与前一代标准DDR3相比,DDR4在带宽、功耗和时钟频率等方面都有所提升。首先,DDR4具有较高的带宽,DDR4的数据速率比DDR3快得多,能够以更高的频率读写数据。这种高带宽对于大量的数据的应用非常重要。其次,DDR4芯片具有更低的功耗,由于技术升级和结构优化的原因,DDR4比DDR3能够以更低的电压工作。这不仅有助于节省能源,还有助于减少发热量,提高整个系统的稳定性。此外,DDR4还支持更大的内存容量,这对于处理大型数据库和运行内存密集型应用的服务器来说非常重要。

DDR4通过架构革新与能效优化,成为高性能计算时代的关键组件。尽管DDR5已登场,但DDR4凭借成熟的生态和性价比,仍在主流市场占据重要地位,尤其适合追求稳定与成本平衡的用户。

总结起来,ddr4芯片作为一种高性能内存标准,具有高带宽、低功耗、高时钟速率、大内存容量等优势。它适用于各种需求高性能的应用场景,包括游戏、影像处理、虚拟现实和数据中心等。作为技术的不断进步,ddr4芯片在未来可能会有更广泛的应用和更大的发展空间。

DDR4 IP核建立

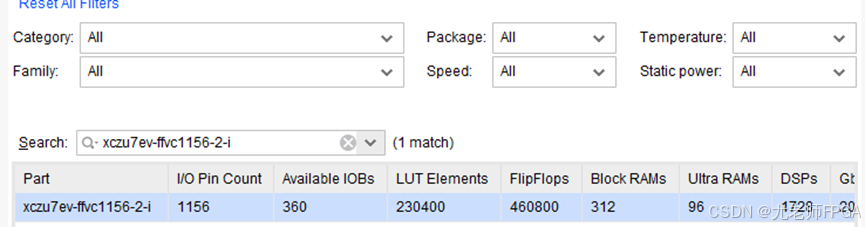

我们以Xilinx ZCU104开发板为例,在这里,我们选择xczu7ev-ffvc1156-2-i芯片,建立vivado工程,如图1。

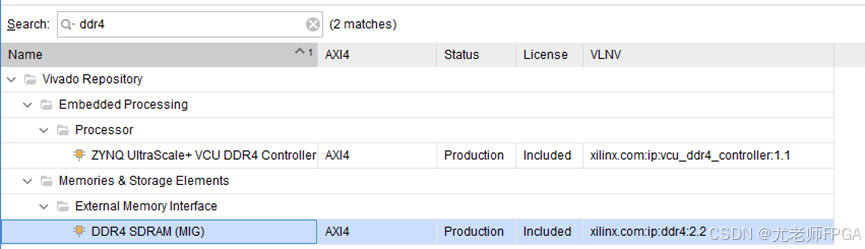

2、打开IP 目录,点击DDR4 SDRAM(MIG),进入ddr4配置界面,如图2

DDR4的配置

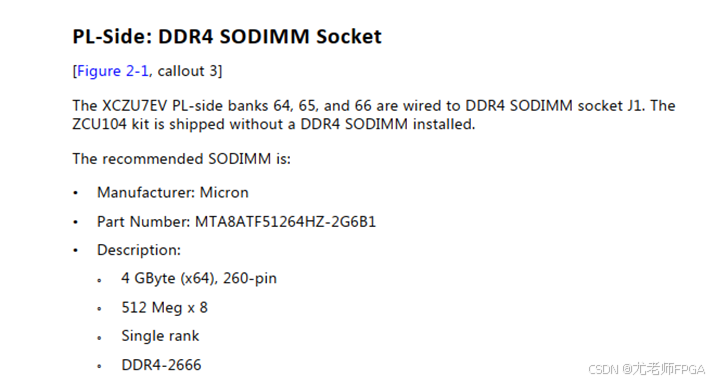

在ZCU104开发板中,使用SODIMM插槽来连接DDR4内存模块,在开发板手册中介绍了推荐的内存条规格。如图3所示。

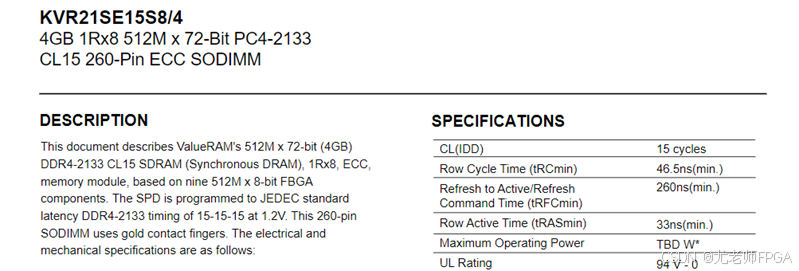

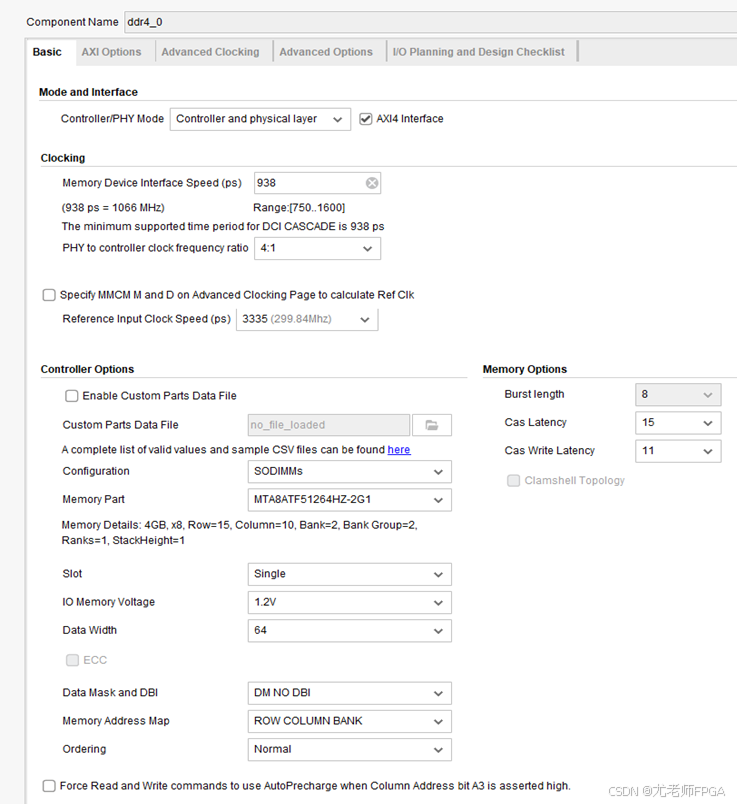

根据选用内存条的规格,如图4,我们进行ddr4的配置。

在Basic页面下,首先勾选上AXI4 Interface选项,我们选用的内存接口速度为2133MHz的ddr4芯片,由于双沿触发,频率为1066MHz,那么周期应为938ps。

因为原理图中有专门给ddr4输入的一组300MHz的差分时钟引脚,所以参考输入时钟速率选择300MHz。

开发板上使用的是标准化的SODIMM插槽,所以在Configuration选项中选择SODIMMs,Memory Part 根据使用的ddr4型号选择MTA8ATF51264HZ-2G1,数据位宽选择64位。

对于Controller/PHY Mode 的选择,我们使用Controller + PHY模式,Xilinx UltraScale/UltraScale+等高端FPGA通常包含硬核PHY,选择Controller + PHY模式可直接利用硬核,降低功耗和延迟,并且此模式的开发更易上手。

选择SODIMMs意味着控制器需要适应SODIMM模块的物理和电气特性,在Slot中选择Single,管脚内存电压选择1.2V,数据位宽我们选择64位。

Data Mask and DBI中选择启用数据掩码,不使用DBI。

内存地址映射选用ROW COLUMN BANK 模式。

Cas Latency:列地址选通延迟为15。

配置如图5所示。

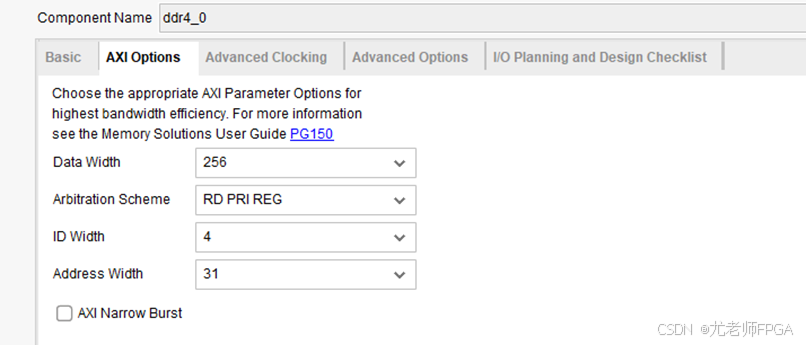

接下来配置axi接口,可以根据自己的需求来配置数据的位宽选择,在这里数据位宽我们选择256位,地址位宽固定为31位。ID的位宽可以随意设置。仲裁方案选择RD PRI REG方案,该方案默认为读请求优先,也可以通过用户接口(axis接口)动态调整优先级。如图6所示。

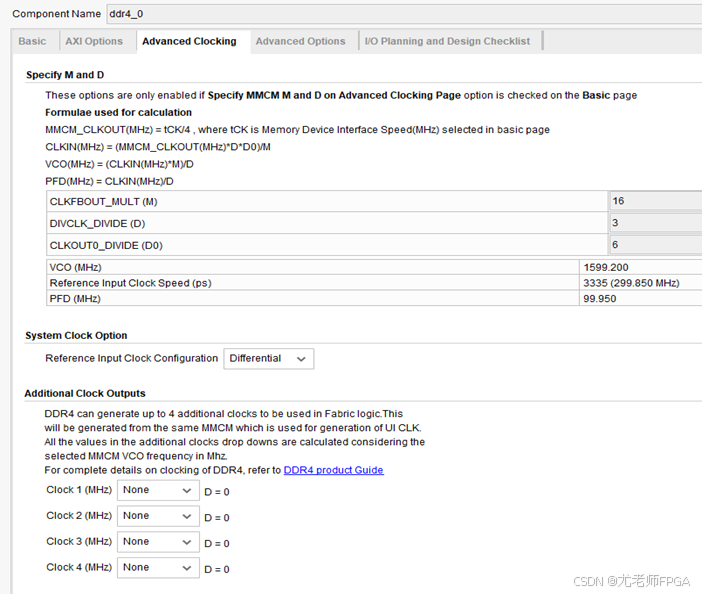

接下来我们来配置时钟,系统时钟保持为差分时钟就好,因为在原理图中有专门的差分时钟引脚连接使用。额外时钟没有需要,不需要勾选。配置如图7所示。

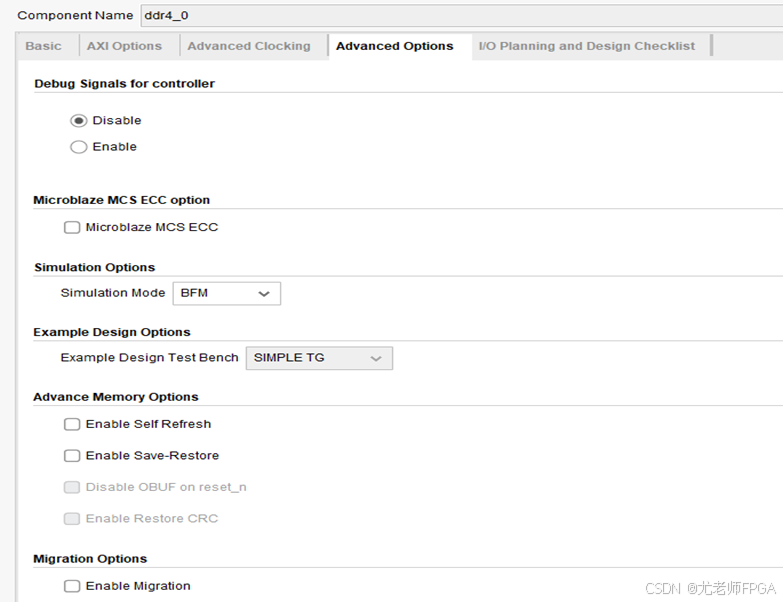

高级选项页面默认配置,在仿真模式中选择BFM模式,可以增加仿真速度。如图8所示。

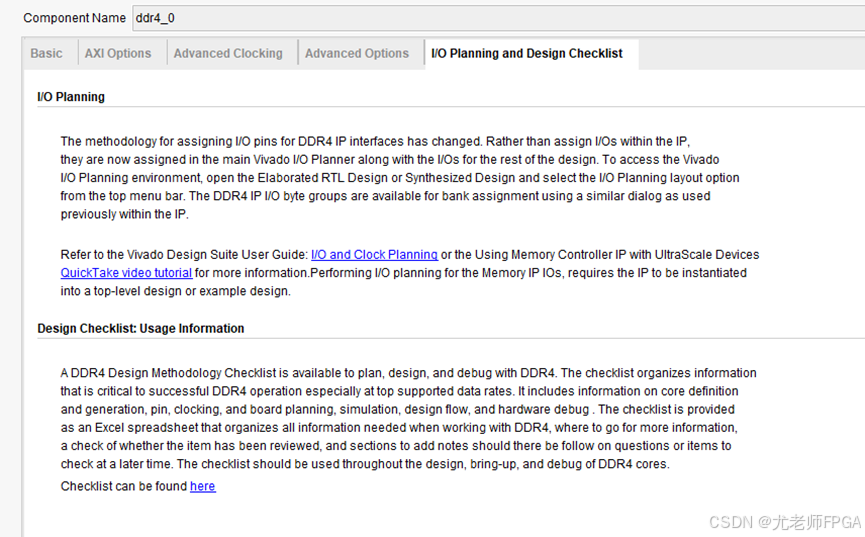

与DDR3比较,对于DDR4的管脚绑定不在IP核中添加,而是使用XDC文件实现管脚约束。 如图9所示。

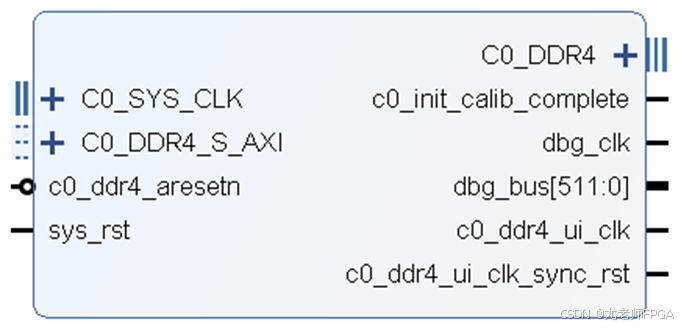

ddr4的接口信号如图10所示

到此,ddr4IP核建立完成。我们后边会着重讲解它的接口信号的含义,以及管脚约束。以方便理解ddr4的工作原理。(未完待续)

496

496

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?