Camera接口分类

Camera接口实在多种多样,总的来说分为两大类:Parallel(并口)、Serial(串口)以及USB口,两种大类下面又分为很多子类,类似于软件中提到Class 和SubClass。下面就是干货部分。

Parallel–并口

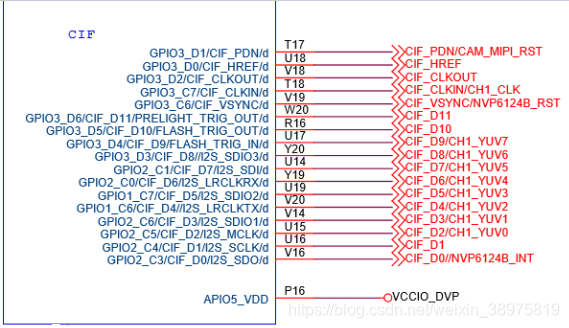

并口一般称DVP接口(Digital Video Port),就是将图像信号按照8bit ,12bit等数据格式,在并行时钟的作用下,一次性传输8位或者12位,这种方式最大的特点就是需要的数据线较多,并行时钟PCLK极限约在96MHZ左右,且走线长度不能过长,所以DVP的最大速率最好控制在72M以下。

上图就是DVP的接线图,可以看到数据线包含D0~D11 12根,时钟包含HREF,VSYNC,RST等信号脚。

Serial–串口

串口可以理解为将数据排队传输,serial主要分为以下几种

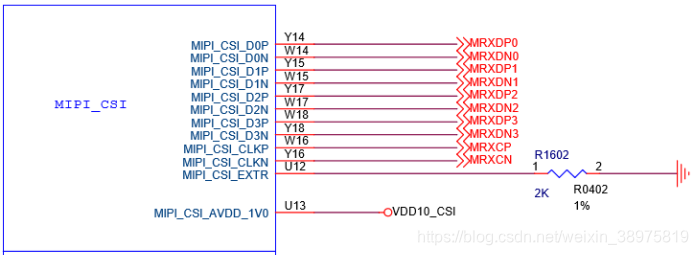

MIPI接口:移动产业处理器接口(Mobile Industry Processor Interface:简称MIPI )1对时钟线,1~4 lane对数据线,单lane最高的传输速率可以达到270Mbps,且都是差分走线,有比较强的抗干扰性。这种接口多用于手机接口,一些监控用的CMOS如SONY IMX185,OV5640等传感器接口;

上图是MIPI接口的接线方式,可以看到数据和时钟都是差分对。

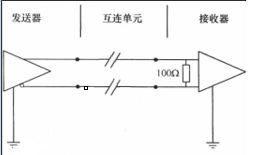

LVDS接口:(Low-Voltage Differential Signaling)低电压差分信号,是一种低功耗、低误码率、低串扰和低辐射的差分信号技术,这种传输技术可以达到155Mbps以上,LVDS技术的核心是采用极低的电压摆幅高速差动传输数据,是一种电流传输方式。在进行PCB设计时,需要主要控制走线阻抗为100欧姆。

上图是LVDS接口的原理图,一般都是在LVDS接收终端,两条线之间加个100欧姆的匹配电阻。

Sub-LVDS接口:Sub-LVDS是LVDS的发展,采用低摆幅电流模式传输系统,同传统的电压模式相比较,在达到几乎相同的性能水平时,由于有比传统模式更好的抗电源噪声能力,它可以在噪声容限低得多,而且摆幅也低得多的情况下工作。

(PS:没有找到Sub-LVDS的原理图,比较尴尬哦!)

USB口

我们先介绍一下UVC是什么,UVC全称 USB video class或者USB device class,是Microsoft 与另外几家设备厂联合推出的USB视频捕获设备定义的协议标准,目前已经成为USB org标准之一。如今的主流操作系统(win XP,linux 2.4.6 and Macos 10.5以及相关的最新版本都支持)都已经提供UVC设备驱动,因此符合UVC规格的硬件设备在不需要安装任何驱动程序下就可以在主机中正常使用。

还有一些接口如HiSpi,(HiSpi,High-Speed Pixel Interface,高速像素接口),这种是Aptina 推出了一款高速串行接口,称为HiSPi。 HiSPi接口可在1到4个通道工作,传输串行数据,外加一条时钟线。每个信号都是差分的,运行速度高达700 Mbps,现在Aptina已经被ONSEMI收购,这种接口只有ON的RGB传感器具备,但是市面上的大部分图像处理器都可以兼容这个接口。

还有一些camera接口,后续会再追加到本文中。

希望以上总结能够帮助到需要的朋友,如有问题,欢迎指出讨论。

1522

1522

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?