一、RTL代码有改动或者添加了ila,vivado综合完成后,导出bitstream

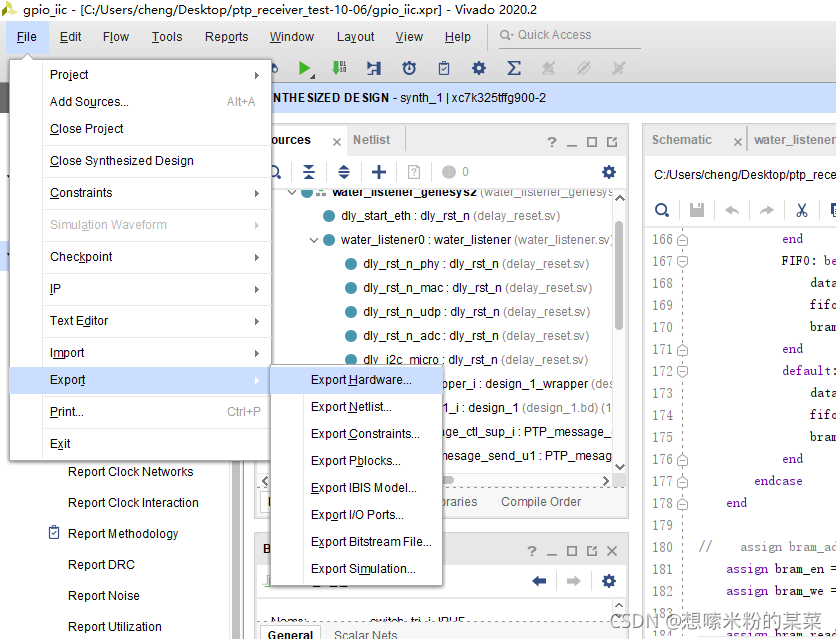

1、在vivado中

2、下一步选择including bitstream;

3、导出.xsa文件

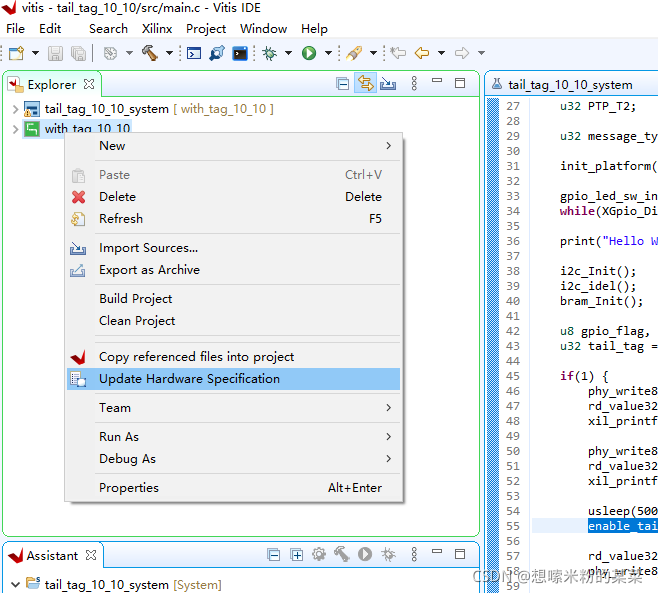

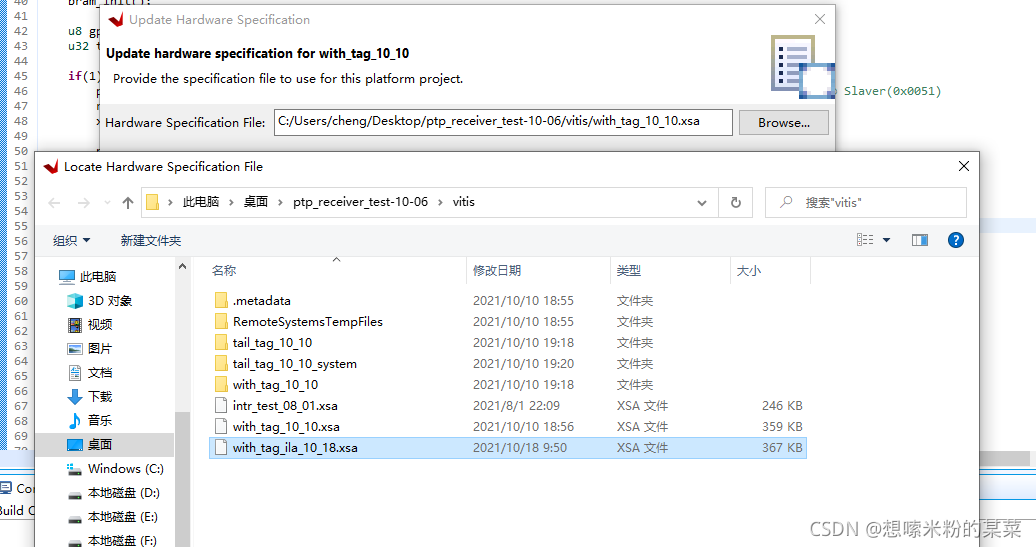

4、在vitis中,update hardware specification,选择相应的xsa文件

二、使用ila debug

1、在vivado中正常添加ila,综合生成bitstream后,在vitis中更新相应的xsa文件,并重新编译;

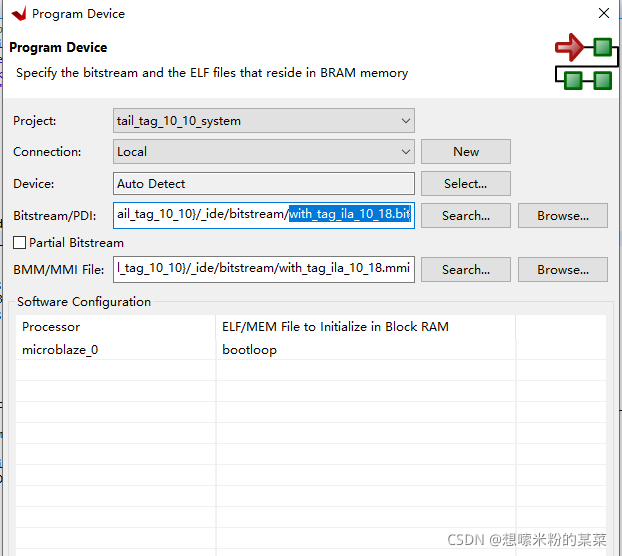

2、在vitis中下载hardware platform(选择的bit和mii文件应该是和xsa文件的名字一样的)

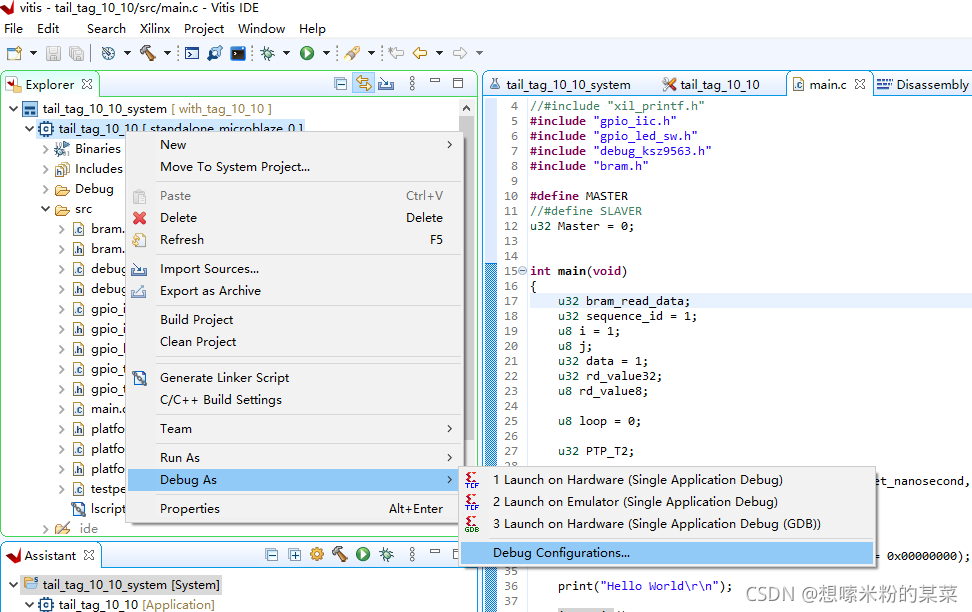

3、在vitis中,下载C语言代码编译后的内容(使用debug)

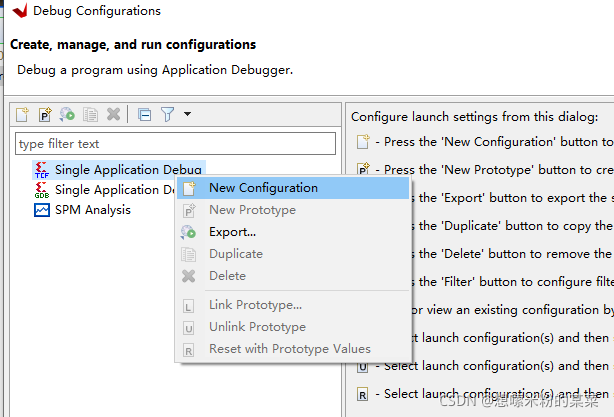

最好是新建一个configuration

然后点击debug,将c语言部分下载到FPGA中

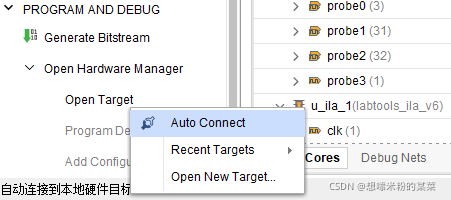

4、在vivado中connect FPGA,若ILA正常的话,会自动跳出波形窗口

5、vitis中控制单步运行或者直接运行。

三、直接运行

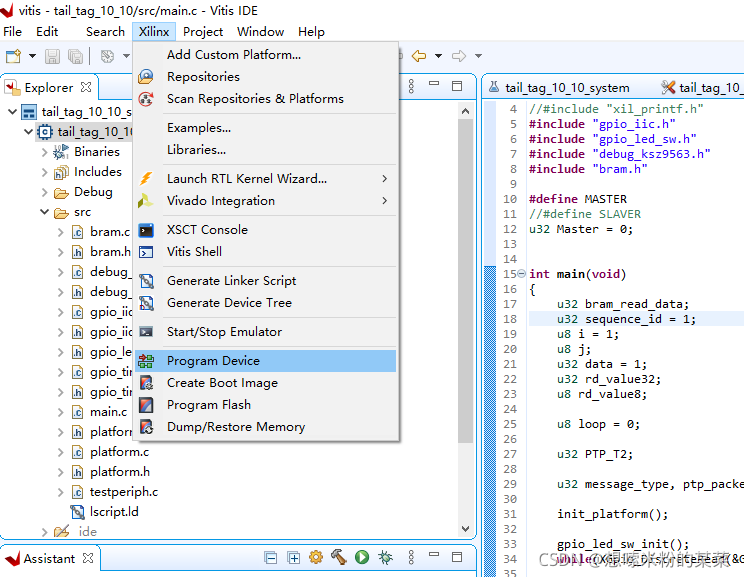

1、在vitis中program FPGA,下载硬件代码;

2、run as 下载C语言部分。

本文档详细介绍了如何在Vivado中进行RTL代码修改或添加ILA(内置逻辑分析仪),然后通过Vivado综合生成bitstream,并在Vitis环境中更新硬件规格、编译及调试。步骤包括从Vivado导出.xsa文件,Vitis中的硬件平台下载,以及ILA调试过程,最后是直接运行C语言代码的步骤。

本文档详细介绍了如何在Vivado中进行RTL代码修改或添加ILA(内置逻辑分析仪),然后通过Vivado综合生成bitstream,并在Vitis环境中更新硬件规格、编译及调试。步骤包括从Vivado导出.xsa文件,Vitis中的硬件平台下载,以及ILA调试过程,最后是直接运行C语言代码的步骤。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?