HIGHLIGHT:

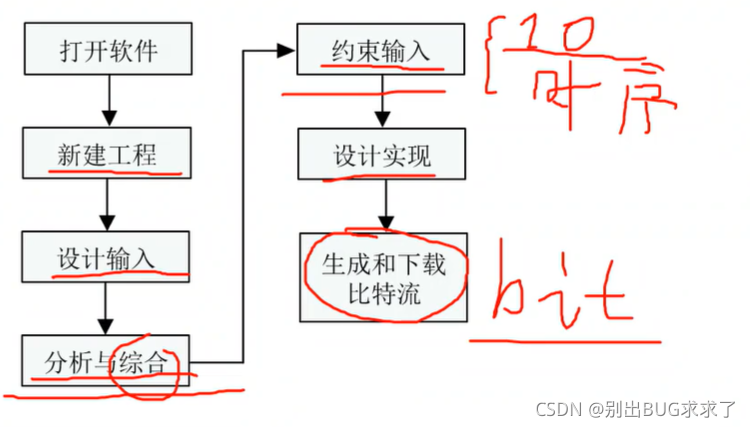

- vivado设计流程:

note:

分析与综合 和 约束输入 可以调换顺序

【基于zynq的卷积神经网络加速器设计】(一)熟悉vivado和fpga开发流程:使用Vivado硬件调试烧写hello-world led闪烁程序实现及vivado软件仿真

一、硬件调试

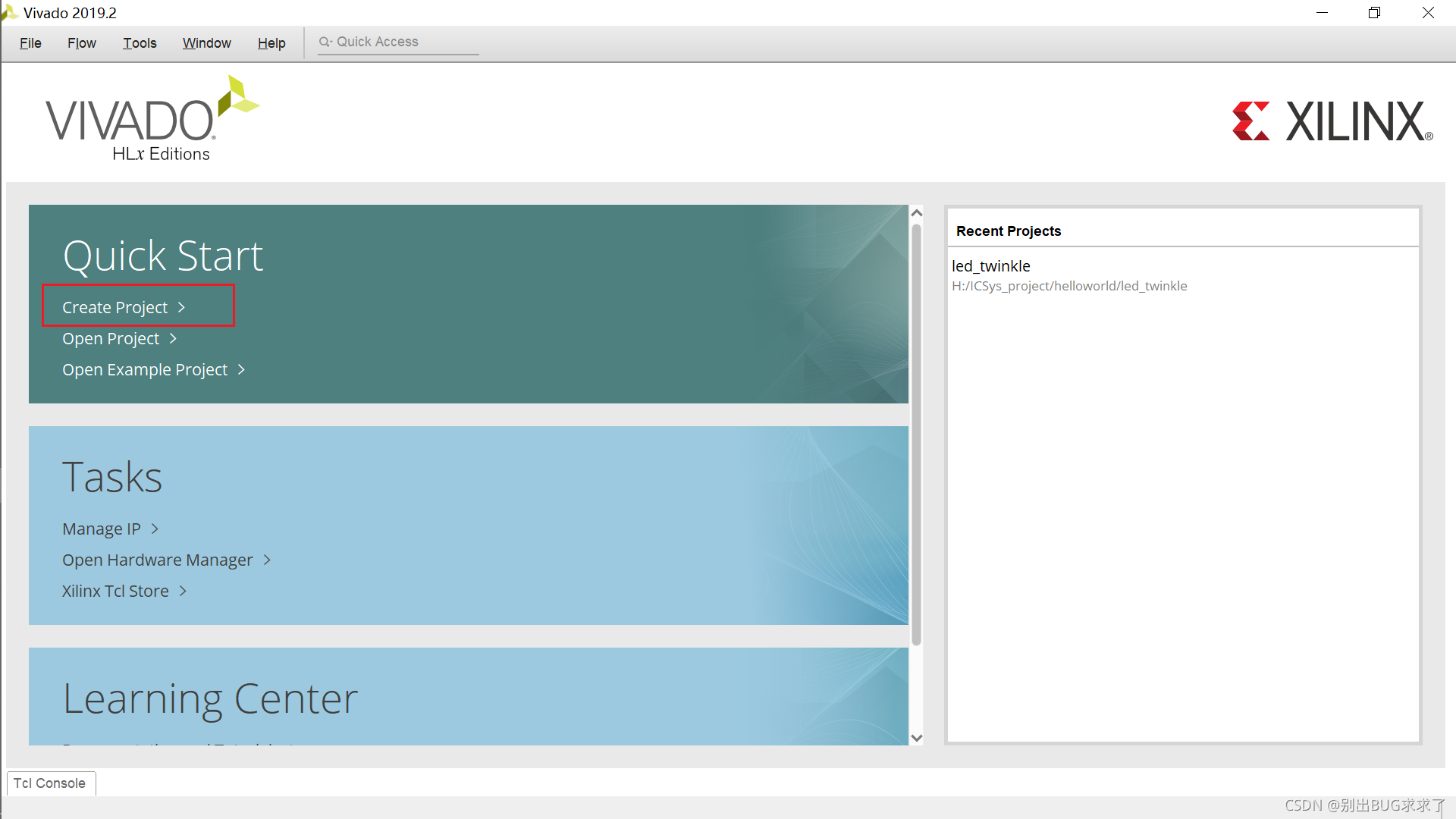

(一)新建工程

- new project

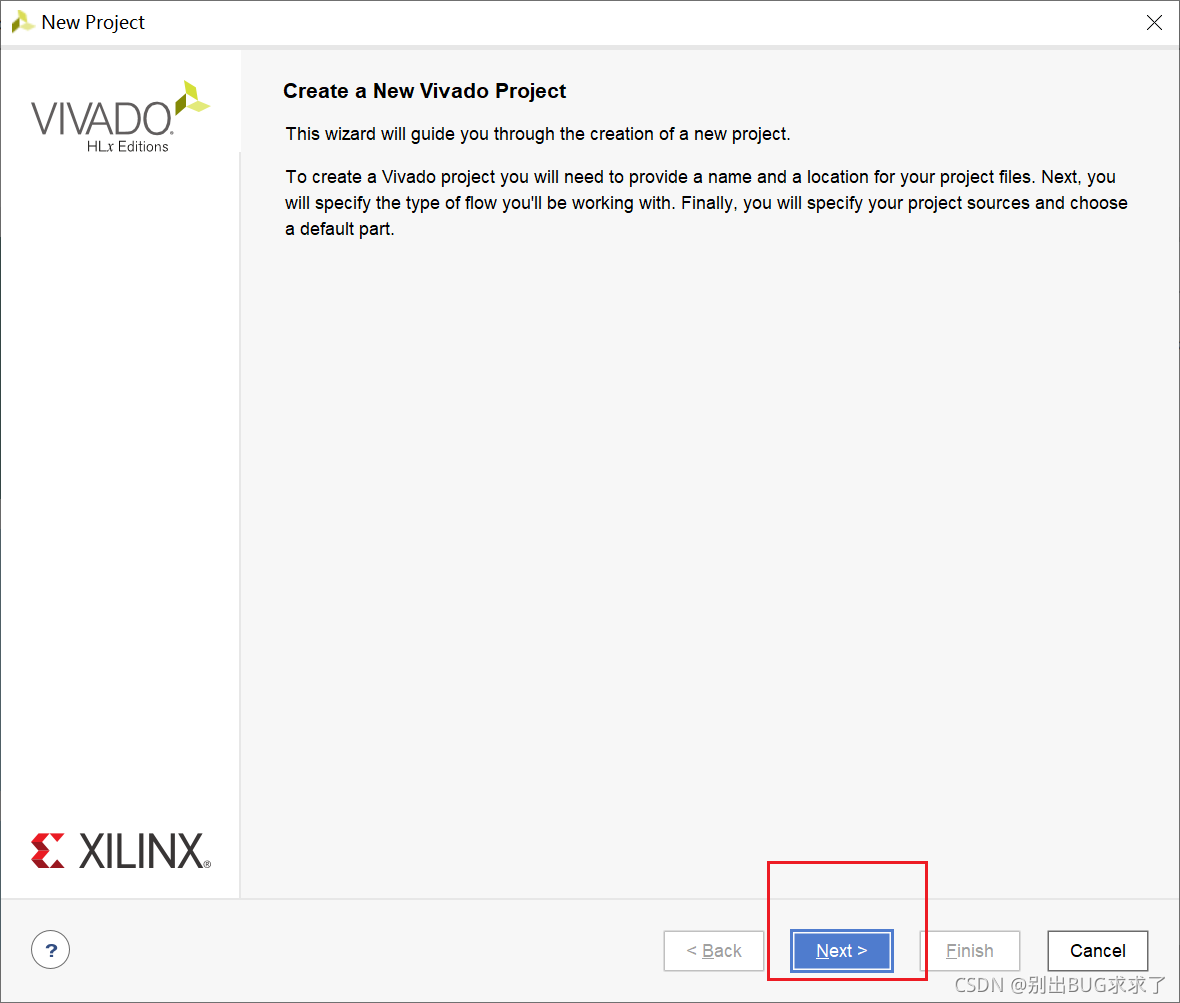

- next

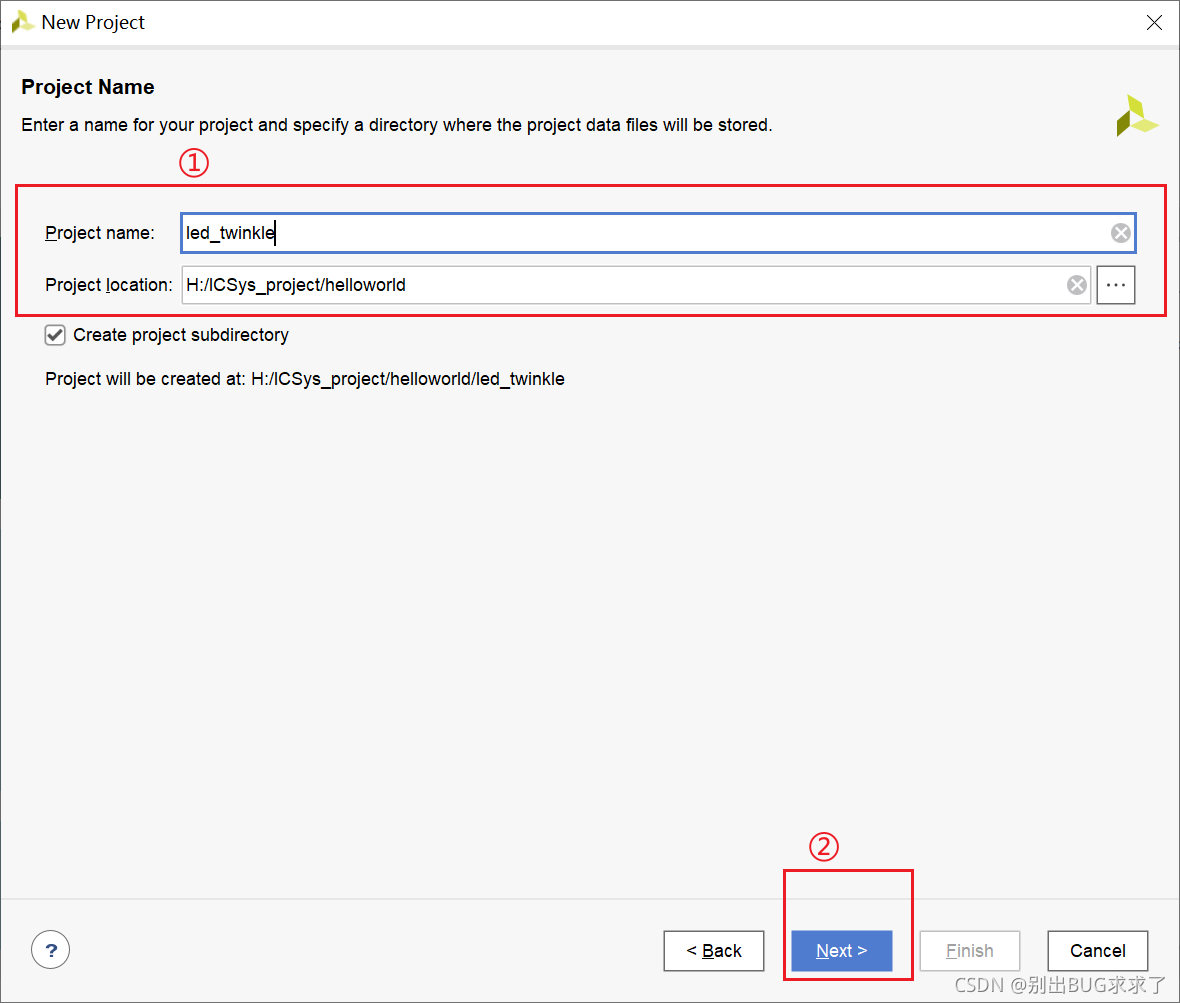

- 编辑,然后next

- 勾选创建完工程再添加文件

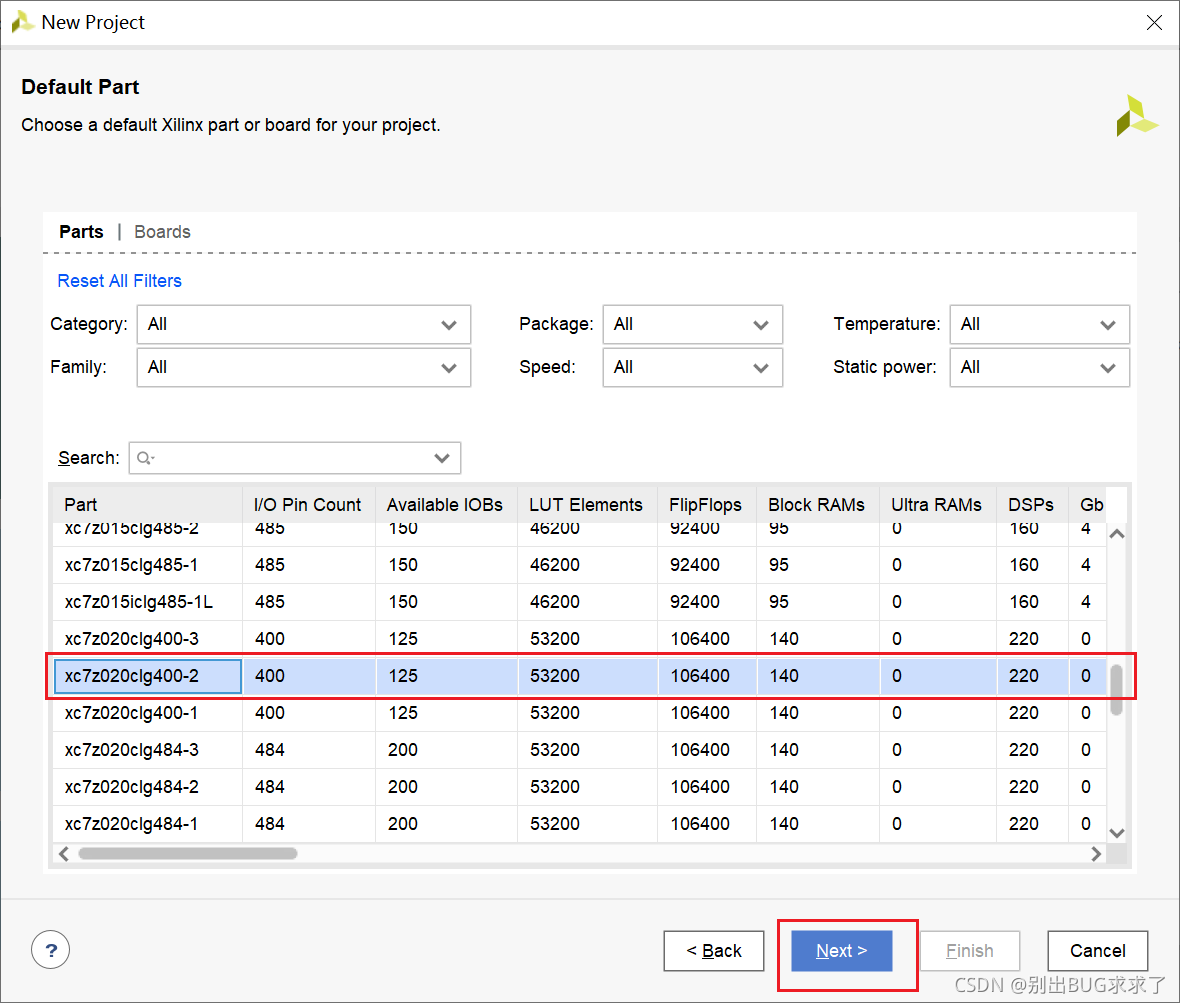

- 根据实际情况选择型号

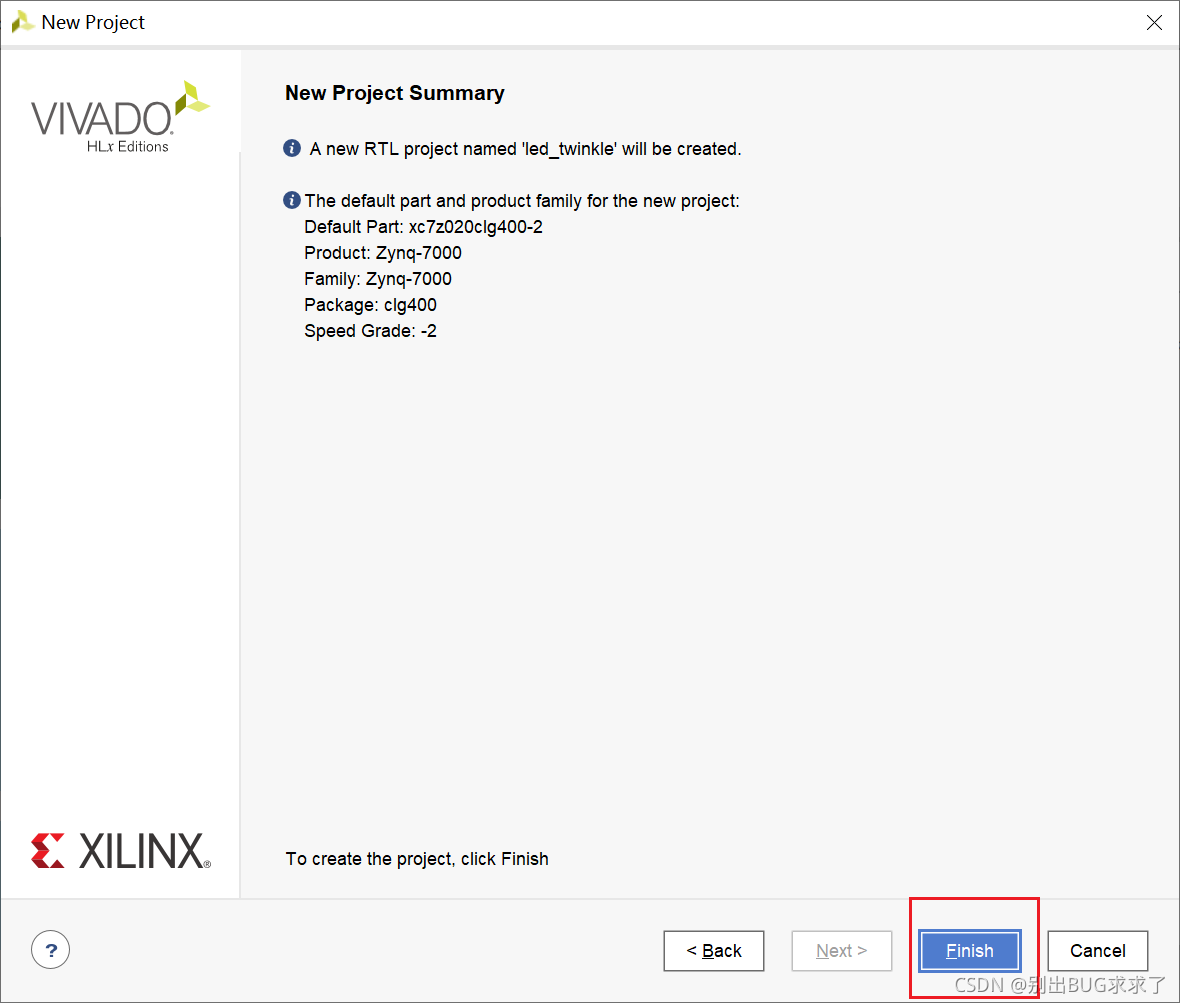

- finish

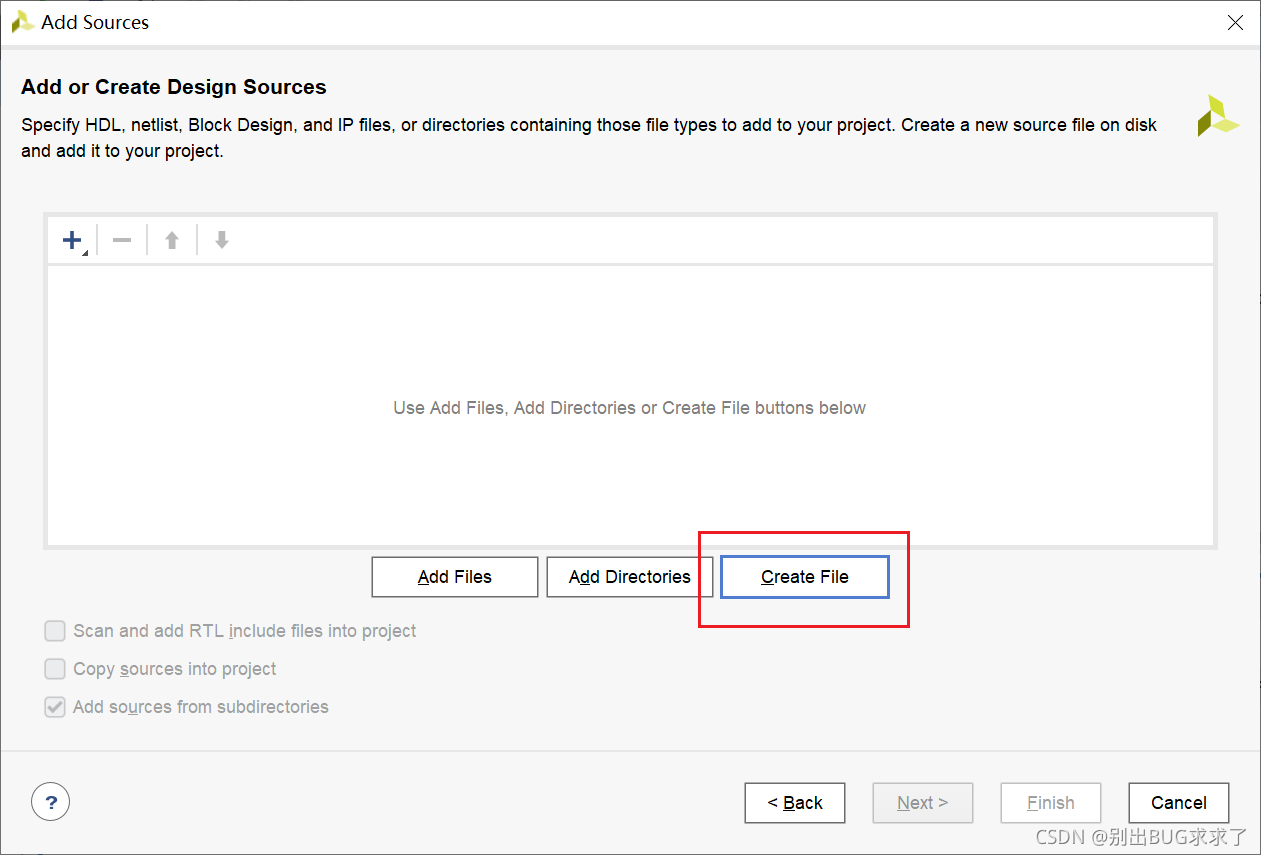

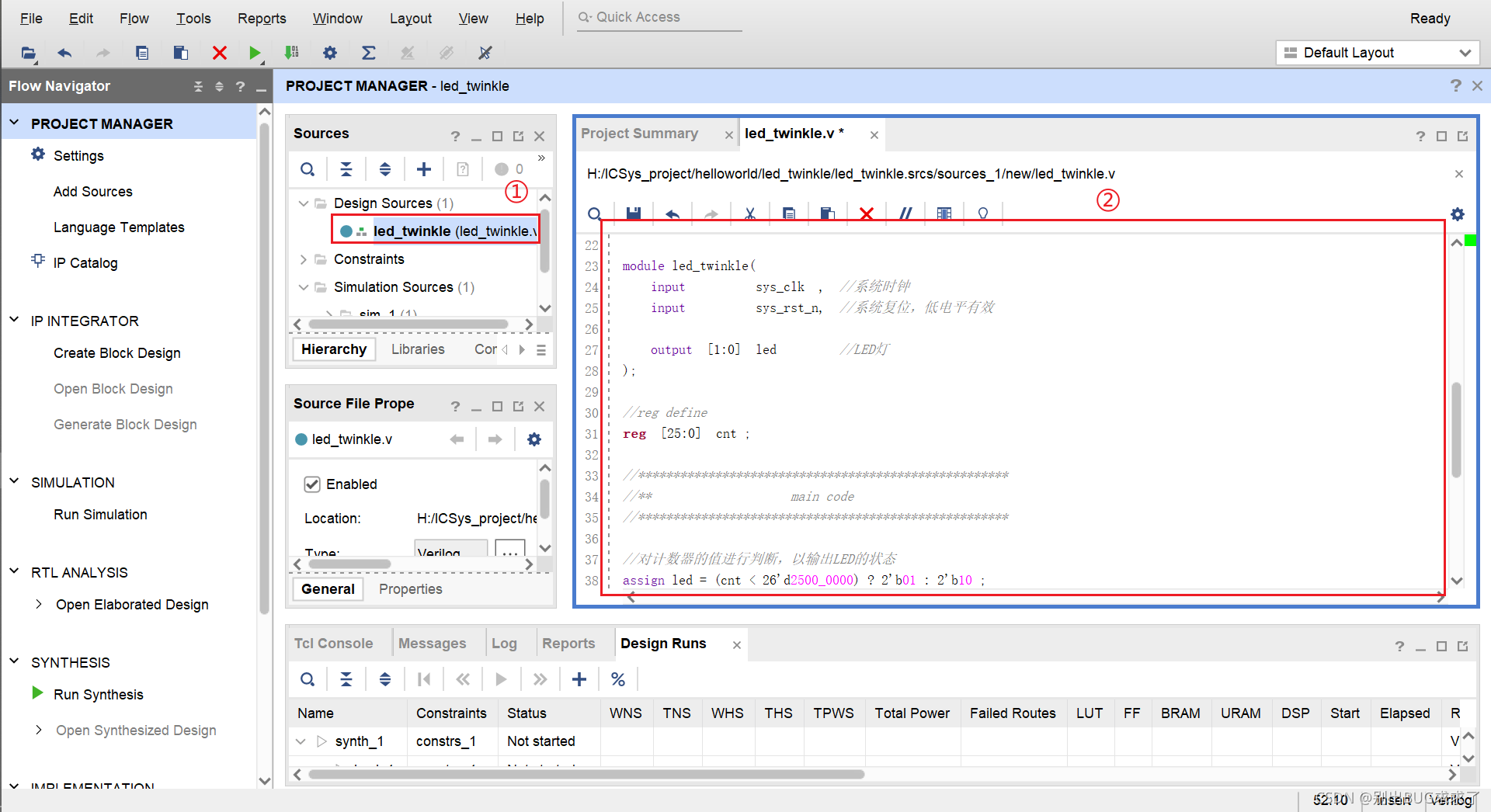

(二)设计输入

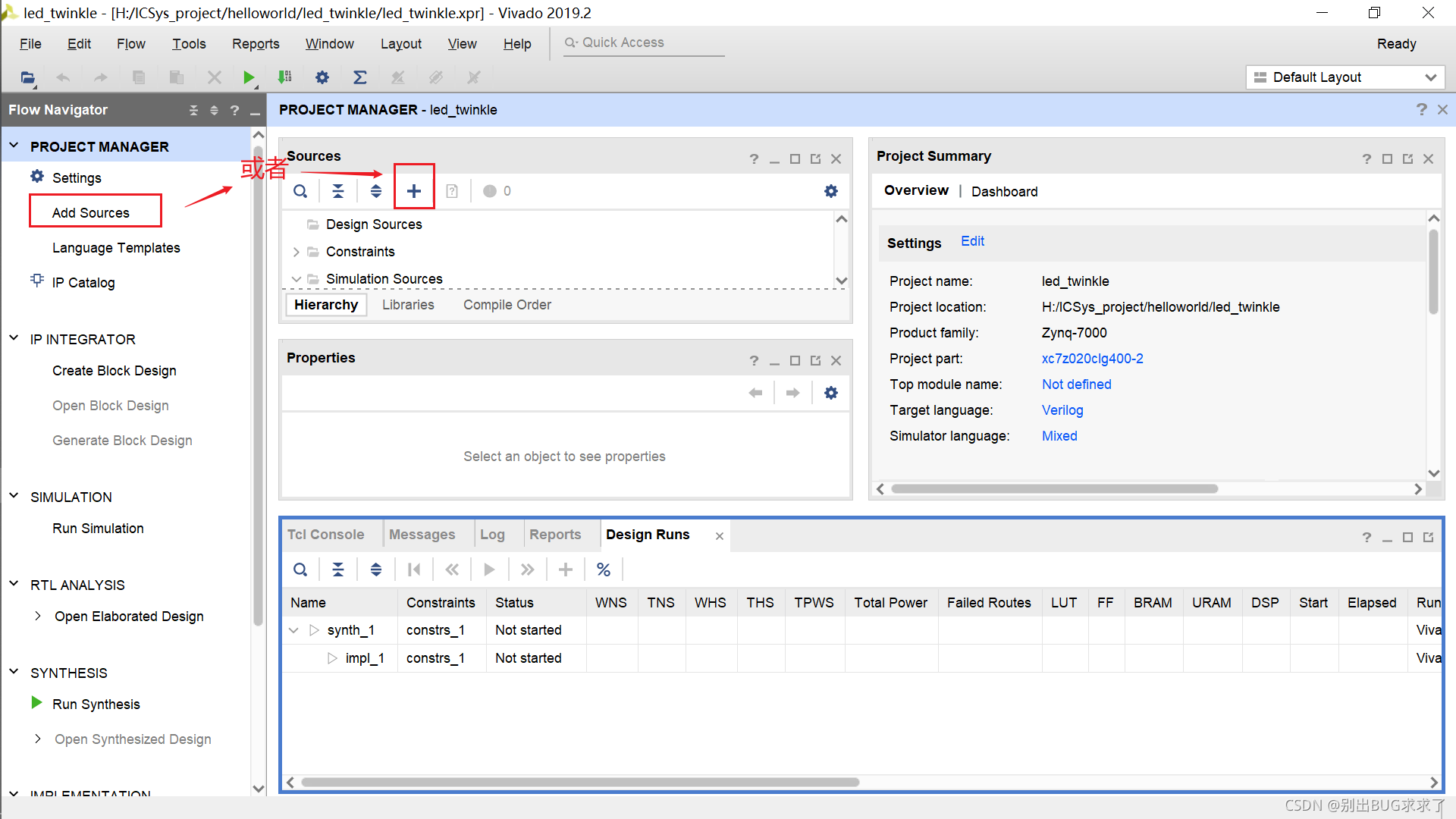

- add source

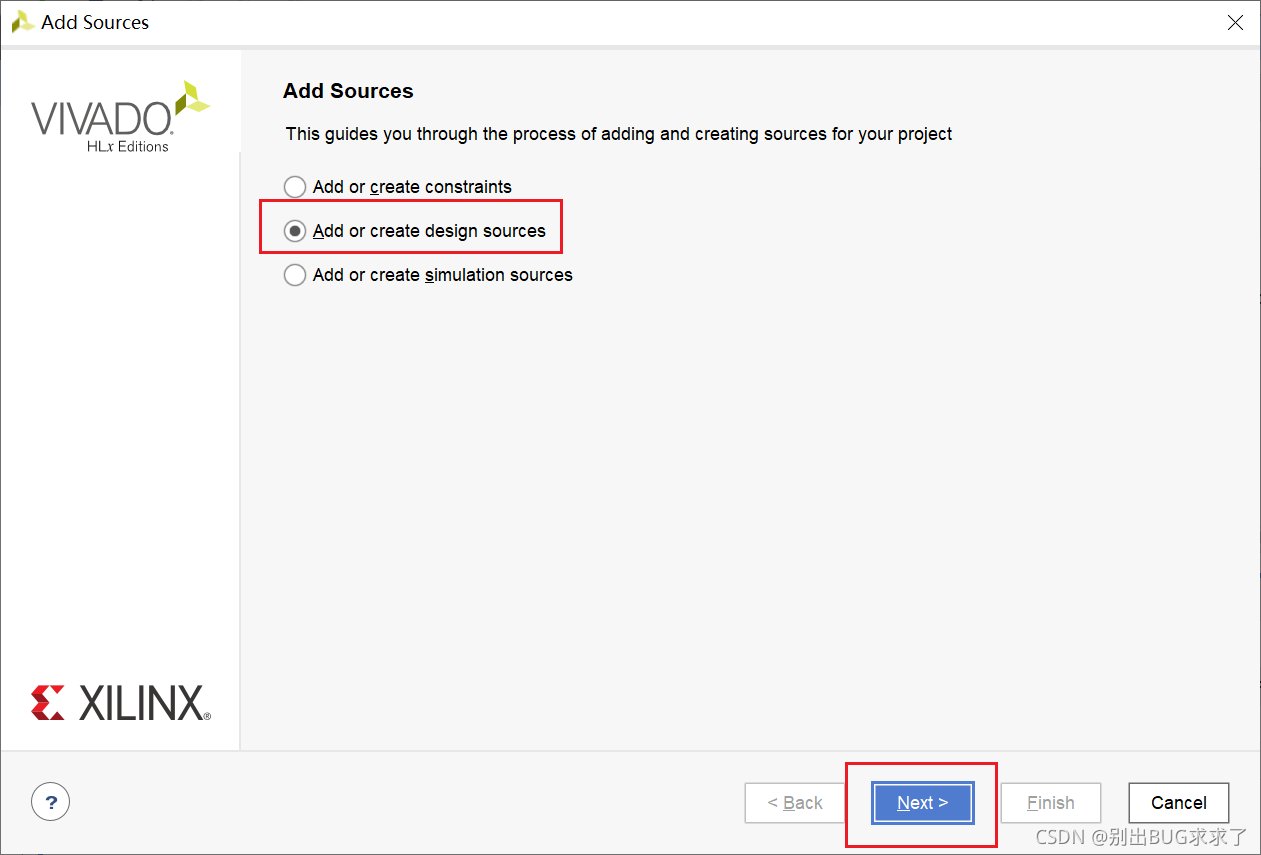

- create design source

- create file

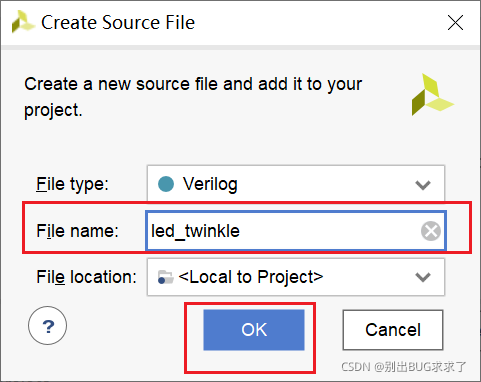

- 命名(一般顶层模块名和工程名保持一致)、ok

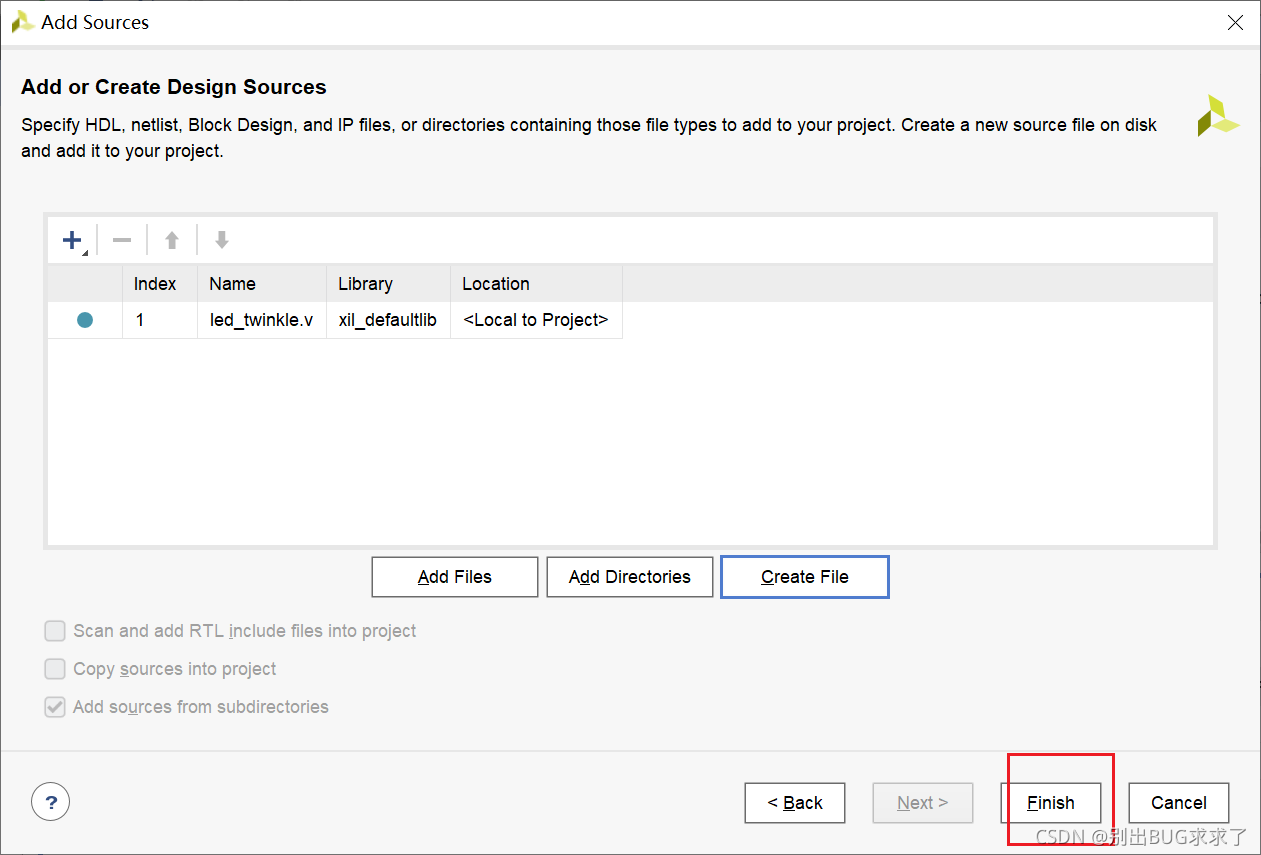

- finish

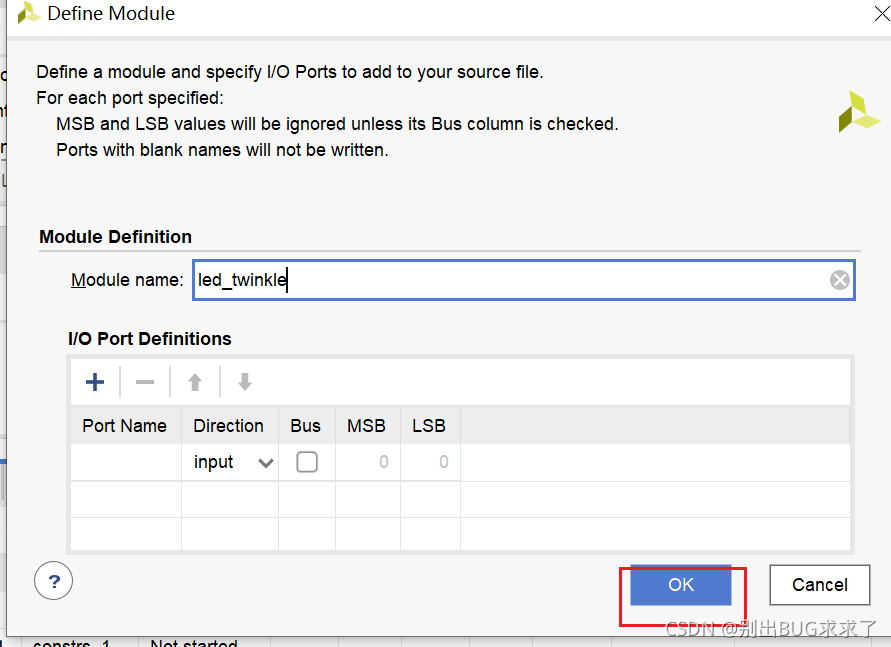

- 端口信号不做定义,点击ok

- 双击创建的.V文件,然后在代码编辑区域输入代码

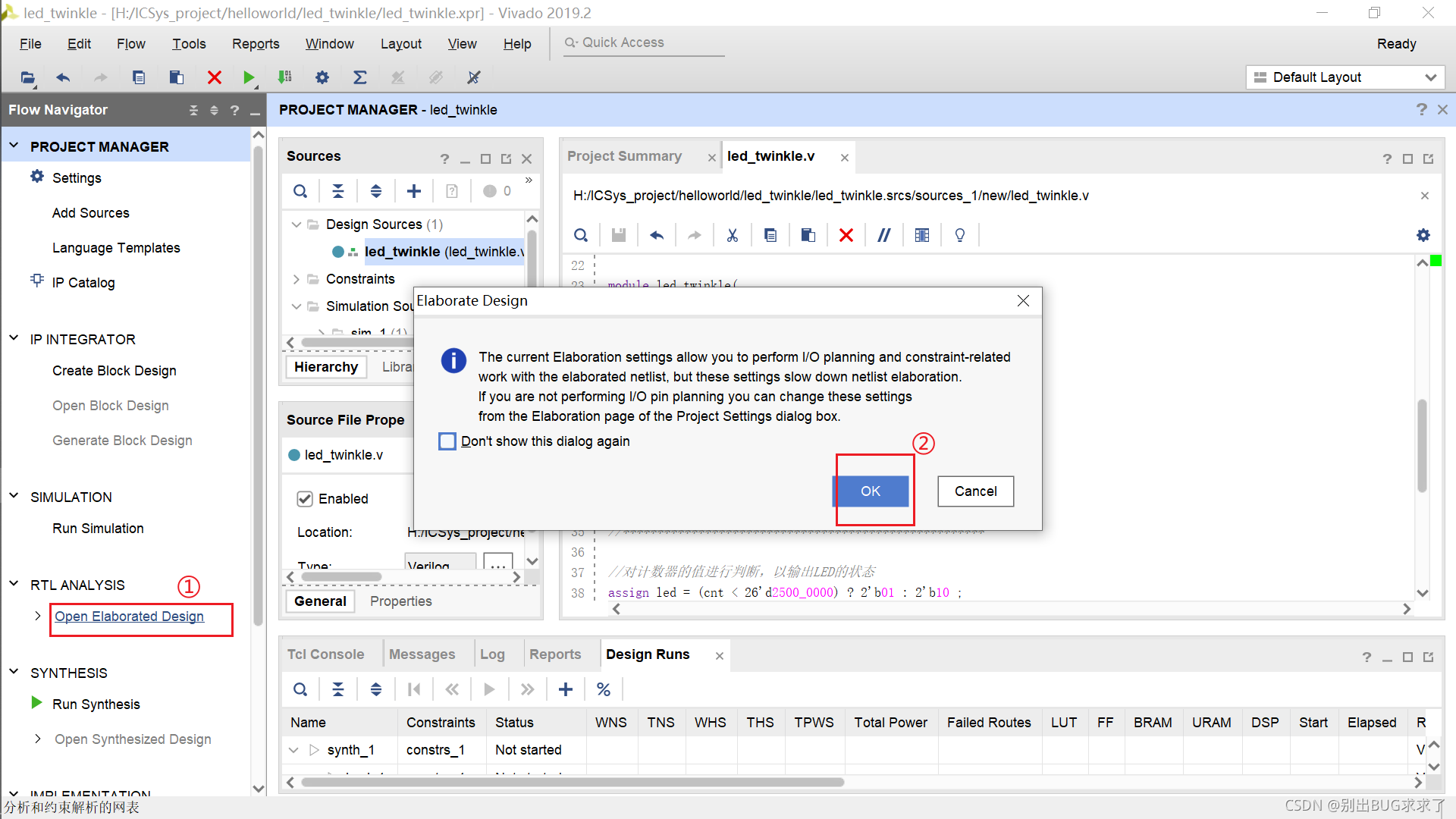

(三)分析

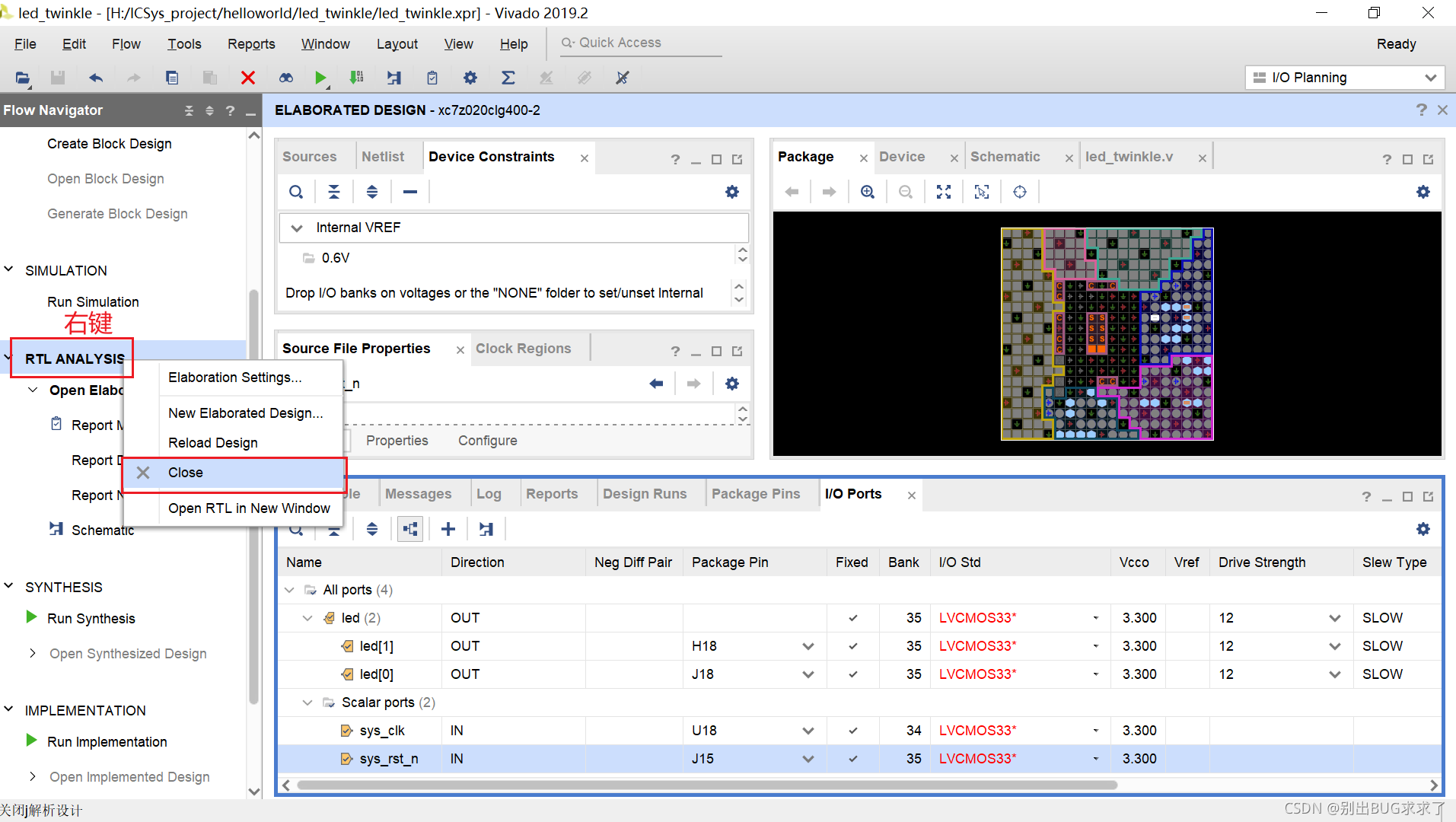

- open elaborated design

verilog转换rtl

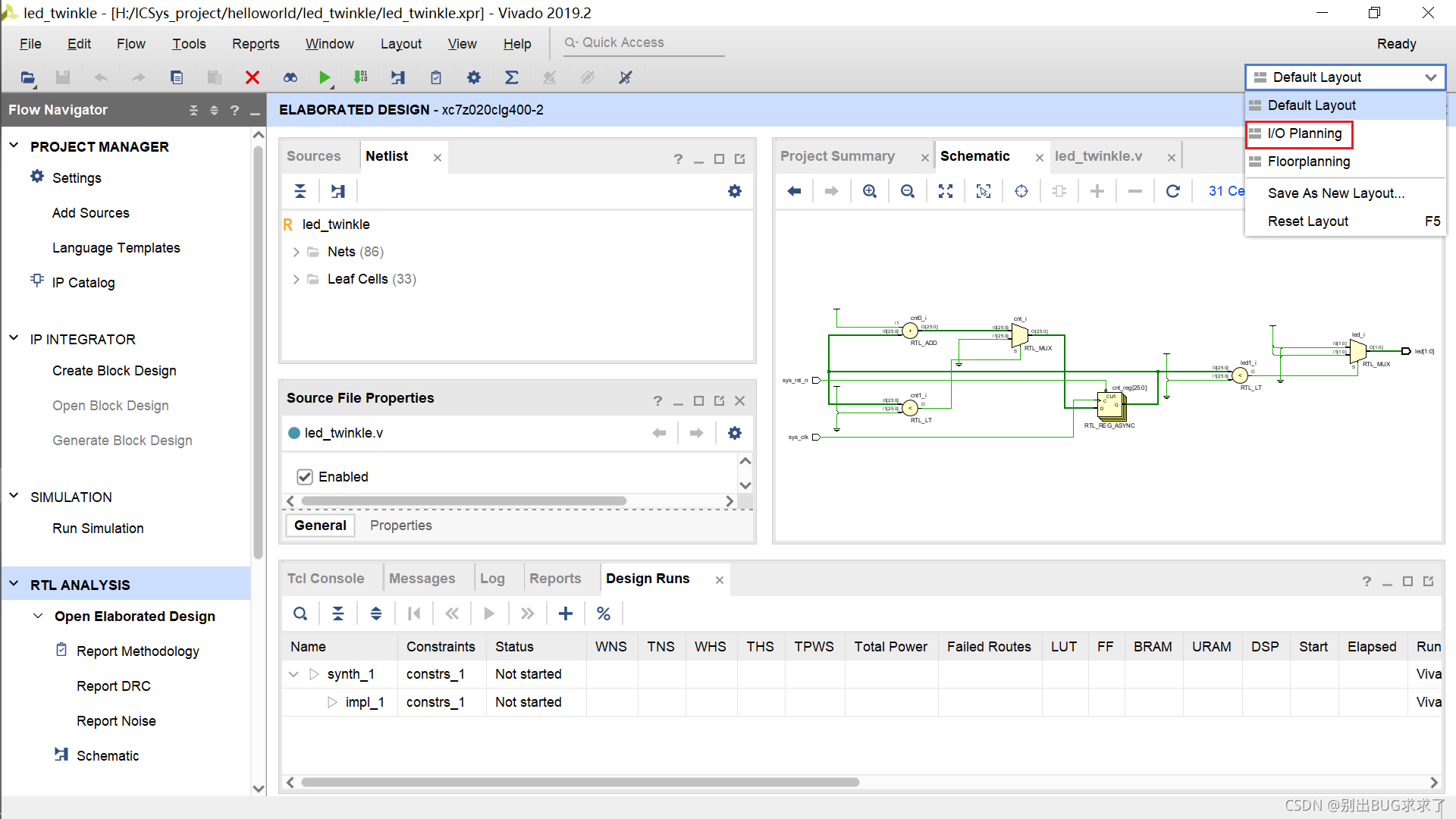

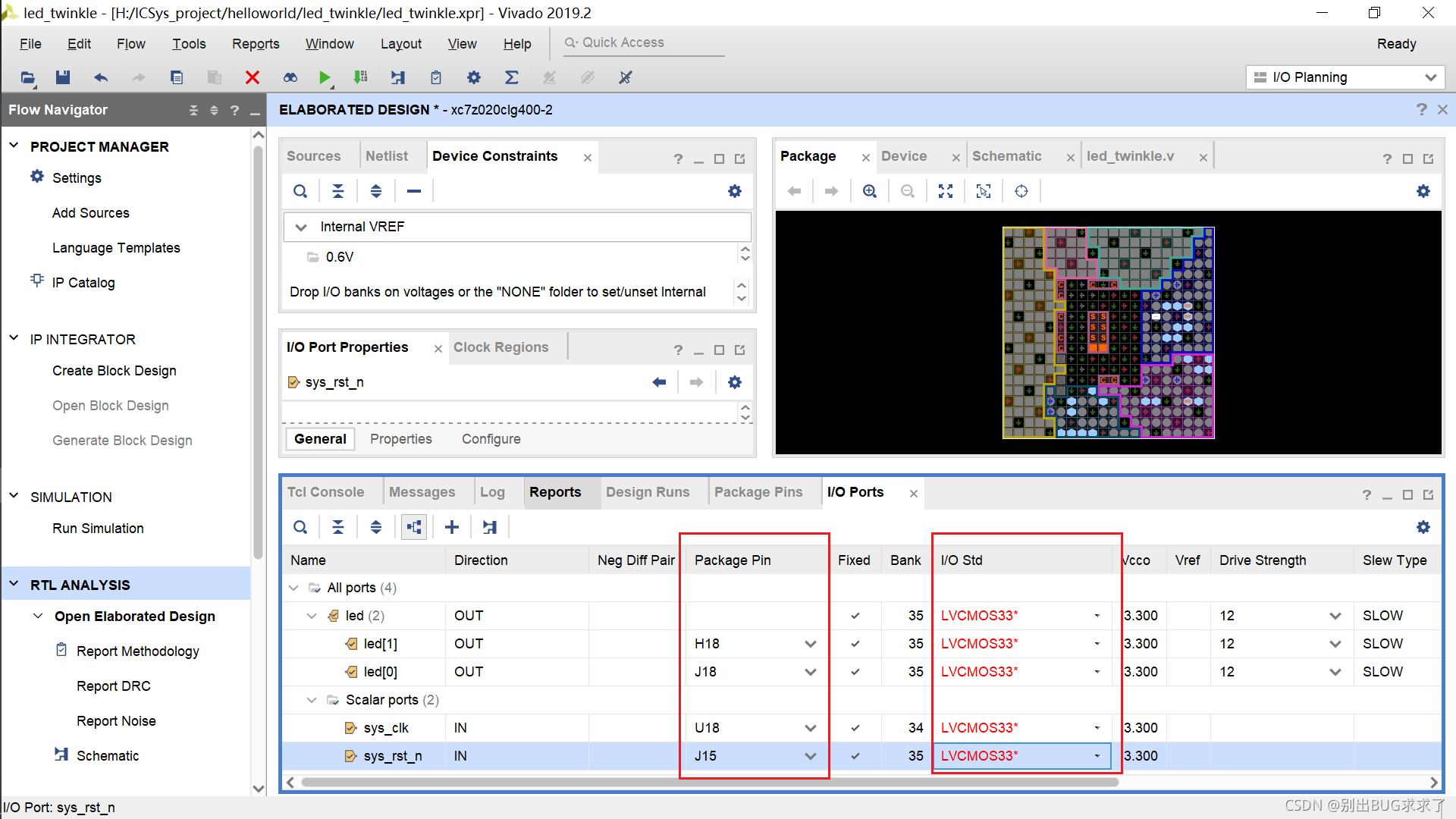

(四)约束输入

- io planing

- 选择管脚和管脚电平

自行在自己开发板对应的原理图手册查找

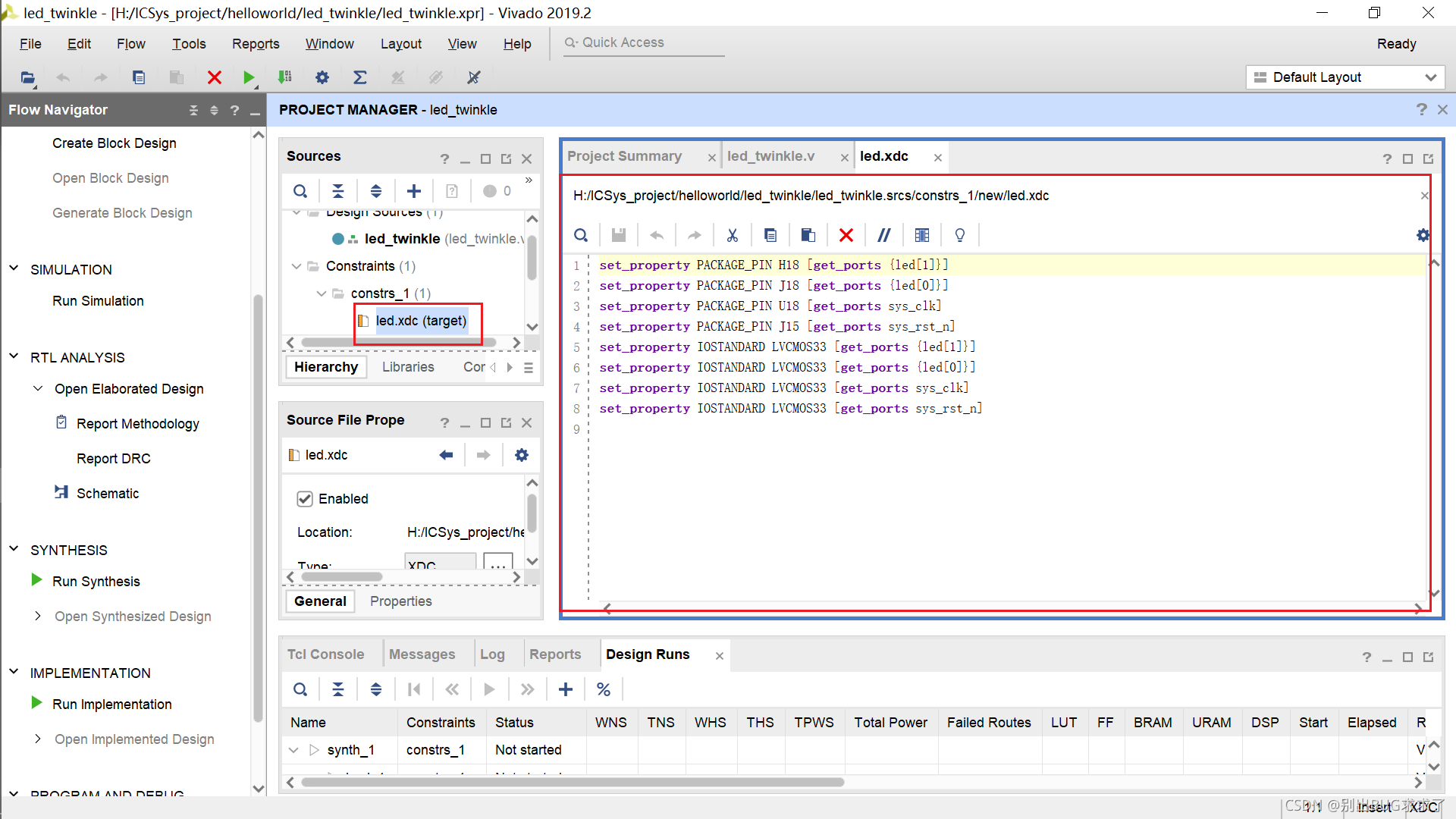

- 按下ctri+s——>起名——>ok

- 右键关闭

- 打开xdc文件

这个文件可以做IO约束 或者 时序约束

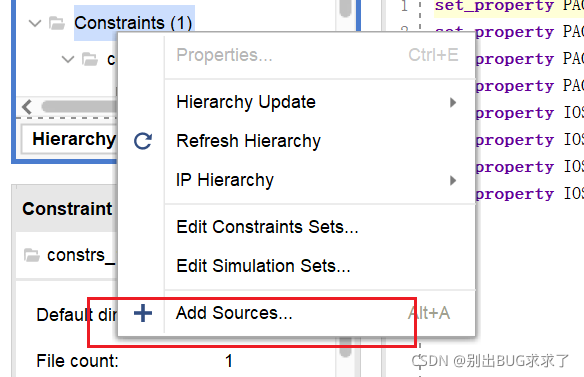

note:

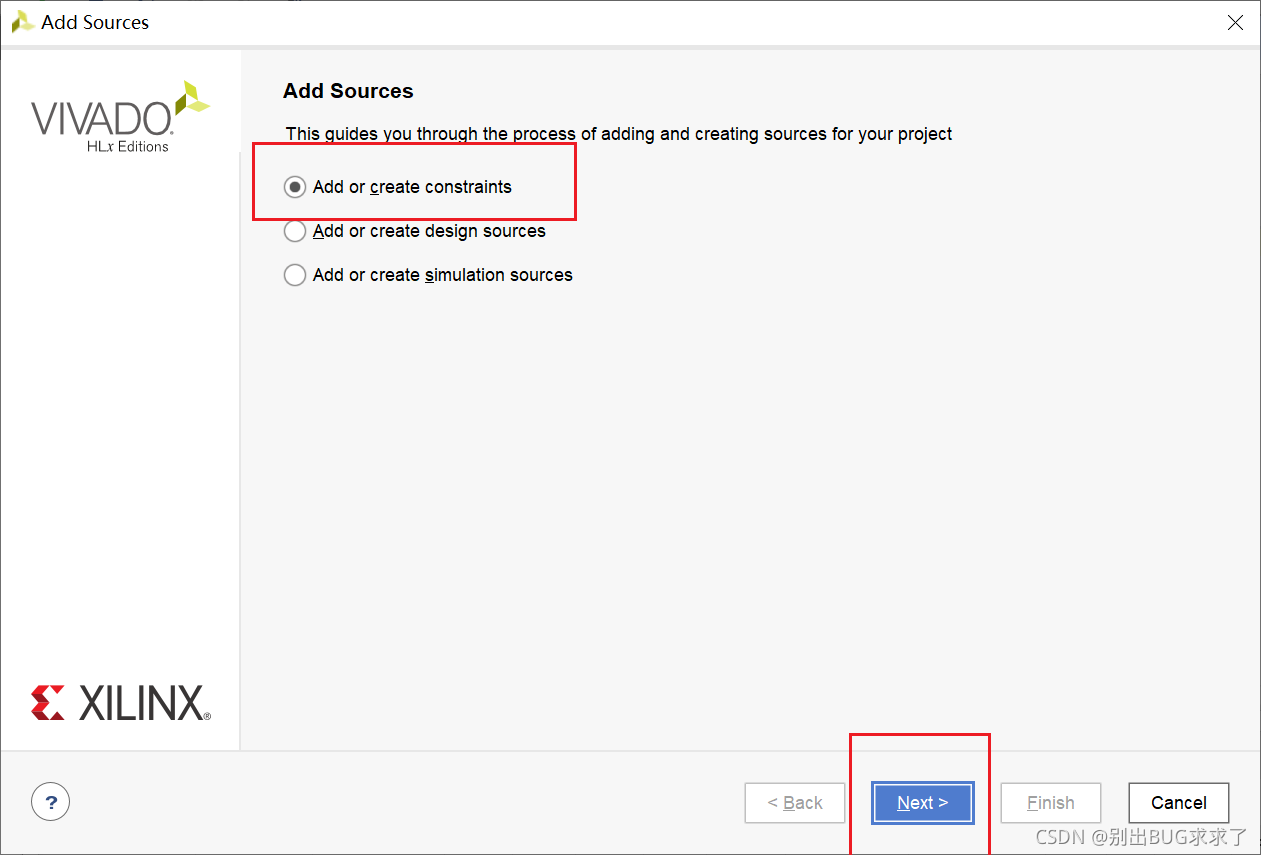

约束这里可以自己添加约束文件

(五)综合、实现、生成比特流

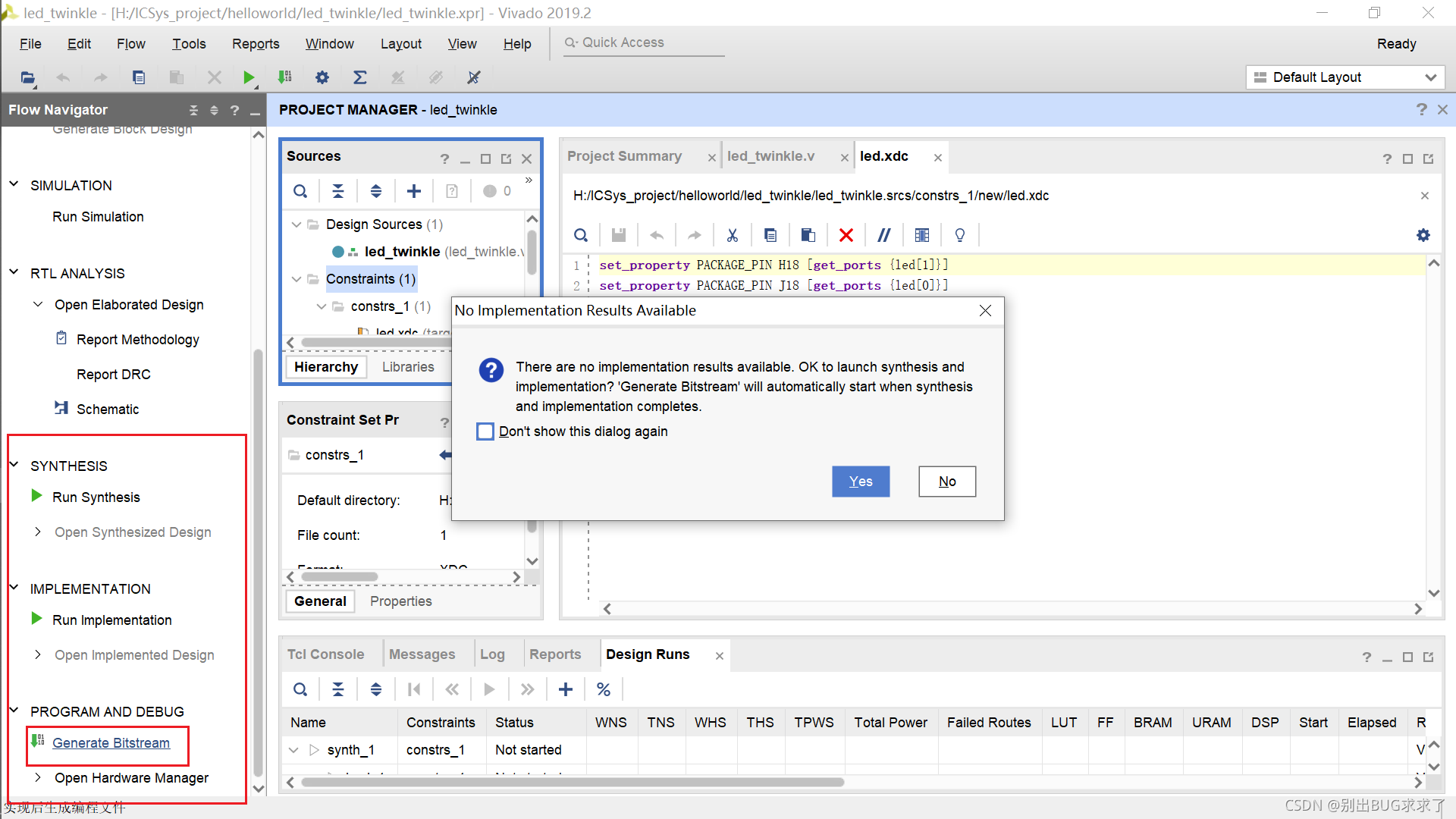

-

点击generate bitstream

点击generate bitstream后,vivado会自动跑综合和实现。提示框点击yes即可

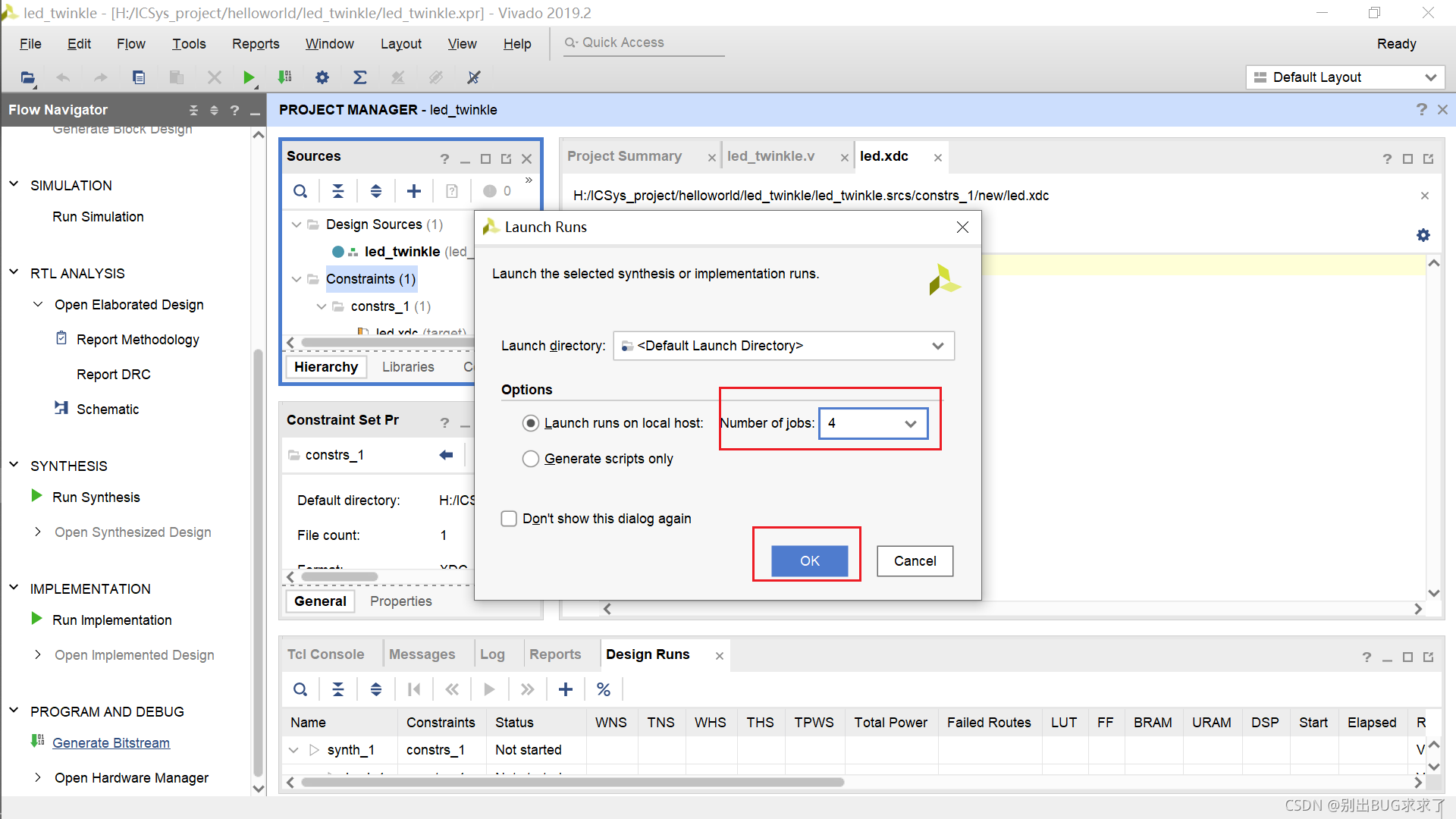

-

选择跑的时候运行的处理器核心数

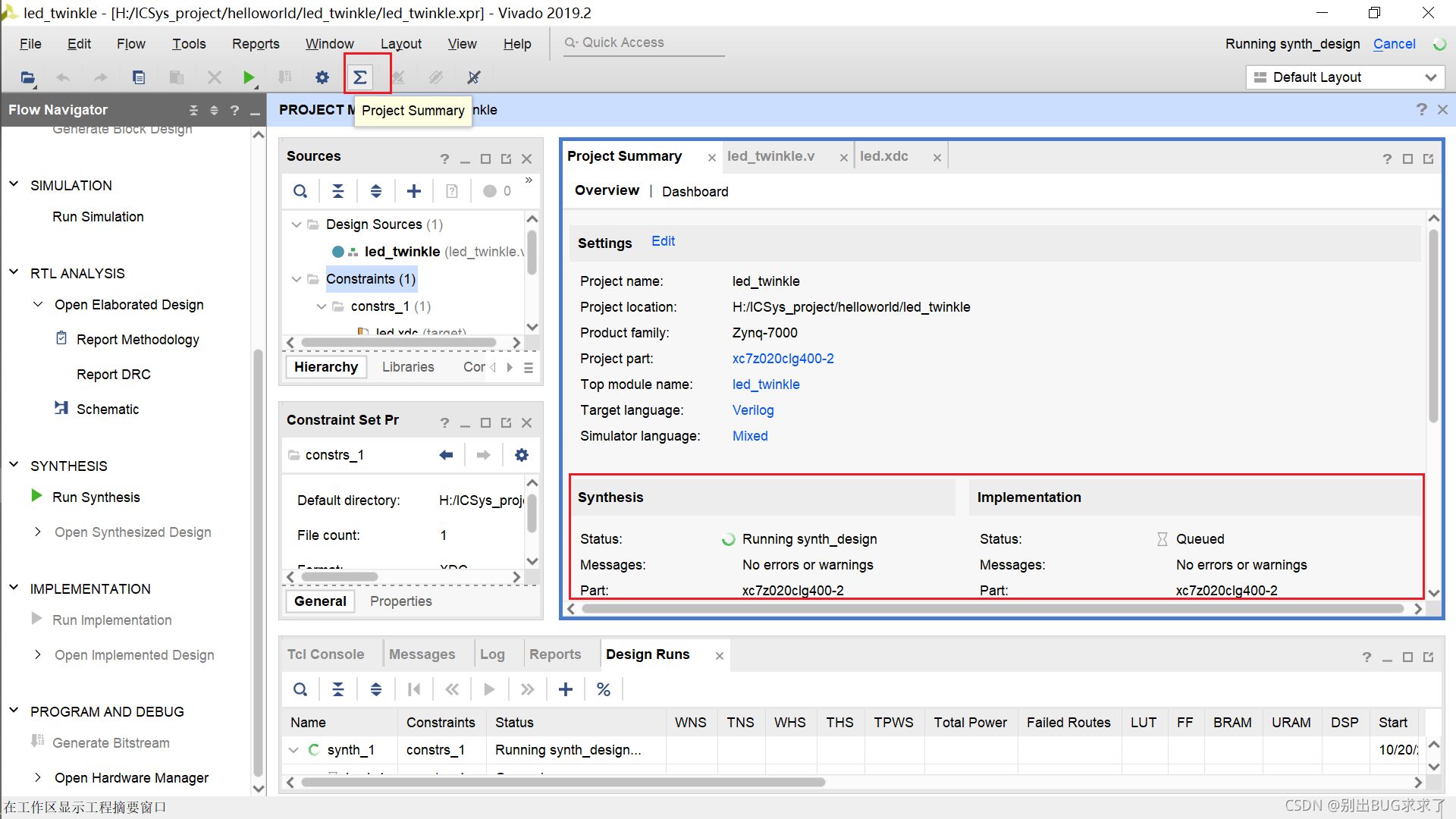

-

可以点击project summary查看进度

图中在综合

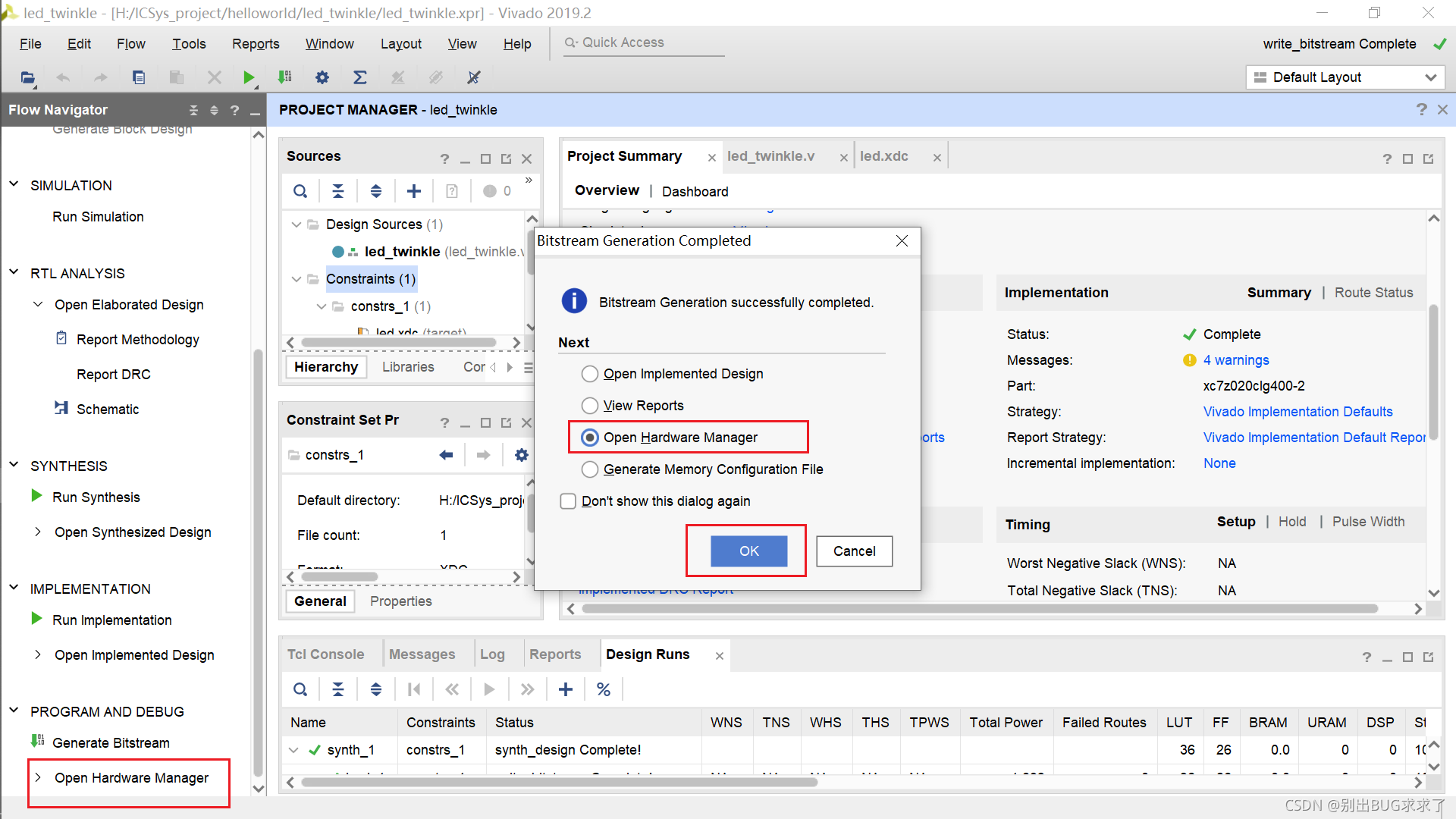

-

跑完了后会弹出以下框框

选择选项3再按ok,或者直接按左边的按钮open hardware manager

-

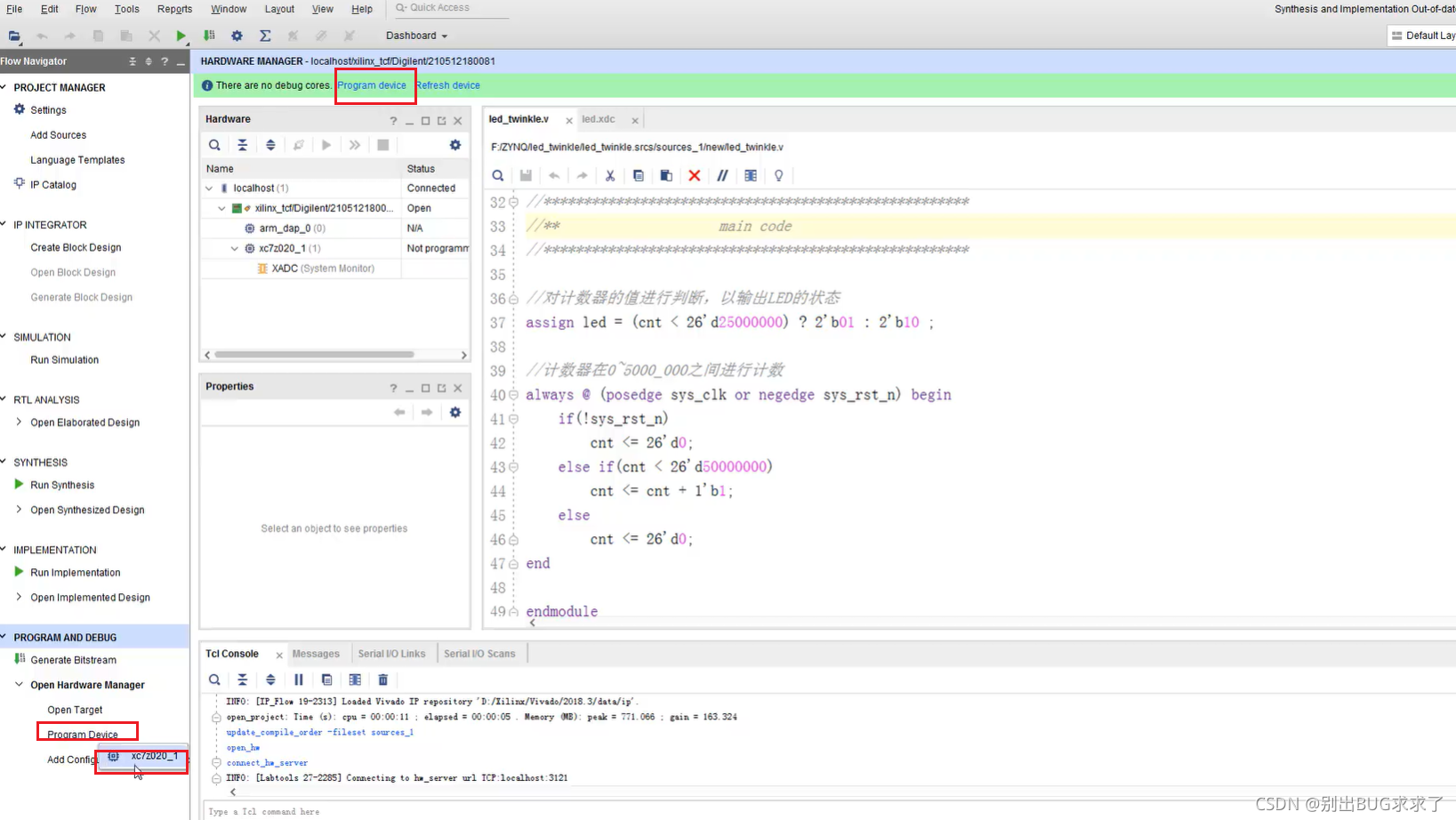

开发板上电连接电脑后选择program device 或者 左下角按钮

-

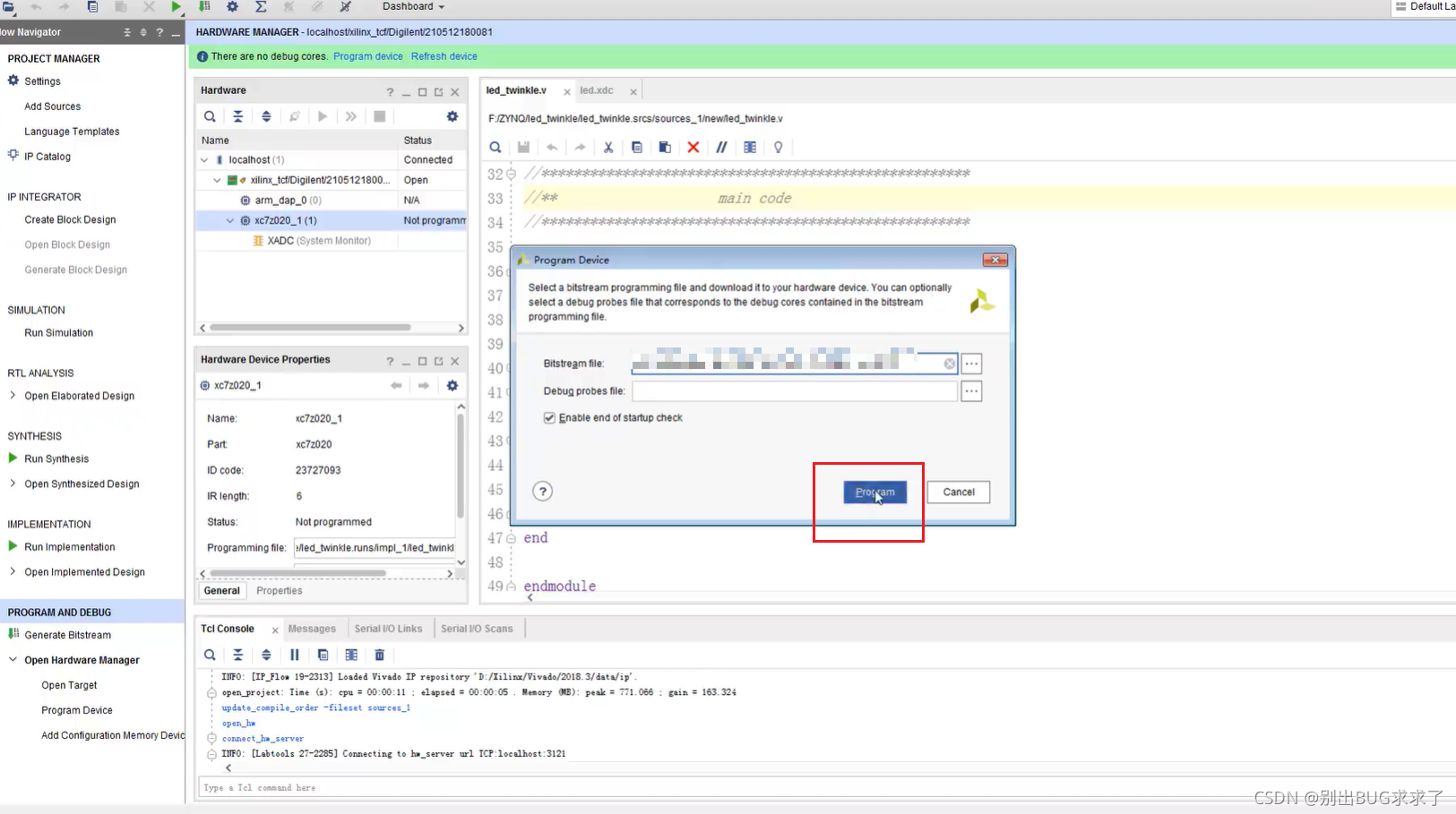

点击program

-

验证成功

二、软件仿真

(一)步骤

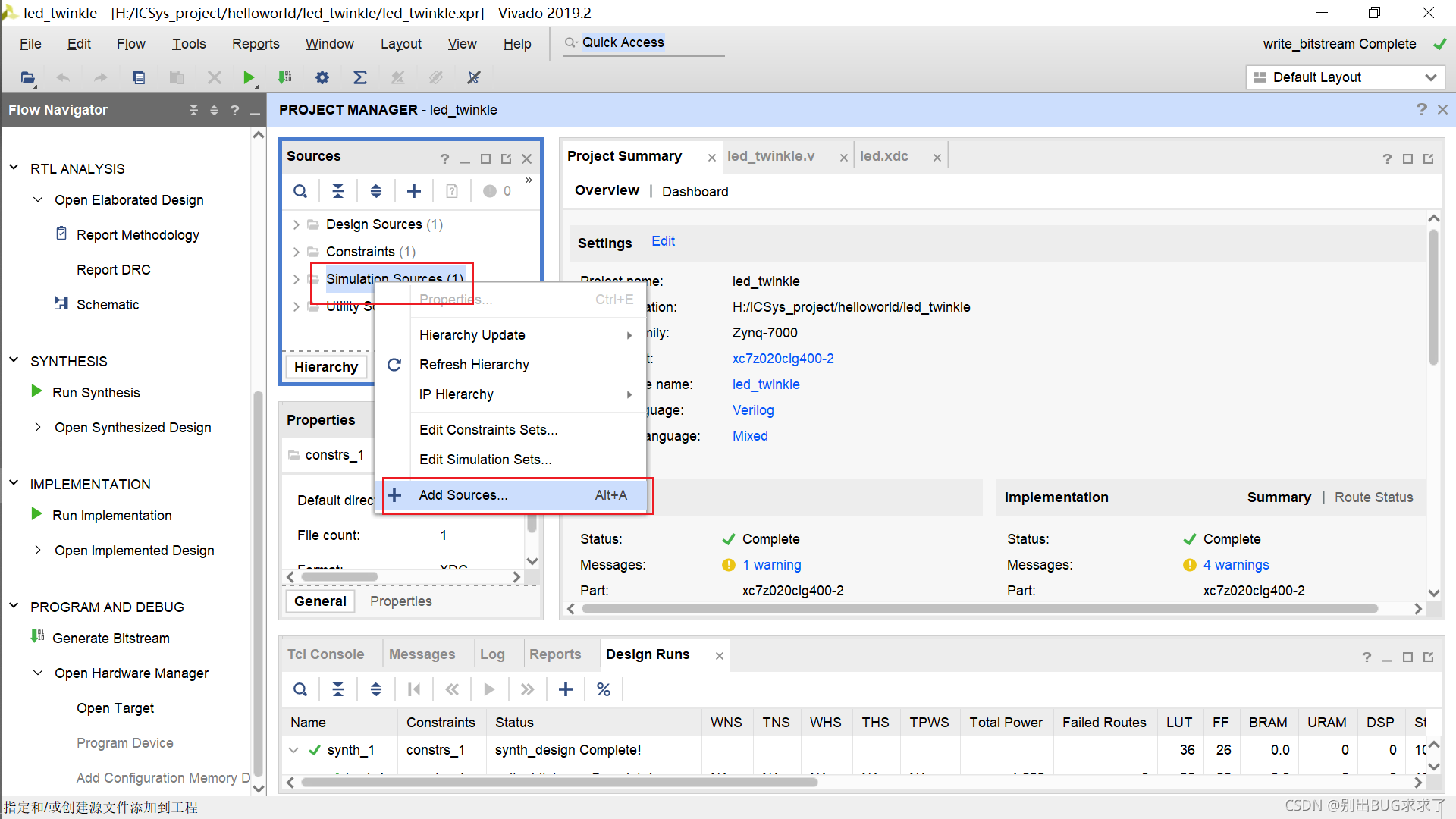

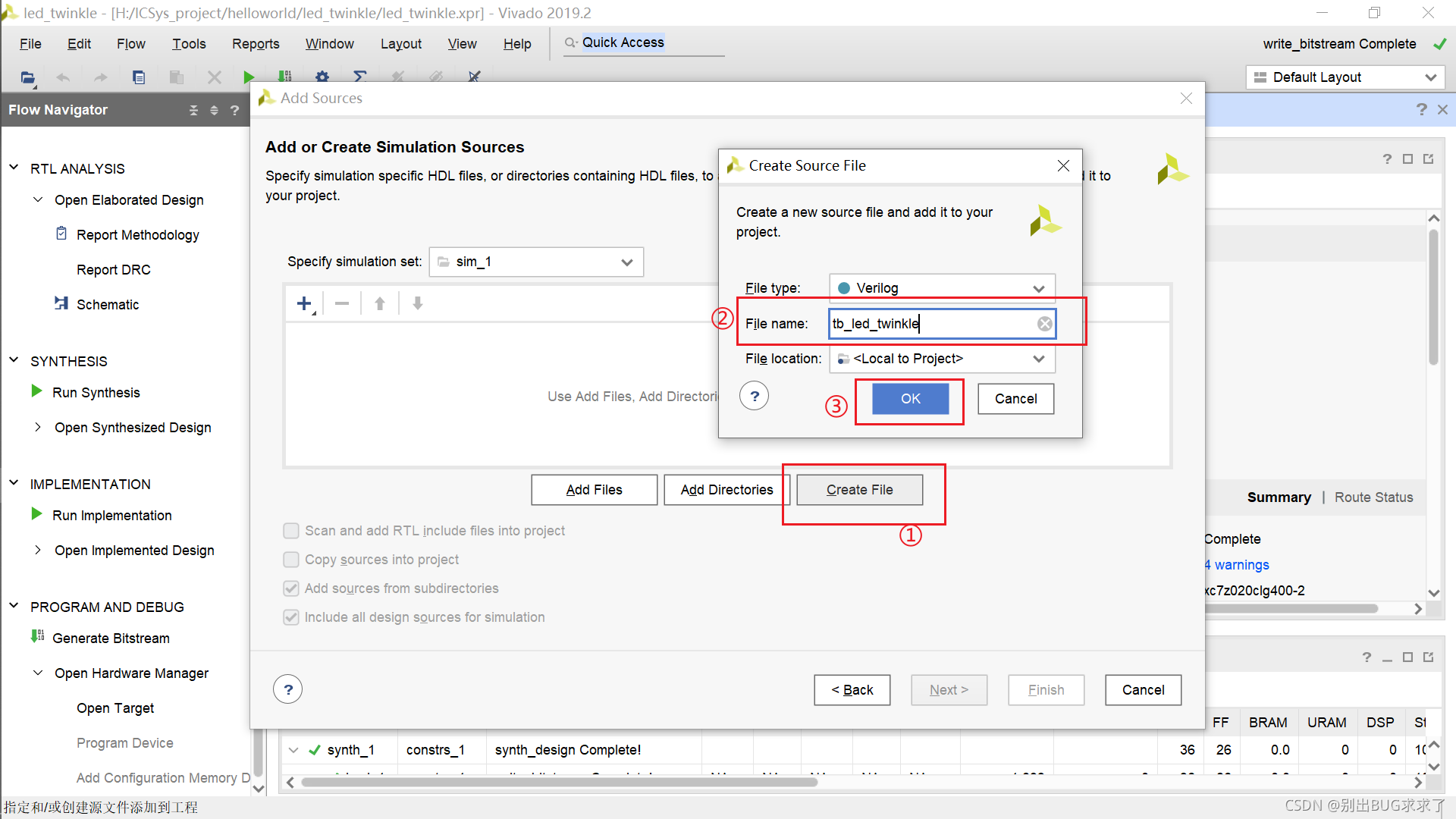

-

右键添加

创建激励文件(testbench文件)

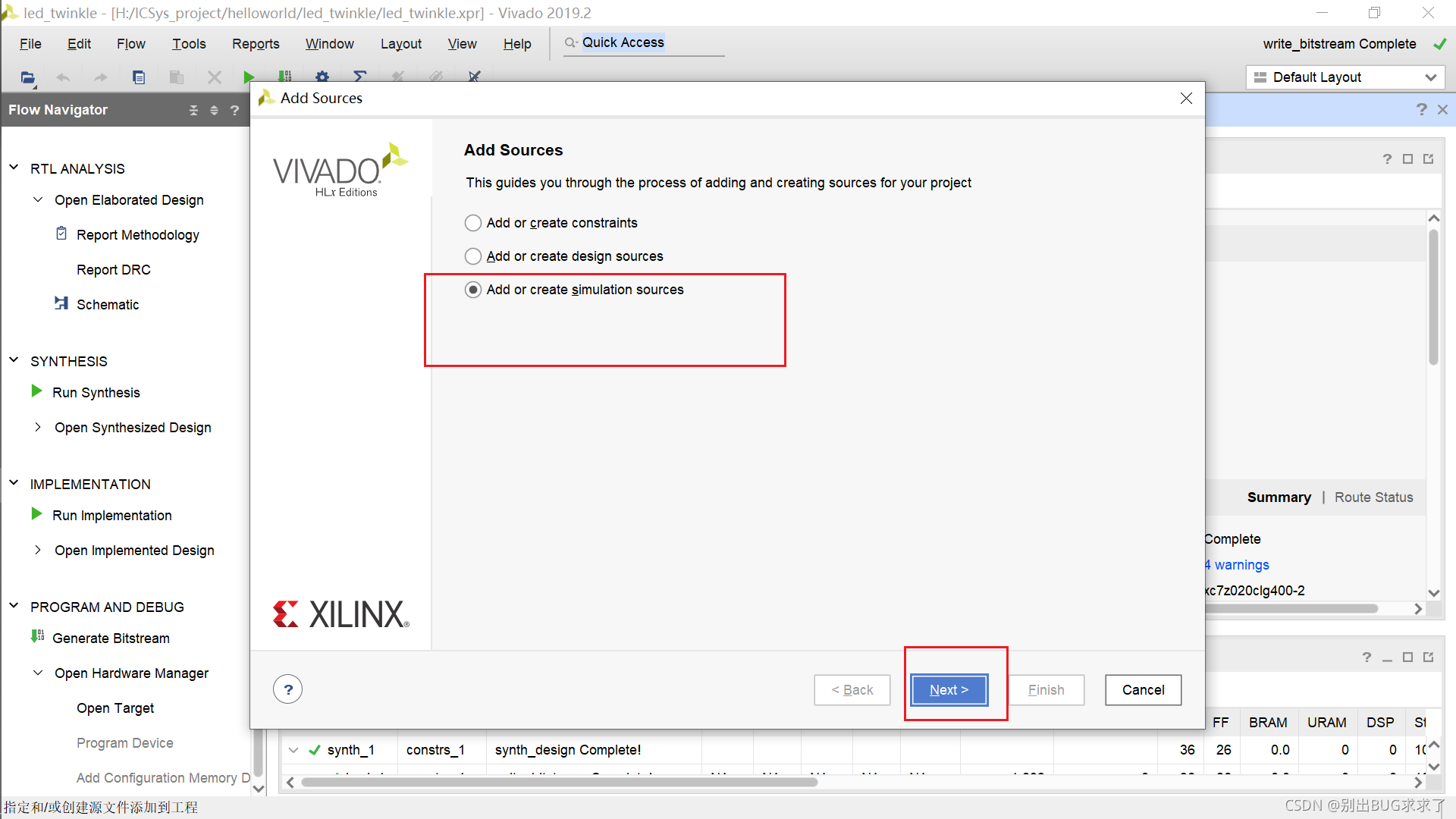

-

next

-

编辑名字

-

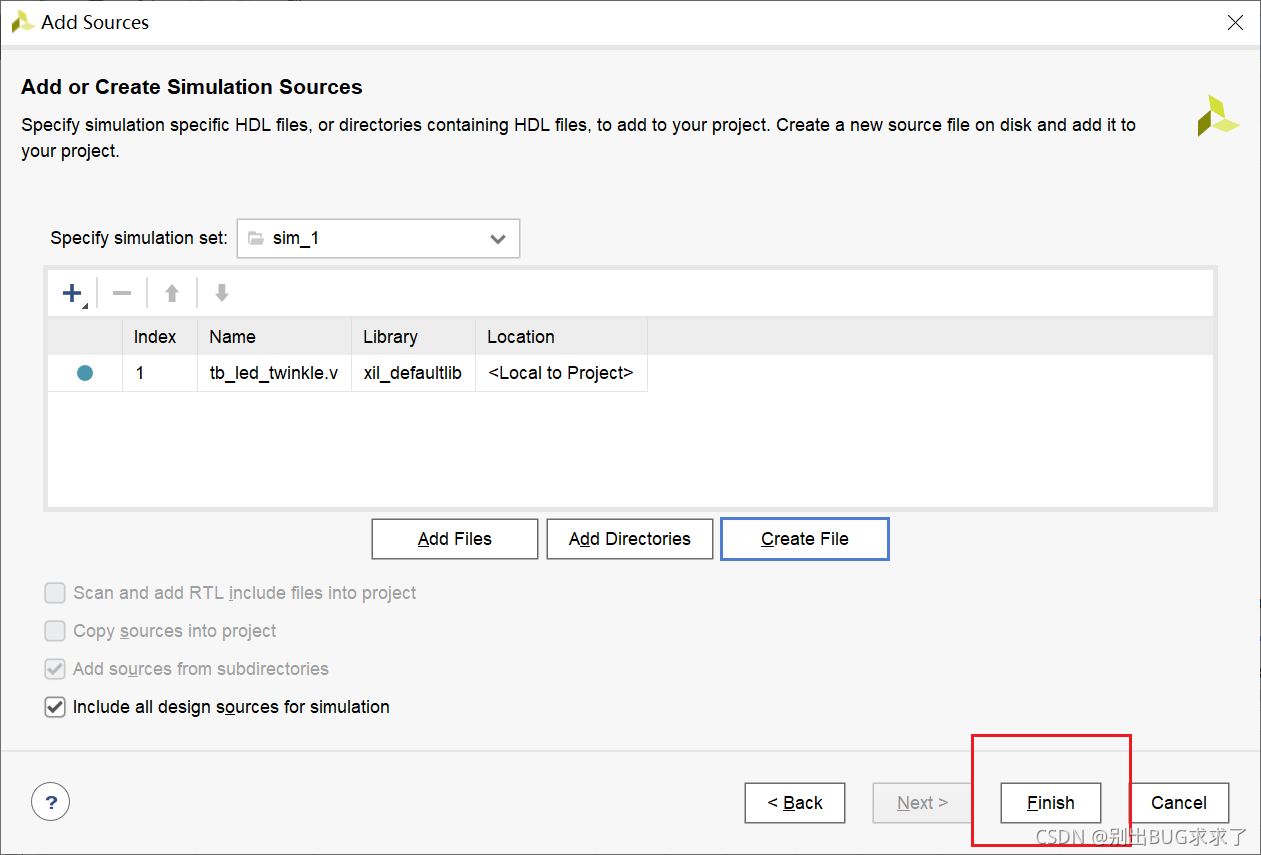

finish

-

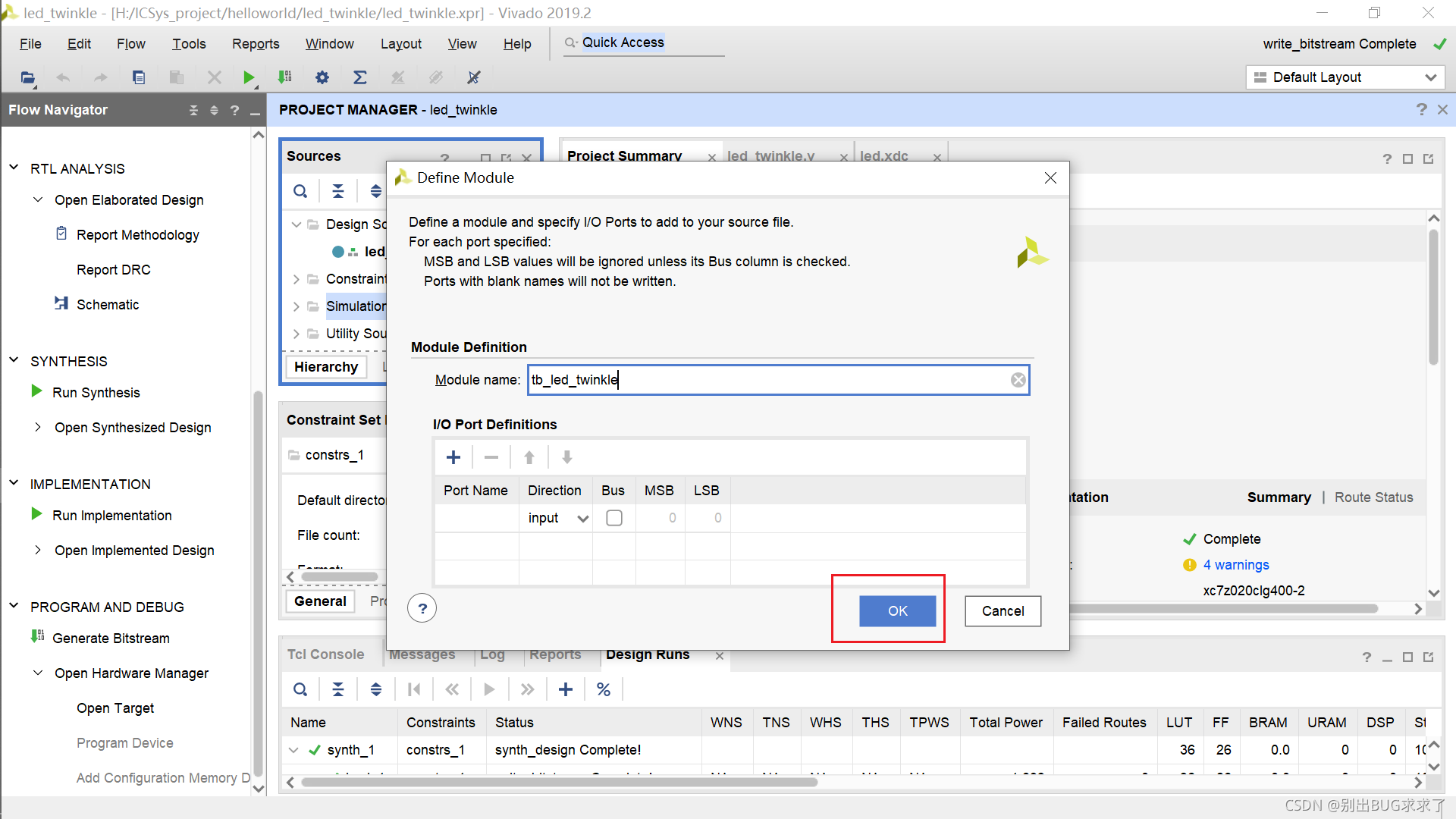

ok

-

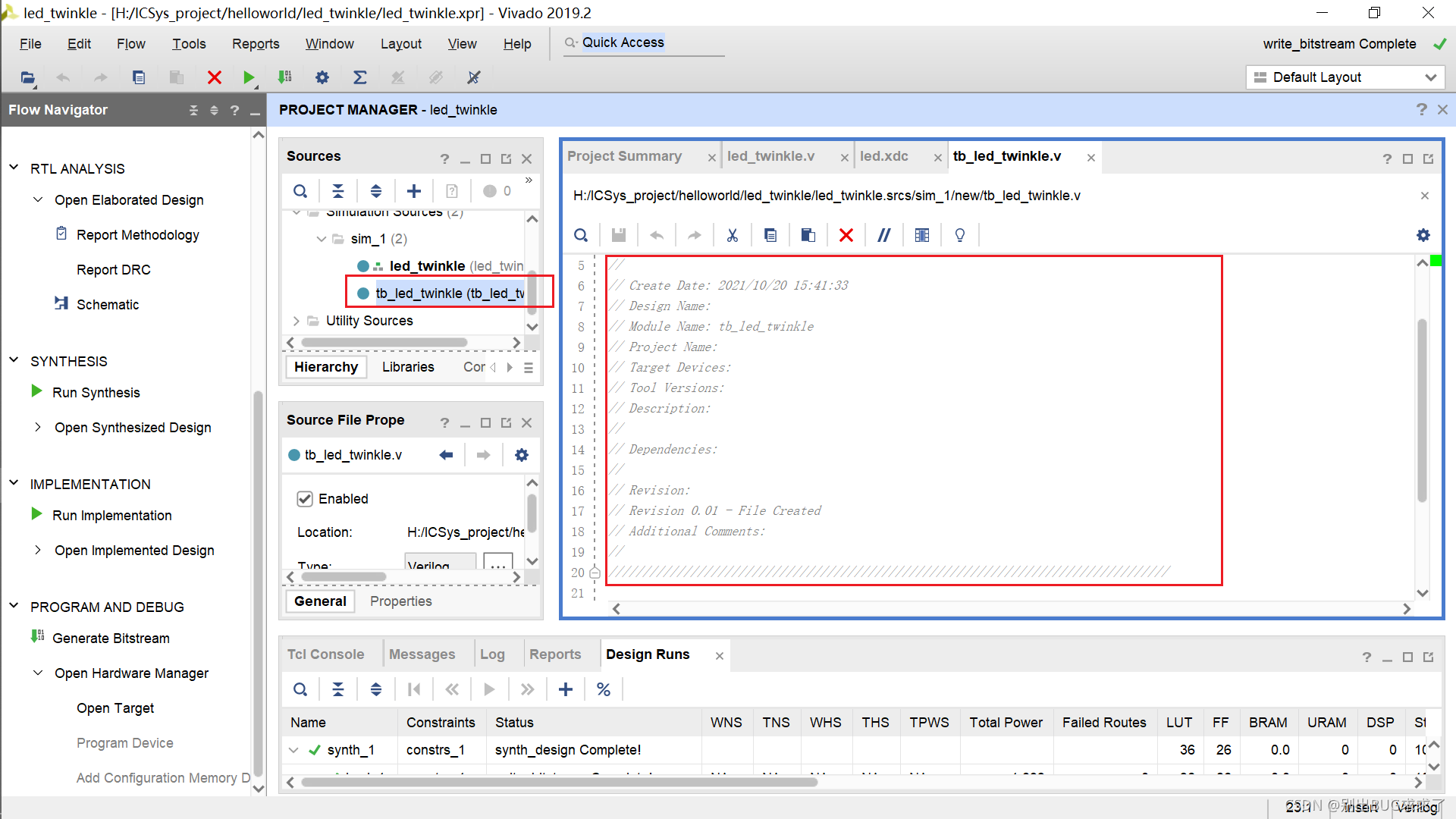

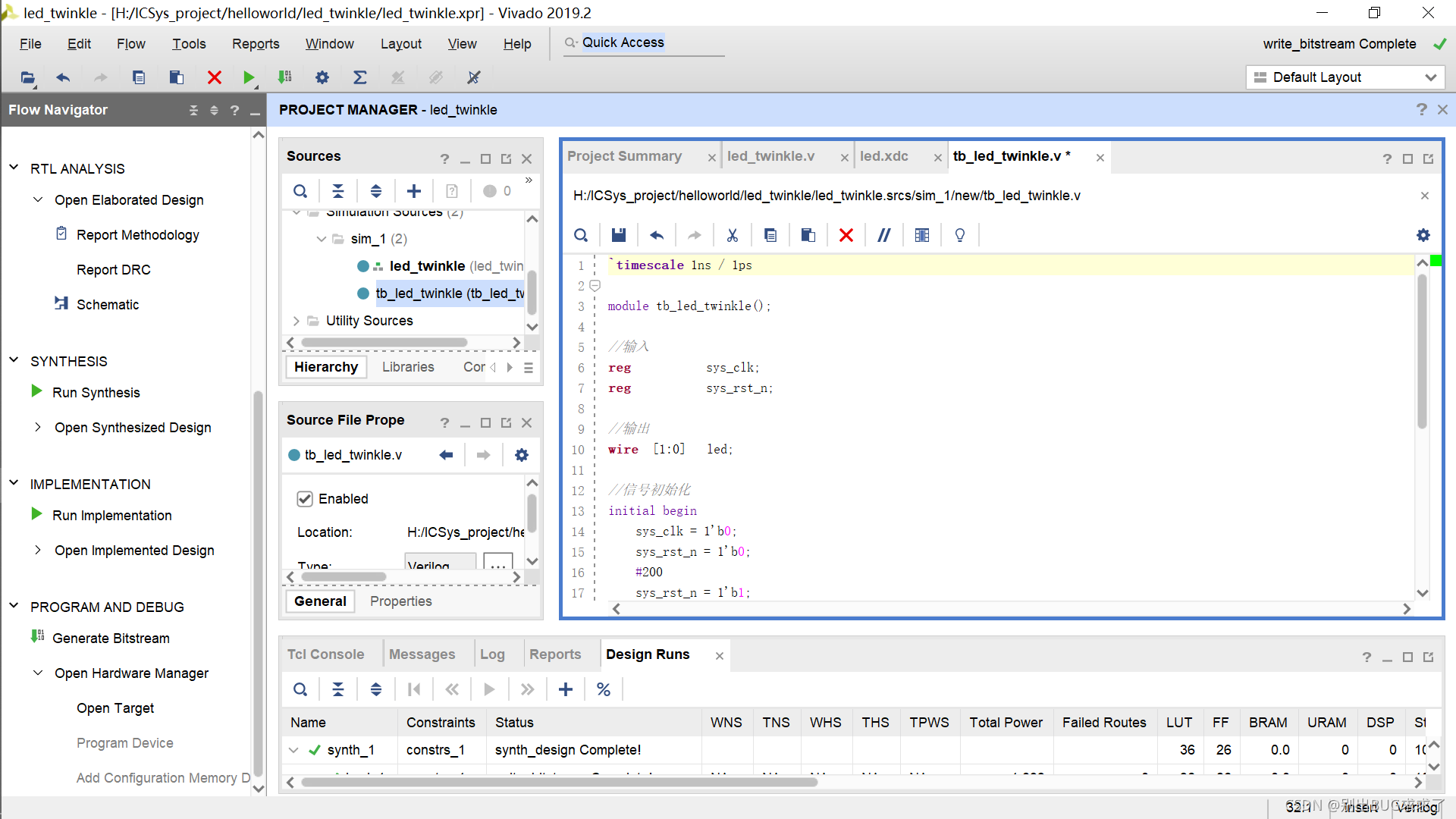

双击testbench文件,把自动生成的注释删去

-

根据自己需求功能编写信号激励

这里主要是时钟和复位信号

-

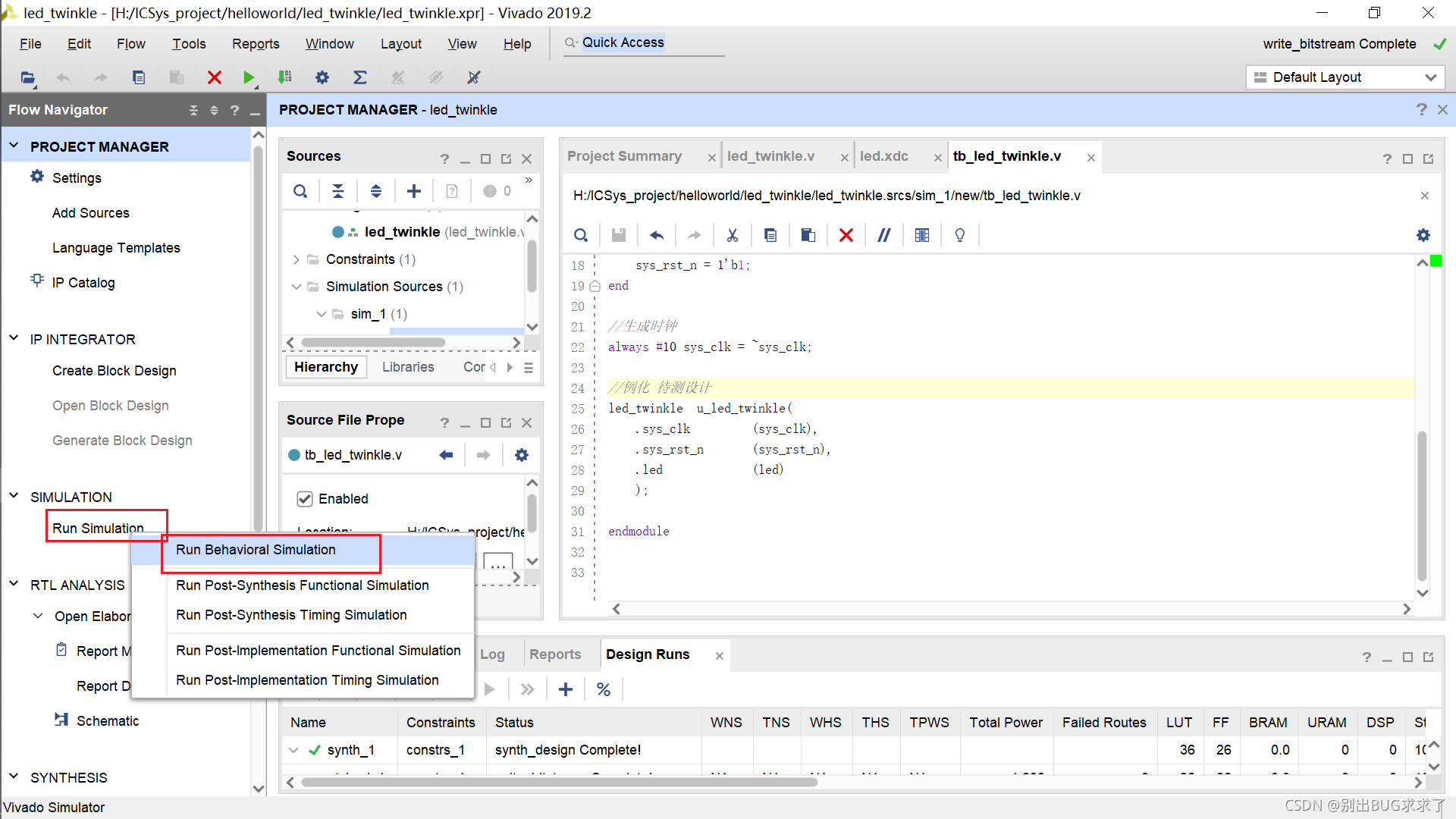

点击行为仿真

结果:

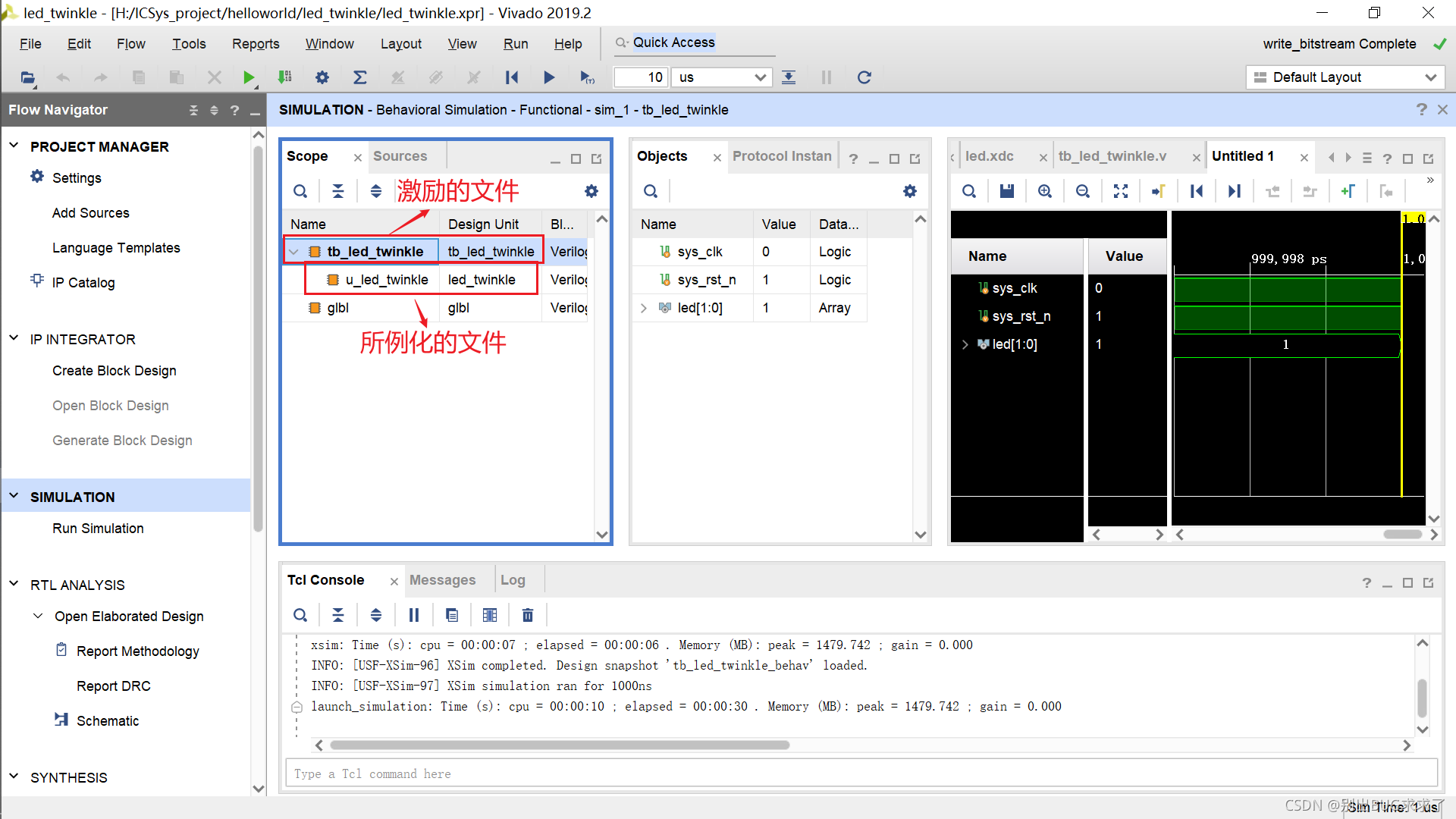

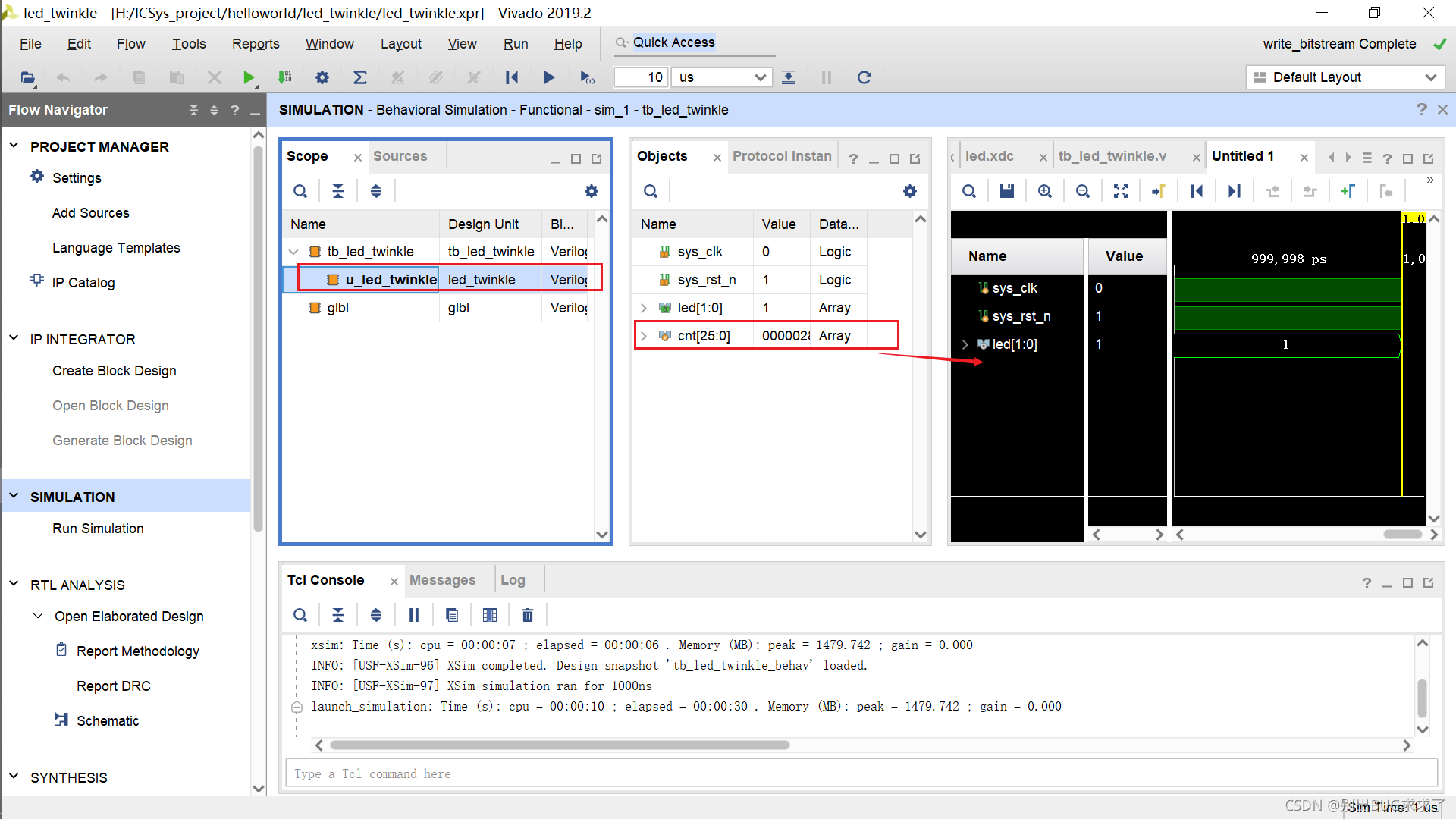

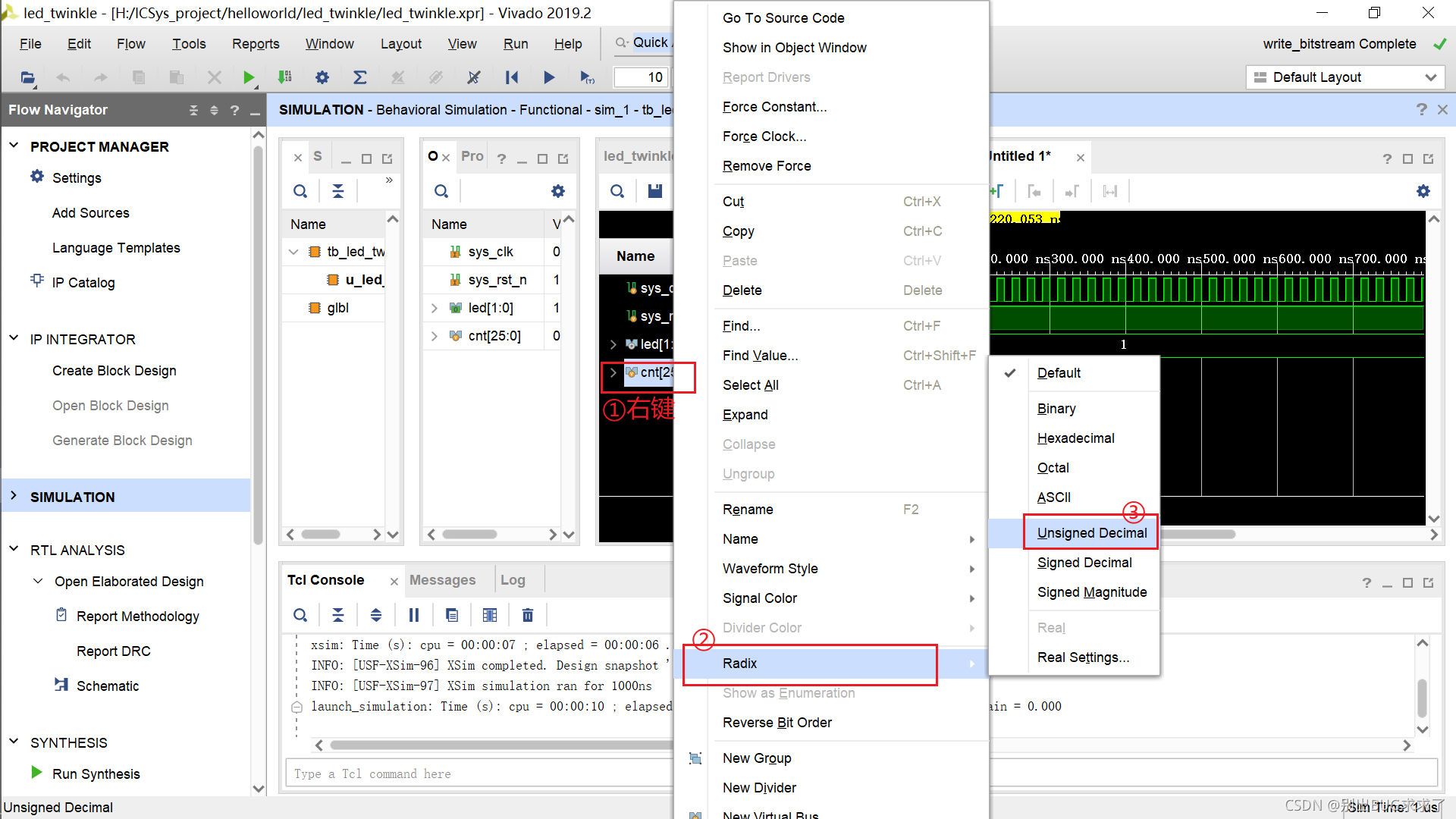

9. 点击所例化的文件,将cnt信号拖入信号栏

自行查看结果即可

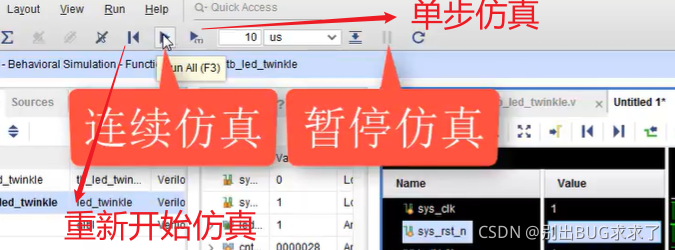

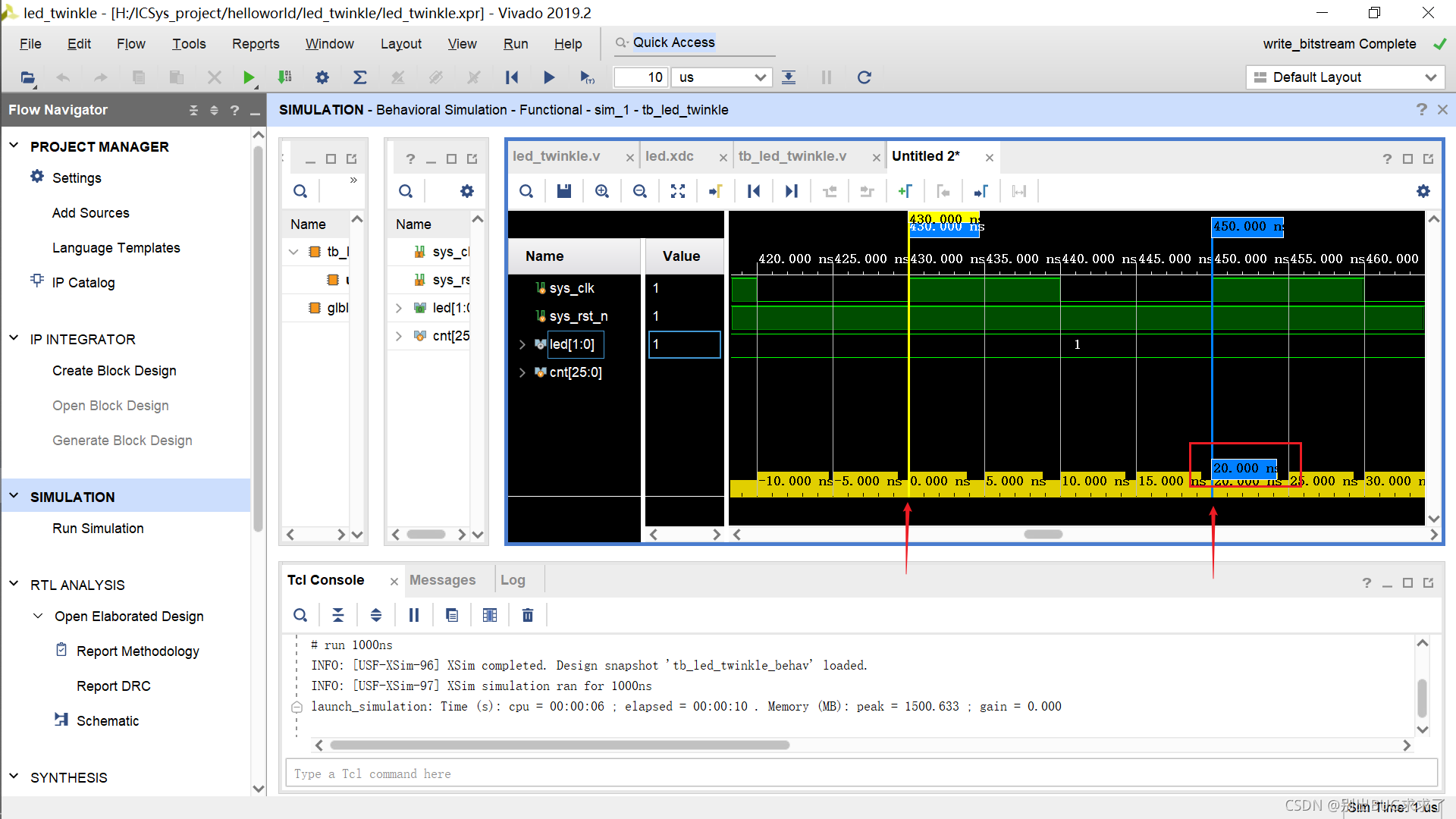

(二)仿真界面指导

-

按钮指导:

-

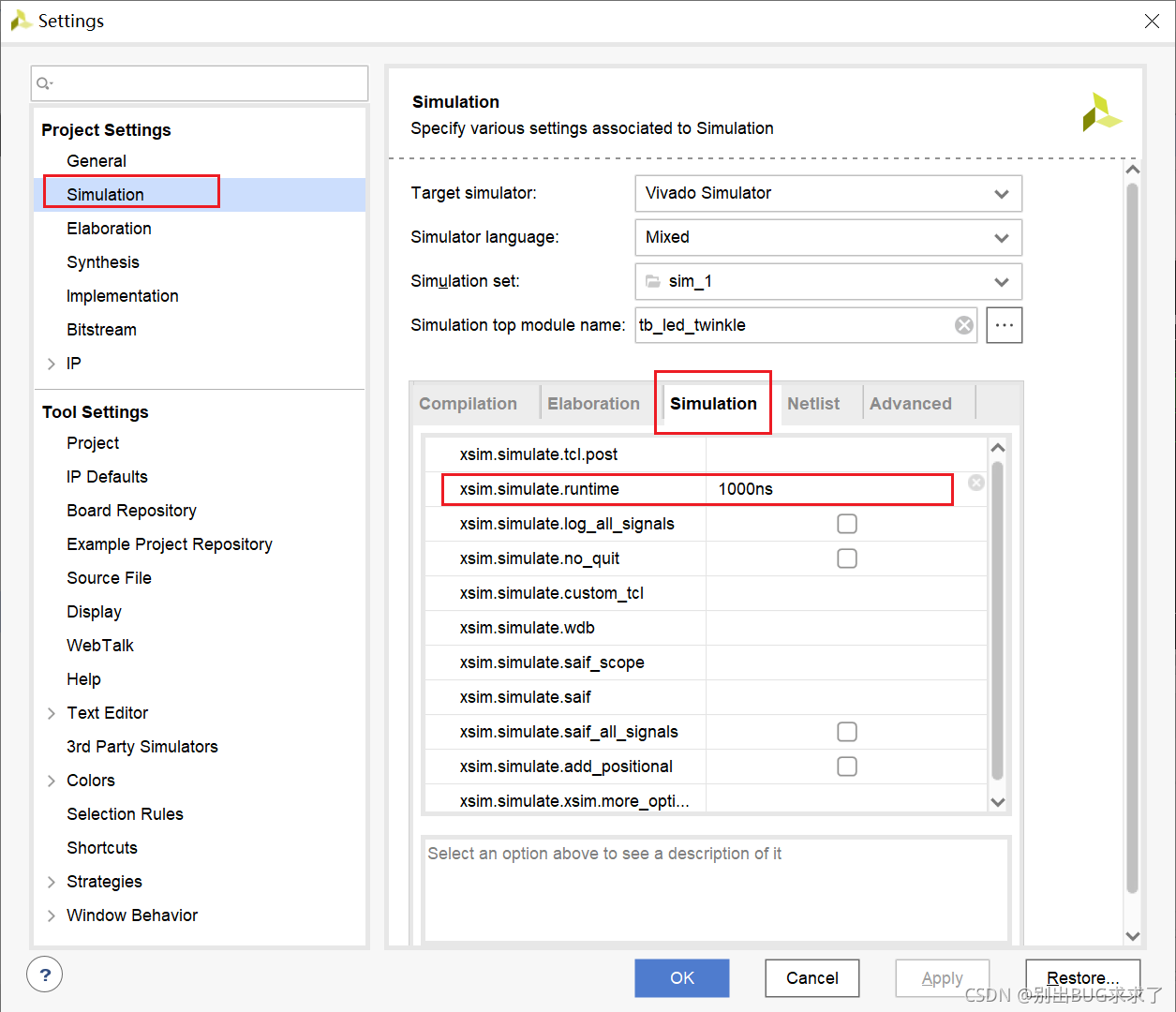

设置仿真时间

这里默认打开后仿真1000ns,可以在这里修改

-

默认为显示十六进制,可以更改为十进制

-

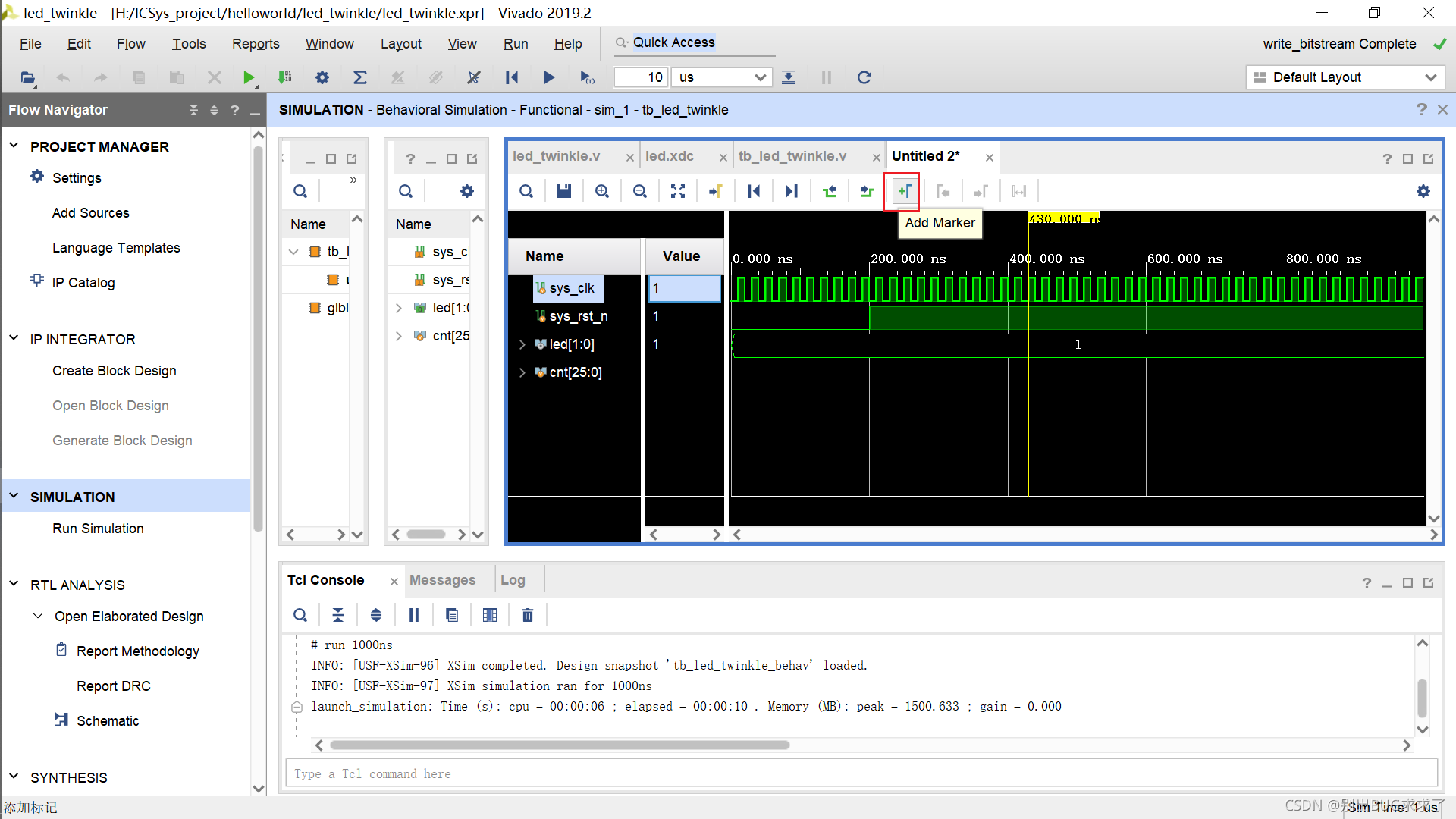

查看时钟周期

间隔的两个上升沿分别add marker

单击左边蓝线,可见间隔为20ns,符合代码

-

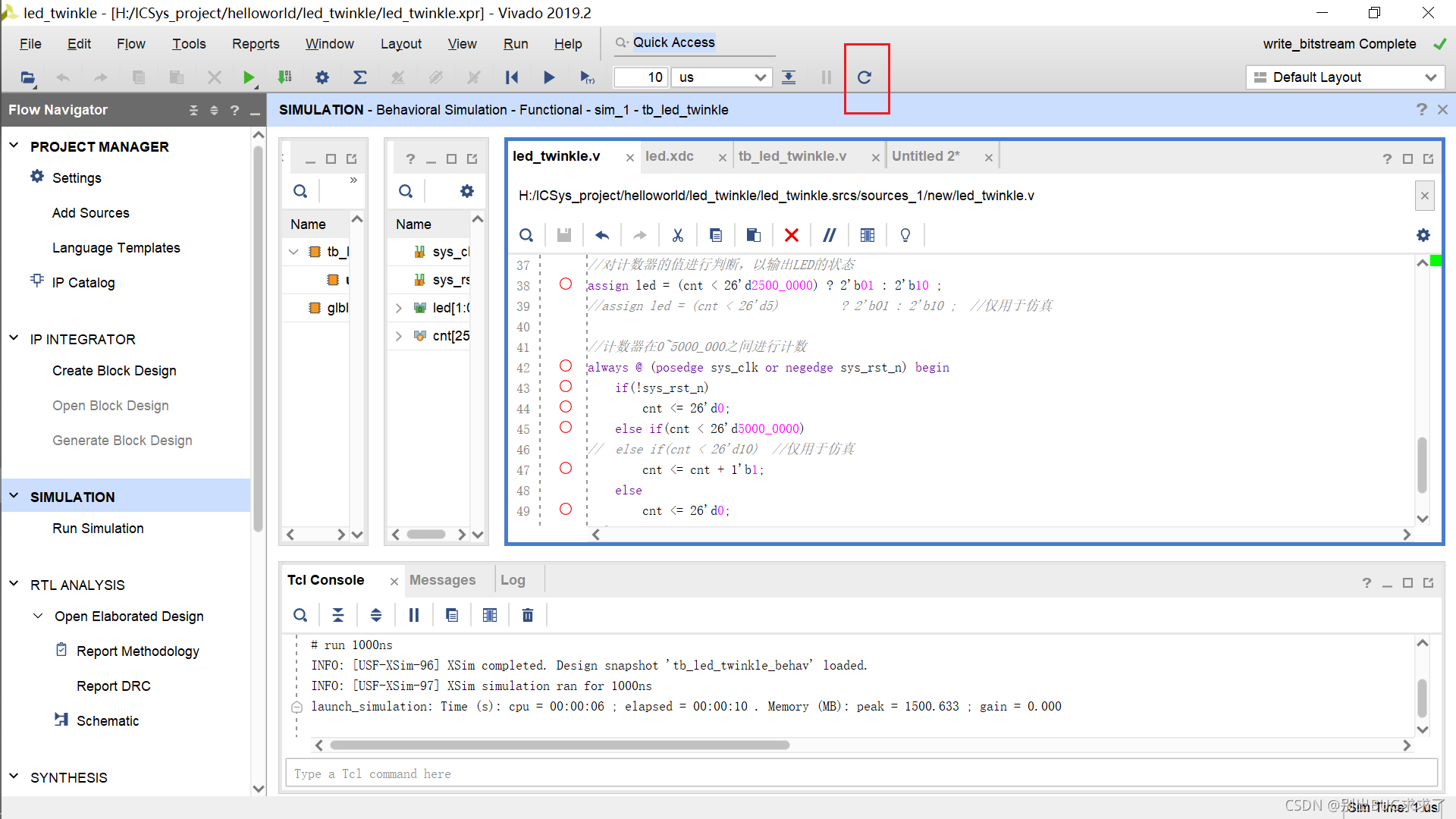

注意的是

代码定义的计数器的值太大,这里只仿真1000ns,如果要跑仿真实际结果,需要很长时间,所以要么就等待,要么就修改计数器的值来模拟即可。

改完代码直接保存,并且relunch即可

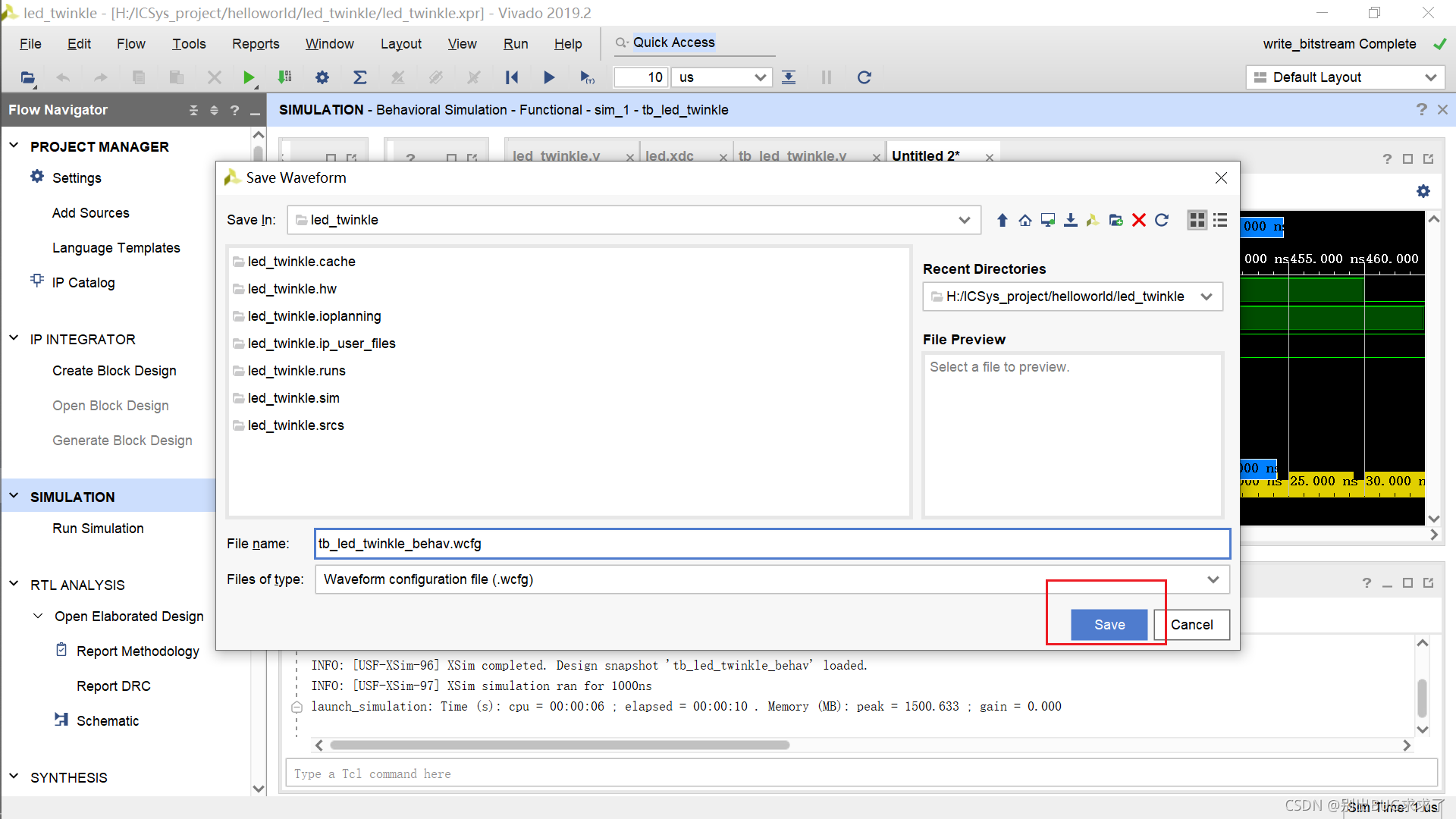

- 保存波形文件

ctrl+s 保存即可

本文详细介绍了基于Zynq的卷积神经网络加速器在Vivado中的设计流程,包括新建工程、设计输入、分析、约束输入、综合、实现和生成比特流等步骤。硬件调试部分涵盖了从创建工程到LED闪烁程序的烧写和仿真,而软件仿真部分则讲解了如何创建激励文件并进行行为仿真。通过这个流程,读者可以掌握Vivado的基本使用方法。

本文详细介绍了基于Zynq的卷积神经网络加速器在Vivado中的设计流程,包括新建工程、设计输入、分析、约束输入、综合、实现和生成比特流等步骤。硬件调试部分涵盖了从创建工程到LED闪烁程序的烧写和仿真,而软件仿真部分则讲解了如何创建激励文件并进行行为仿真。通过这个流程,读者可以掌握Vivado的基本使用方法。

960

960

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?