前言

- 在FPGA中,会由晶振产生时钟信号,一般是50M,但是这块开发板上面是12M的,这时候就需要利用的PLL/MMCM实现时钟的倍频。

在较早期的FPGA中使用的是DCM,其本质上就是DLL(Delay Locked Loop),是数字电路,能实现对输入时钟进行相位移动,补偿,产生倍频和分频,但是后期几乎不怎么使用了。

PLL就是锁相环,是由模拟电路生成,时钟倍频,分频,调节相位等也可以用PLL,并且PLL时钟频率精度比DCM高,而且jitter也更高,但PLL无法动态调整相位。

MMCM是混合模式时钟管理器,是PLL+DCM功能的结合体,本质上是一个PLL,上面加上了DCM的一小部分以进行精细的相移,PLL能实现的功能MMCM都能实现,又因为PLL是模拟电路,DCM是数字电路,所以MMCM叫混合模式。但如果实现的功能相同,PLL占用的资源会少一点。

时钟IP核的调用

-

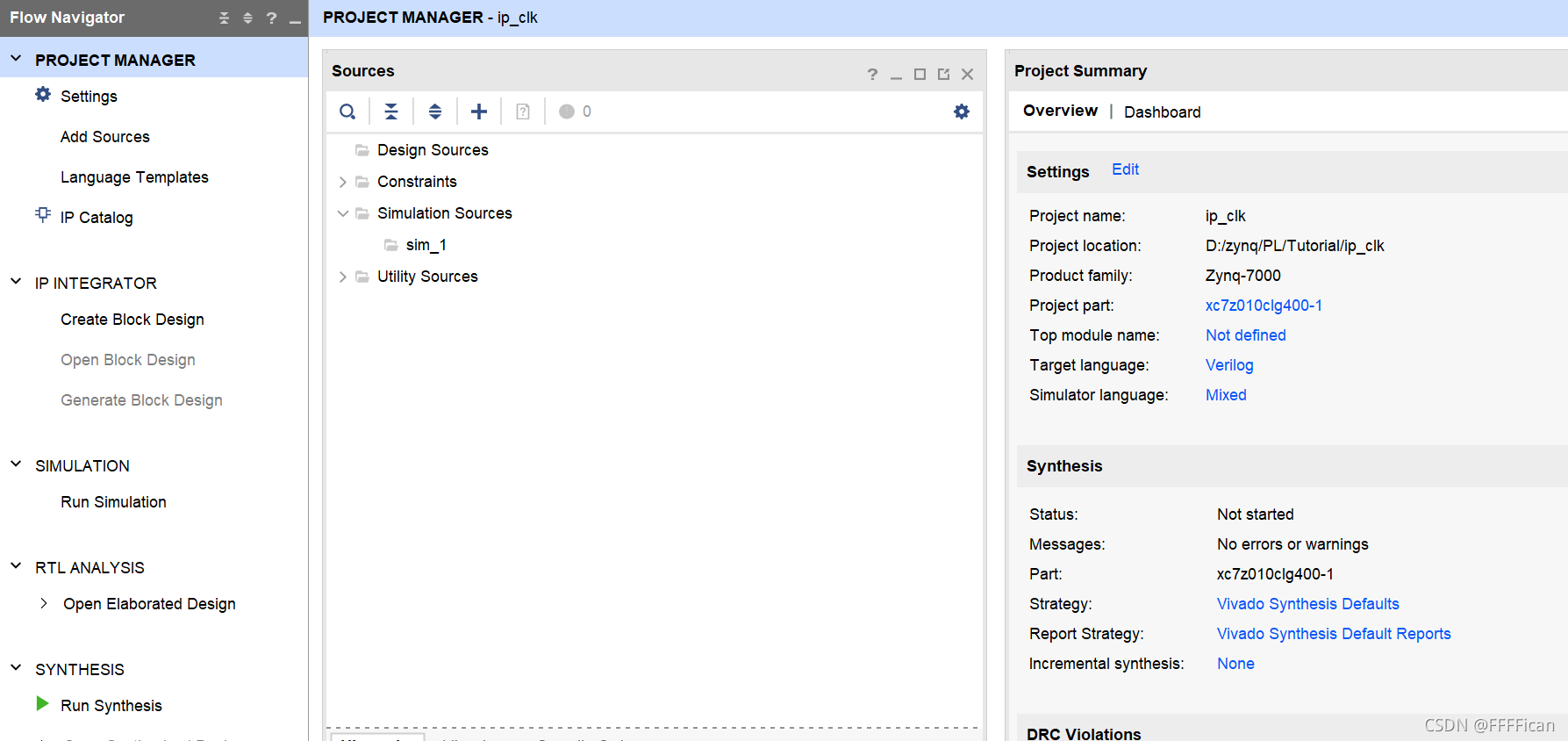

创建文件

-

添加IP核,点击IP Catalog

该博客介绍了在FPGA设计中如何利用PLL和MMCM进行时钟管理,包括时钟倍频、分频和相位调整。文章详细阐述了PLL和DCM的区别,以及MMCM作为两者的结合体的优势。同时,展示了如何在VHDL中例化时钟IP核 clk_wiz_0,配置输出不同频率的时钟,并提供了仿真步骤和波形图。

该博客介绍了在FPGA设计中如何利用PLL和MMCM进行时钟管理,包括时钟倍频、分频和相位调整。文章详细阐述了PLL和DCM的区别,以及MMCM作为两者的结合体的优势。同时,展示了如何在VHDL中例化时钟IP核 clk_wiz_0,配置输出不同频率的时钟,并提供了仿真步骤和波形图。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5854

5854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?