电工之家:www.dgzj.com QQ群:2179090

关注电工之家官方微信公众号“电工之家”,收获更多经验知识。

触发器是由各种基础门电路单元组成,广泛应用于数字电路和计算机中。它具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

触发器具有两个稳定状态,即0和1,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。触发器有集成触发器和门电路组成的触发器二种。触发方式有电平触发和边沿触发二种。触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等例如RS触发器;它是将两个与非门或者或非门的G1 G2的输入、输出端相互交叉连接而成。它用逻辑图和逻辑符号表示,有效高电平、低电平

触发器按逻辑功能分类它主要有以下四种:

①RS触发器:即在时钟脉冲作用下,根据输入信号R,S取值不同,凡具有置0,置1和保持功能的电路,都称为RS型时钟触发器,简称为RS触发器。

②JK触发器:即在时钟脉冲作用下,根据输入信号J,K取值的不同,凡具有保持,置0,置1,翻转功能的电路,都称为JK型时钟触发器,简称为JK触发器。

③D触发器:即在时钟脉冲作用下,凡具有置0,置1功能的电路,都叫做D型时钟触发器,简称为D触发器。

④T触发器:即在时钟脉冲作用下,根据输入信号T取值的不同,凡具有保持和翻转功能的电路,即当T=0时能保持状态不变,T=1时一定翻转的电路,都称为T型时钟触发器,简称为T触发器。

下面就时基555集成块构成的单稳态触发器来述一下其简单工作原理。所谓单稳态触发器它只有一个稳定状态,一个暂稳态。它在电路外加脉冲信号的作用下,可以从一个稳态转换到另一个暂稳态状态。在电路中由RC延时充放电的作用,该暂稳态保持一段时间后又回到原来的初始状态,暂稳态维持时间由RC的阻值和电容量来决定。

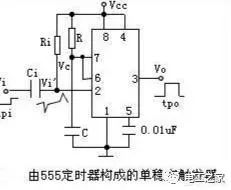

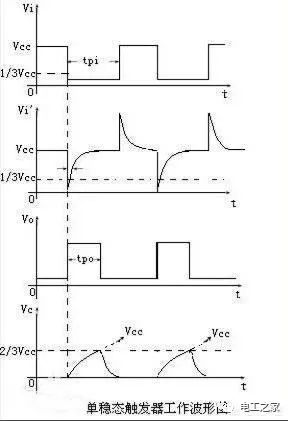

电路组成如上图所示,图中R、C为单稳态触发器的定时元件,它们的连接点Vc与定时器的阈值输入端(6脚)及输出端Vo'(7脚)相连。单稳态触发器输出脉冲宽度tpo=1.1RC。Ri Ci构成输入回路的微分环节,用以使输入信号Vi的负脉冲宽度tpi限制在允许的范围内,一般tpi>5RiCi,通过微分环节,可使Vi'的尖脉冲宽度小于单稳态触发器的输出脉冲宽度tpo。若是输入信号的负脉冲宽度tpi本来就小于tpo,则微分环节可忽略。定时器的复位输入端(4脚)接高电平,控制输入端Vm通过0.01uF接地,定时器输出端Vo(3脚)作为单稳态触发器的单稳信号输出端。工作原理;当输入Vi为高电平时,Ci相当于断开。输入Vi'由于Ri的存在而为高电平Vcc。这时,①若定时器原始状态为0,则集成块(7)输出导通接地,使电容C快速放电、Vc=0,即输入6脚的信号低于2/3电源电压Vcc,此时定时器维持0不变。②若定时器原始状态为1,则集成块(7)输出对地为断开状态,这时Vcc经R向C充电,使Vc电位升高,待Vc值高于2/3电源电压Vcc时,定时器翻转到0状态。综合上述可知,单稳态触发器正常工作时,输入端未加负脉冲,Ⅴi维持高电平,则输出的Vo一定为低电平。单稳态触发器的工作过程分为下面三个阶段来分析,图为其工作波形图:

1、触发翻转阶段:输入负脉冲Vi到来时,下降沿经RiCi微分环节在Vi'端产生下跳负向尖脉冲,其值低于负向阀值(1/3Vcc)。由于稳态时Vc低于正向阀值(2/3Vcc),固定时器翻转为1,输出Vo为高电平,集电极输出对地断开,此时单稳态触发器进入暂稳状态。

2、暂态维持阶段:由于集电极开路输出端(7)对地断开,Vcc通过R向C充电,Vc按指数规律上升并趋向于Vcc。从暂稳态开始到Vc值到达正向阀值(2/3Vcc)之前的这段时间就是暂态维持时间tpo 。

3、返回恢复阶段:当C充电使Vc值高于正向阀值(2/3Vcc)时,由于Vi'端负向尖脉冲已消失 ,Vi'值高于负向阀值(1/3Vcc),定时器翻转为0,输出低电平,集电极输出端(7脚)对地导通,暂态阶段结束。C通过7脚放电,使Vc值低于正向阀值(2/3Vcc),使单稳态触发器恢复稳态。

未完,请点击左下角“阅读原文”继续阅读

本文介绍了触发器的基本概念,特别是双JK触发器74LS112的逻辑功能。触发器作为数字电路中的基本单元,可以实现数据的存储和状态转换。文章详细讲解了RS、JK、D和T四种类型的触发器,并通过时基555集成块构成的单稳态触发器实例,阐述了其工作原理和状态转换过程。

本文介绍了触发器的基本概念,特别是双JK触发器74LS112的逻辑功能。触发器作为数字电路中的基本单元,可以实现数据的存储和状态转换。文章详细讲解了RS、JK、D和T四种类型的触发器,并通过时基555集成块构成的单稳态触发器实例,阐述了其工作原理和状态转换过程。

8240

8240

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?