达尔闻求职笔试经,这不仅仅是题,而是你所不知的知识。

本期笔试经解析题目来源紫光展锐IC笔试题,共3道问答题,涉及知识点包含:锁存器和触发器的概念及区别、典型的时序分析计算。

今天解析的内容是紫光展锐数字IC岗问答题部分,也是本套题的最后一部分内容。问答题一共有4道,我们在求职“笔试经”第九弹:紫光展锐数字IC编程题中解析了其中的一道,下面我们把剩下的三道解析完。

2、锁存器(latch)和触发器(filp-flop)的概念和区别?为什么多用register。行为级描述中latch如何产生的?

解析:

关于锁存器(latch)和触发器(filp-flop)的概念和区别以及如何产生锁存器的情况我们在求职攻略| 典型FPGA器件常用资源(新手必读)中做了一些简单的介绍。

1)锁存器是什么?

从概念上来讲,锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值。简单而言,锁存器的输入有数据信号和使能信号,当处于使能状态时,输出随着输入变化而变化,当不处于使能状态时,输入信号怎么变化都不会影响输出。

2)触发器是什么?

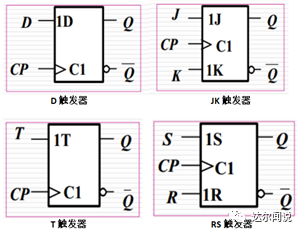

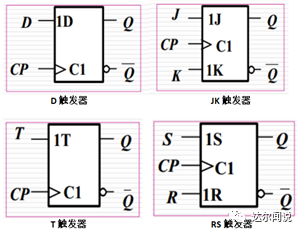

触发器是对脉冲边沿敏感的器件,它的变化只会在时钟的上升沿或者下降沿到来的瞬间改变。下图是几个典型的触发器:

3)区别?

从上面的描述可以看出,锁存器是电平触发的,触发器是边沿触发的。如果是电平触发的,当使能的时候,如果输入信号不稳定,那么输出就会出现毛刺。而触发器就不会出现这种问题,他的变化只会在边沿的时候触发。

4)register是什么?

register是寄存器,用于暂时存放参与运算的数据和运算结果。在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。由于一个触发器能够存储一位二进制码,所以把n个触发器的时钟端口连接起来就能构成一个存储n位二进制码的寄存器。

5)为什么多用register?

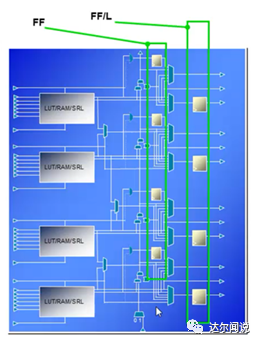

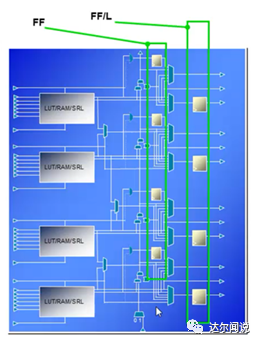

换个角度来讲,为什么少用latch呢?首先,latch是电平触发的,这样就容易产生毛刺;其次,latch将静态时序分析变得极其复杂;再者latch会浪费硬件资源(对FPGA而言)。因为在FPGA当中,是没有latch单元的,要生成latch单元需要耗费其他资源。

以Xilinx器件为例,如下图所示,是Silce的结构,每个Silce包含两列触发器,第一列只可以配置成触发器,第二列可以配置成锁存器和触发器,如果第二列的触发器被配置成锁存器,第一列触发器就不能用了。

6)latch是如何产生的?

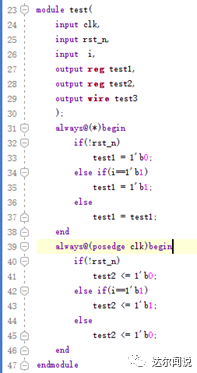

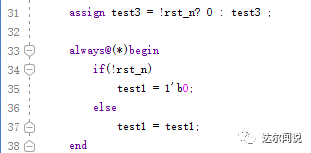

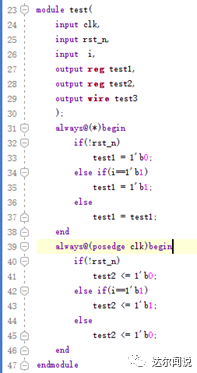

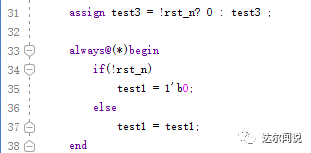

网上大多数都指出,由于if或者case语句的逻辑表达不完全产生的。其实就我个人而言,这样说并不完全正确。首先需要区分一点,我们定义一个类型的时候,单纯的定义reg或者wire其实并不代表它最终实现的真正类型,这得看我们写的代码,这么说也许比较抽象,下面直接上代码:

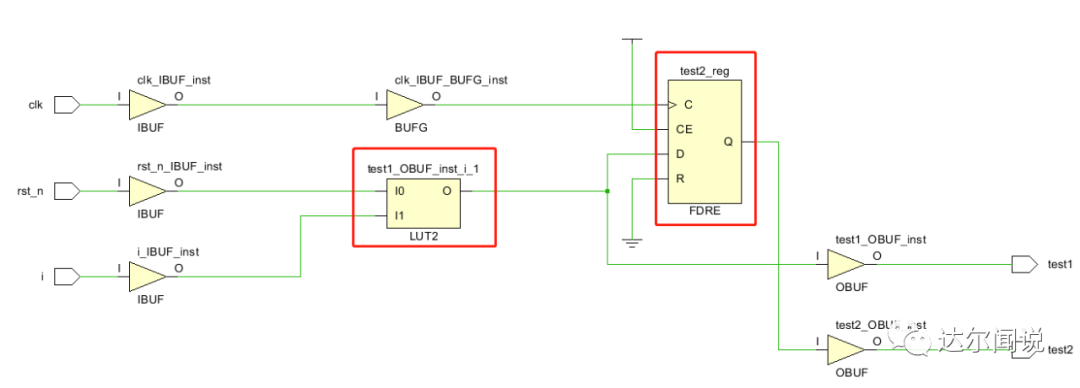

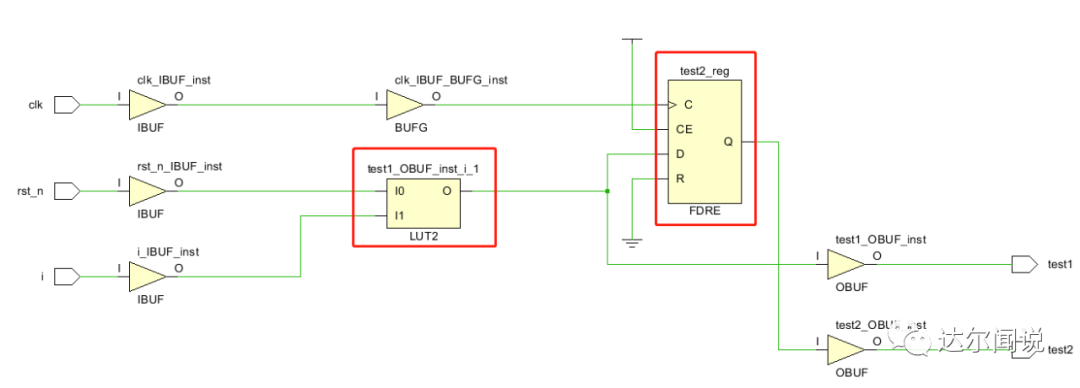

在这段代码里面,test1和test2都是定义为reg类型的,都放在了always语句块里面,除了触发条件不同,其他都相同,下面看看在Vivado综合之后的结果:

可以看到test2是综合成寄存器(触发器)的,而test1直接就“消失”了,被“安排”在了一个LUT“里面”,这也正说明,定义并不代表着最终的结果。在这里,always(*)里面的所谓“reg”,其实和wire没有区别,为了方便称呼,我把wire和这类“reg”统称作“类wire”。

前面铺垫了这个是为了什么呢?为了说明以下会产生latch的两种情况:

①类wire型的数据“自己等于自己”的情况下会产生latch;

②类wire型的数据,由于if或者case语句的逻辑表达不完全,会产生latch。

下面举个例子,如下图所示,test1和test3的表示式不一样,但其实是一样的,都是类wire型。他们都存在着“自己等于自己”的情况。哪怕test1的else内容删除之后,还是会产生latch。

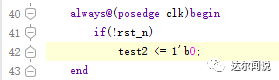

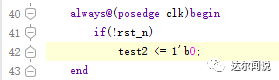

在Vivado中,真正的reg型,如果不在case里面加上default,或者if不加上else,都不会产生latch,如下图所示,如果我们没有定义else,那么在else的情况下,寄存器的值保持不变,其实相当于自动“附加”上“else test2 <= test2; ”,而reg不用怕“自己等于自己”。

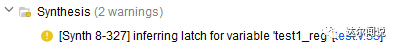

最后总结,上面只是描述了非常直接的“自己等于自己”的情况,有的时候自己并无意如此,但经过多个逻辑表达式之后,还是会有不受时序约束的“自己等于自己”的情况,这样也是会产生latch。其实就算无意中“伪reg”产生了latch也不用急,在综合的时候也会有提示,如下图所示:

有的时候会在implementation的时候提示产生了”loop”,然后直接error了。因此在写代码的时候,特别是fpga的时候,一定要避免产生latch,为了保险起见,也为了良好习惯,不管是什么数据类型,都要在case最后加上default,在if最后加上else。

3、设计一个电路,把A clock domain的一个单周期脉冲同步到B clockdomain,在B domain也为一个单周期脉冲(A、B是异步clock,且时钟周期关系不确定),画出电路图。

解析:

通读题干后我们可以得出一些比较有用的信息:

1)单周期脉冲,说明只有1bit;

2)A、B是异步的,说明需要做跨时钟域的处理;

3)A、B的时钟周期关系不确定,说明要考虑A时钟快还是B时钟快。

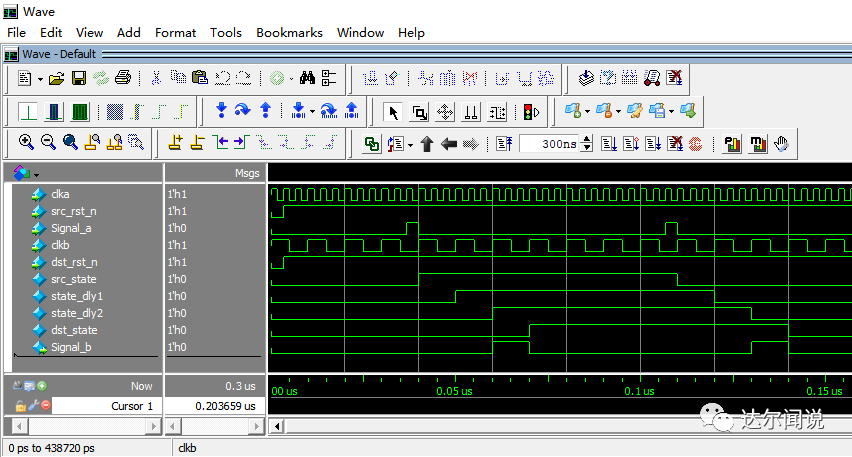

总结下来就是考察我们单比特数据如何做跨时钟域处理的问题,相关的知识点我们在加油站| 单比特信号跨时钟域问题详解(大疆FPGA逻辑岗A卷)中做了详细的讲解。与之不同的是我们要用一种方法实现两种情况(A快B慢和A慢B快),这里我们还是用脉冲展宽的方法,代码不再贴出,直接看仿真结果。

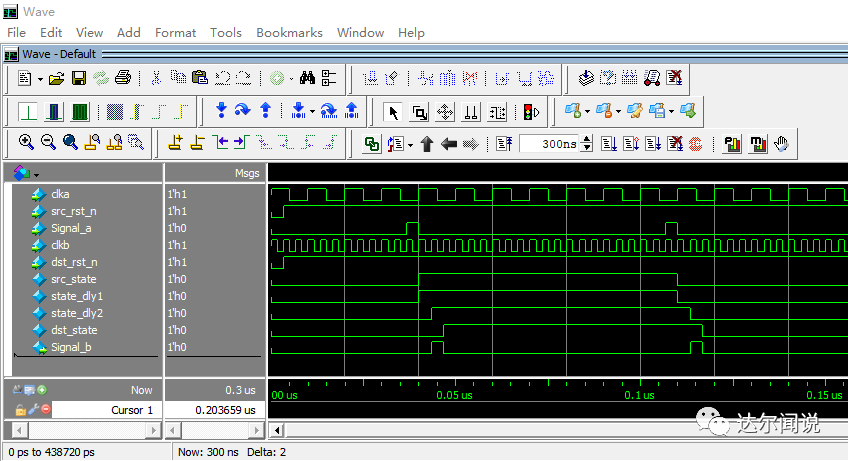

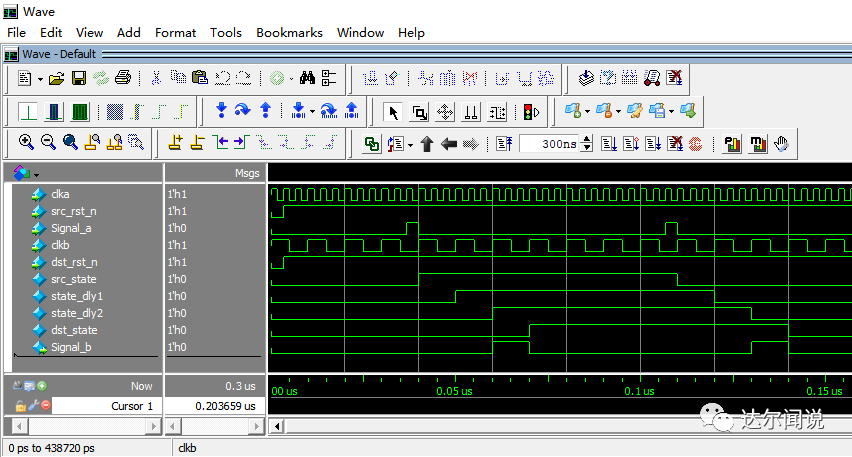

A(约300MHz)快B(100MHz)慢跨时钟域仿真波形图:

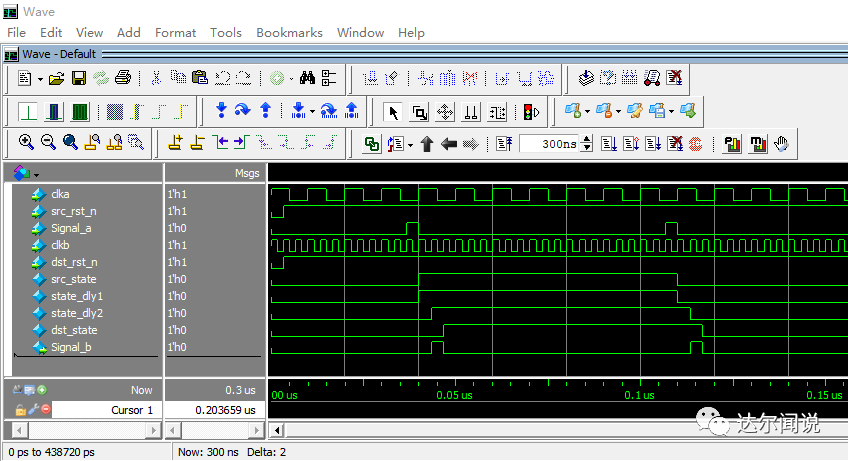

A(100MHz)慢B(约300MHz)快跨时钟域仿真波形图:

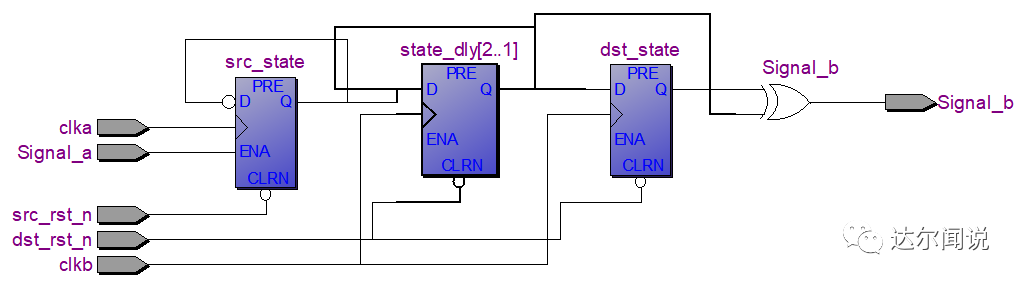

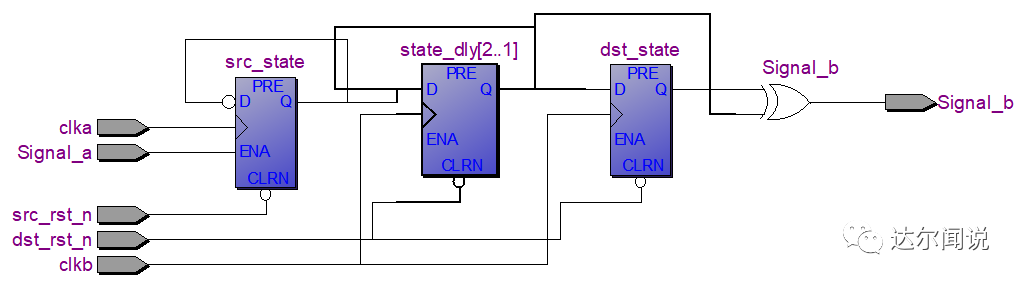

题目要求画出电路图,所以我们可以将如下所示的RTL代码综合出的电路图画出。

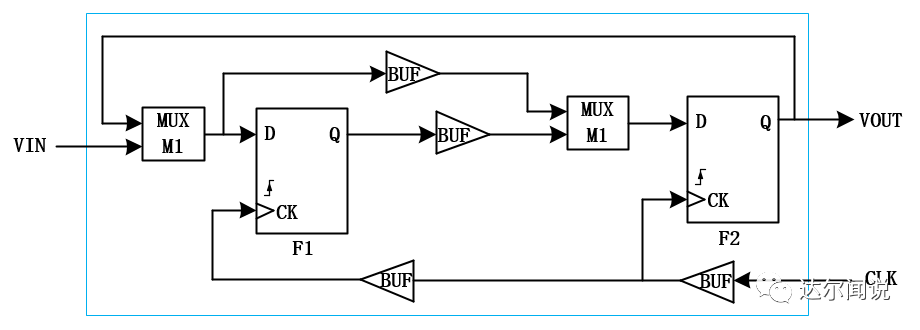

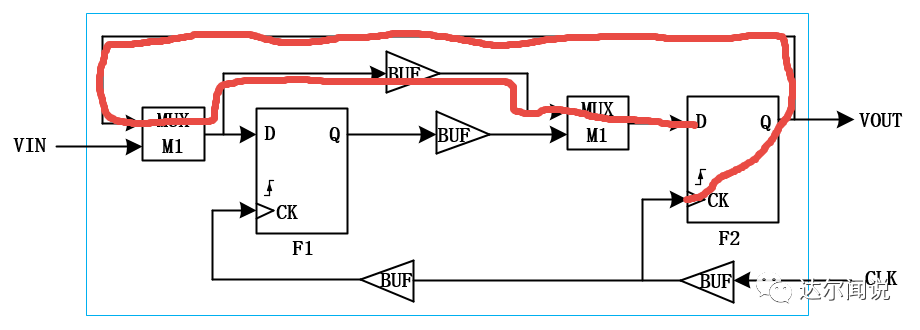

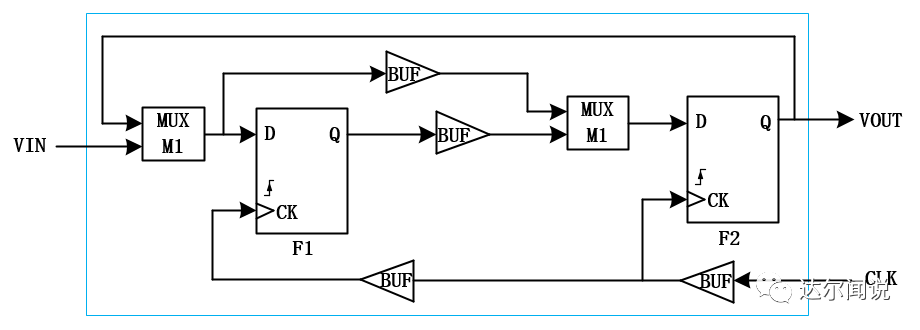

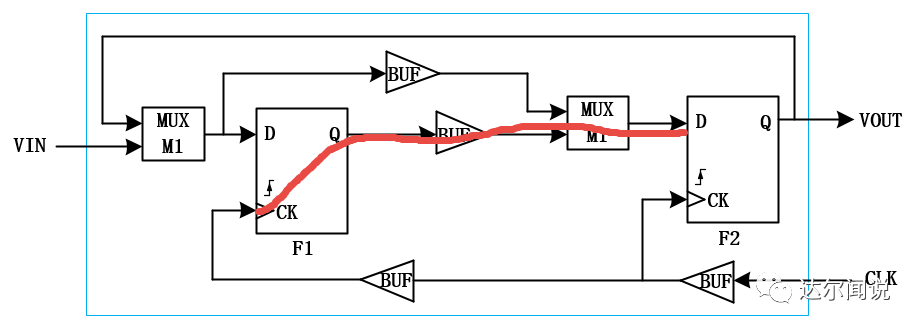

4、图中电路共有三种器件:MUX,BUFFER,DFF,请分析并回答问题。

假设各电路的传出延时为:

TVIN:max delay:8ns;min delay:4ns

TBUF:max delay:2ns;min delay:1ns

TMUX:max delay:3ns;min delay:1ns

DFF:

Tclk-Q:max delay:4ns;min delay:1ns

TSETUP:4ns;THOLD:1.5ns

1)请问本电路是否存在hold time问题?如果有,请修改电路在不影响功能的前提下fixhold time问题。

2)请指出本电路setup time的关键路径,并求最高工作频率是多少?

解析:

这道题目是典型的时序分析计算题,在计算时,我们需要用到在加油站|FPGA时序分析看这篇就够了(大疆逻辑岗)中所推导出的时序分析理论公式。从题干中给出的条件我们就应该有一定的敏感性,题目中没有给出时钟的频率,这也就意味着无法根据时序分析理论公式判断出建立时间是否违例,只能判断保持时间是否违例。再来看两个问题,果不其然,第一问是让判断保持时间违例,第二个是让求最高工作频率。再来看题目中分别给出的每个参数的maxdelay和min delay,分别对应的慢速模型和快速模型,在分析建立时间时是应该用慢速模型,在分析保持时间时应该用快速模型。

1)

题目中有两个寄存器F1和F2,和之前的时序分析理论模型不同,F1寄存器和F2寄存器之间有反馈回路且回路中还有逻辑电路,以及F2到F2自身也有反馈回路且回路中还有逻辑电路。所以我们要分别以F1和F2为对象来计算它们的保持时间余量。我们应该将快速模型参数代入保持时间余量公式:holdtime stack = ((Tco + Tdata) -△T) - Th中进行计算。

①当以F2为对象来分析F2到F1时,其保持时间余量holdtime stack(F1-F2) = ((Tco2 + Tdata) -△T) - Th= ((Tclk-Q + TMUX) - (TBUF - 0) - THOLD= ((1 + 1) - (2 - 0)) - 1.5ns = -1.5ns ≤ 0

②当以F1为对象来分析F1到F2时,其保持时间余量holdtime stack(F2-F1) = ((Tco1 + Tdata) -△T) - Th= ((Tclk-Q +( TBUF + TMUX)) - (0 - TBUF))- THOLD = ((1 + (1 + 1)) - (0 - 1)) - 1.5ns = 2.5ns ≥ 0

③当以F2为对象来分析F2到F2时,其保持时间余量holdtime stack(F2-F2) = ((Tco2 + Tdata) -△T) - Th= ((Tclk-Q +( TMUX + TBUF + TMUX))- (0 - 0)) - THOLD = ((1 + (1 + 1 + 1)) - (0 - 0)) - 1.5ns = 2.5ns ≥ 0

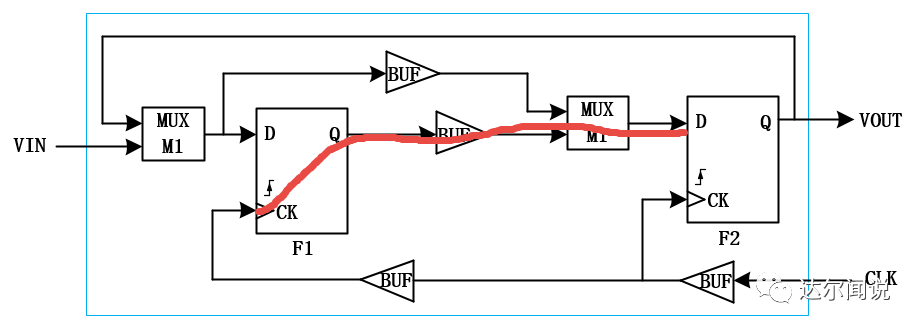

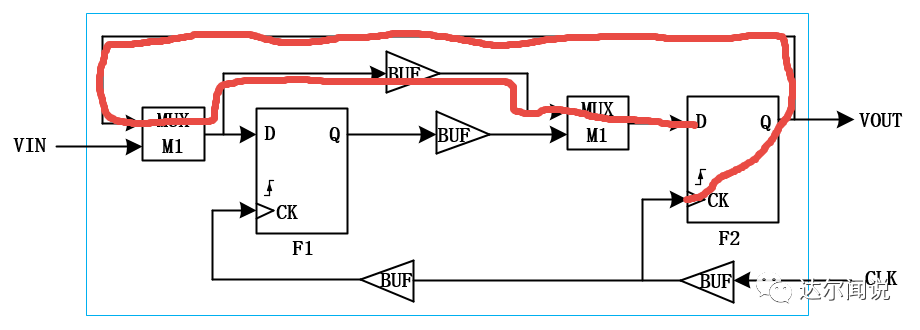

因为以F1为对象分析出的保持时间余量为负数,所以以F1为对象的保持时间违例,我们能做的就是在F2到F1之间的路径中加入两个BUF,既能满足以F1为对象的保持时间的时序要求又不影响电路的功能。

④另外题目中还给出了TVIN的值,所还要再计算相对于外部输入数据的保持时间余量holdtime stack(VIN) = ((Tdelay + Tdata) -△T) - Th= ((TVIN + TMUX) - (TBUF - 0) - THOLD= ((4 + 1) - (2 + 2 - 0)) - 1.5ns = -0.5ns ≤ 0,这样在不影响电路功能的情况下还需要在VIN到F1之间再加一个BUF。

综上两种加入BUF的情况,统一将BUF插入到MUX M1与寄存器F1之间的位置,就可以同时解决两处的保持时间违例了。

2)

第二问是要指出setuptime关键路径(critical path),那什么是关键路径呢?关键路径简单的理解就是延迟最大的那条路径,所以我们要找出setup time中延迟最大的那条路径,这条路径决定了系统中时钟所能工作的最大频率。而关于建立时间相关问题的计算,我们应该将慢速模型参数代入建立时间余量公式:setuptime stack = (Tclk - (Tco + Tdata) + △T) -Tsu中进行计算。要求出频率,在理想情况下建立时间余量为0,但是往往要大于0,即(Tclk- (Tco + Tdata) + △T) -Tsu≥ 0,根据这个关系可以得出时钟的周期Tclk ≥ (Tco+ Tdata) - △T + Tsu

和第一问一样,同样有三条内部路径需要分析(因为题目中没有给外部时钟,所以不用考虑相对于外部输入数据的建立时间)。然后对比,找出延时最大的那条路径就是关键路径,并用此路径求出时钟的最高工作频率。

①当以F1为对象来分析F1到F2时,其路径如下所示,(Tco1+ Tdata) - △T + Tsu = ((Tclk-Q + (TBUF + TMUX))-(0 - TBUF) + TSETUP = ((4 + (2 + 3)) - (0 - 2)) + 4ns =15ns

②当以F2为对象来分析时F2到F1,其路径如下所示,(Tco2+ Tdata) - △T + Tsu = ((Tclk-Q + TMUX) - (TBUF- 0) + TSETUP = ((4 + 3) - (1 - 0)) + 4ns = 10ns

③当以F2为对象来分析F2到F2时,其路径如下所示,(Tco2+ Tdata) - △T + Tsu = ((Tclk-Q + (TMUX + TBUF +TMUX)) - (0 - 0) + TSETUP = ((4 + (3 + 2 + 3))- (0 - 0)) + 4ns = 16ns

综上所示,延时最长的为③,所以在理想情况下最高工作频率是Tclk ≥ 16ns = 62.5MHz。END

目前,我们正在通过大疆硬件岗和FPGA逻辑岗的题目,为大家带来笔试题的解析,以及知识的补充。如果有想要解析的题目,可以发给达尔闻安排。同时,欢迎加入达尔闻求职技术交流群,进群方式:添加妮姐微信(459888529),并备注求职,即可邀请进群。

达尔闻求职系列:

磁珠的用法、PCB布线3W规则

单比特信号跨时钟域问题详解

如何搞定状态机问题

电容击穿表现为短路?

MOS管导通损耗和什么有关?

毛刺滤除的代码应该如何写

资深工程师总结减小串扰的7种方法

二进制数11.101对应的十进制数是多少

FGPA时序分析看这篇就够了

逻辑电路24种表达式

芯片工艺28nm的28是指什么

FPGA设计中的时序收敛准则

华为硬件逻辑岗(FPGA)

紫光展锐数字IC岗(编程题)

从无人机爱好者到获得DJI大疆Offer

offer拿到手软,最后选华为!

IO的时序约束该如何设置

典型FPGA器件常用资源

死活清除不了的亚稳态,怎么减少出现概率?

典型5级流水线RSIC结构中的5大功能

三步优化FPGA时序设计

噪声还分颜色?粉红、白噪声解析

电源拓扑别再傻傻搞不清楚

开关电源中的MOS功耗来源

晶体管的静态工作点一步快速搞定!

老司机也要复习功率二极管、三相半波可控整流电路

2021年校招提前批第一枪(vivo芯片设计岗)

建立时间VS保持时间,竞争VS冒险(紫光展锐IC笔试题)

RAM的大小为520*8bit,其地址需要多少位

在这段代码里面,test1和test2都是定义为reg类型的,都放在了always语句块里面,除了触发条件不同,其他都相同,下面看看在Vivado综合之后的结果:

在这段代码里面,test1和test2都是定义为reg类型的,都放在了always语句块里面,除了触发条件不同,其他都相同,下面看看在Vivado综合之后的结果:

综上所示,延时最长的为③,所以在理想情况下最高工作频率是Tclk ≥ 16ns = 62.5MHz。END

综上所示,延时最长的为③,所以在理想情况下最高工作频率是Tclk ≥ 16ns = 62.5MHz。END

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?