摘要:JTAG to AXI Master这个IP 核非常好用,在做工程的时候可以直接绕开PS,使用vivado以及tcl指令直接对自己的代码进行调试。

目录

1.JTAG to AXI Master IP

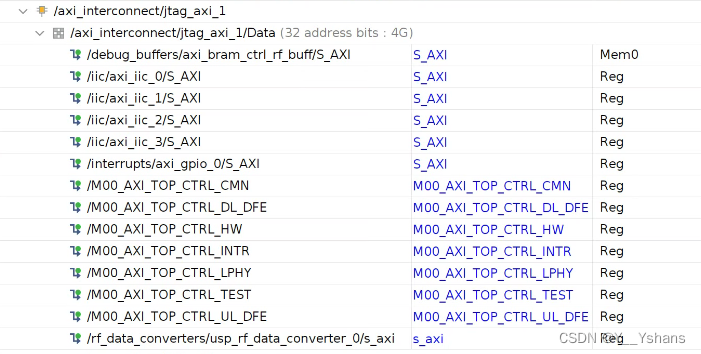

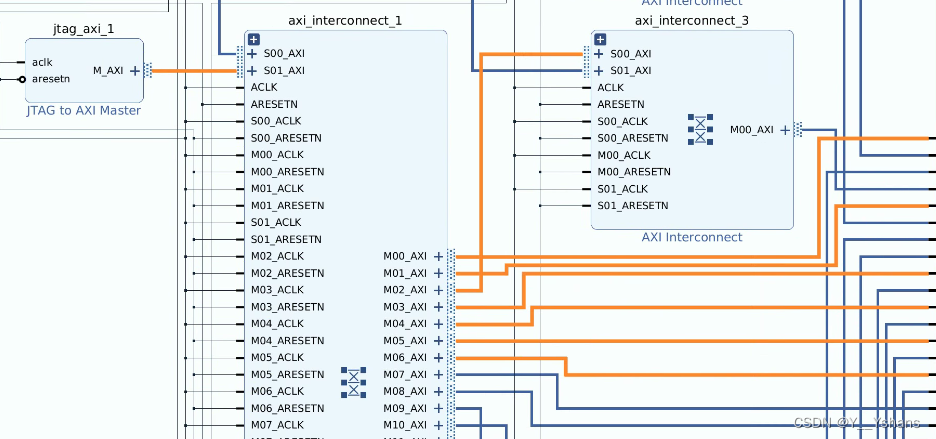

使用这个IP核,跟axi interconnect连出去,给到虚拟接口(记得在Address Editor里面定义地址,最好与ps端保持一致即可)。这样一来,就可以通过vivado的tcl去进行调试。

2.TCL指令

首先打开vivado,连接硬件,需要在tcl框里面定义这些,把下列代码写进文本文件,例如:vernon_lib.tcl

# AXI or AXI Lite access via JTAG

set addr_version A0262000;

set addr_scratch A0263ffc;

# ---------------------------------------------------------------------------- #

# Generic Procedures #

# ---------------------------------------------------------------------------- #

proc rd_axi {reg_addr} {

create_hw_axi_txn rd [get_hw_axis hw_axi_1] -address $reg_addr -type read -force;

run_hw_axi rd;

}

proc wr_axi {reg_addr reg_value} {

create_hw_axi_txn wr [get_hw_axis hw_axi_1] -address $reg_addr -data $reg_value -type write -force

run_hw_axi wr

}

proc wv_axi {reg_addr reg_value} {

wr_axi $reg_addr $reg_value

rd_axi $reg_addr

}

# ---------------------------------------------------------------------------- #

# Version Register #

# ---------------------------------------------------------------------------- #

proc rd_version {} {

rd_axi $::addr_version

}

# ---------------------------------------------------------------------------- #

# Scratch Register #

# ---------------------------------------------------------------------------- #

proc rw_scratch {} {

rd_axi $::addr_scratch

wr_axi $::addr_scratch 12345678

rd_axi $::addr_scratch

}现在vivado tcl里面输入上述的文件,例如下面,$scr_path是这个文件的路径:

source $scr_path/vernon_lib.tcl

然后可以用自己建的rd_axi和wr_axi去进行读写操作:

# AXI or AXI Lite access via JTAG

source $scr_path/vernon_lib.tcl

rd_version

rw_scratch

# ------------------------------------------------------------------------------#

#

# ------------------------------------------------------------------------------#

# # Example: Read Version and Scratch Registers

# rd_axi A0262000

#

# # Example: Write Scratch Register

# wr_axi A0263ffc 12346789

#

# # Example: Read Scratch Register

# rd_axi A0263ffc

###################################software command##############################

#read fh buff

wr_axi A0264018 00000001

#dl 0-3 carry en

wr_axi A0262200 01010101

# bypass dpd cfr

wr_axi A0265ff8 FEEDBEEF

wr_axi A0265308 00000003

# sample number

wr_axi A026A120 c004B000

wr_axi A026A120 c0096000

#start trig

wr_axi A026A124 00000000

wr_axi A026A124 00000001

本文介绍了如何利用JTAGtoAXIMaster IP核在Vivado中进行AXI总线的高效调试,通过TCL脚本实现寄存器读写,详细展示了设置和执行步骤,并提供了示例代码。

本文介绍了如何利用JTAGtoAXIMaster IP核在Vivado中进行AXI总线的高效调试,通过TCL脚本实现寄存器读写,详细展示了设置和执行步骤,并提供了示例代码。

1524

1524

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?