首先来看一段代码。这里用一个简单的计数器来举例。

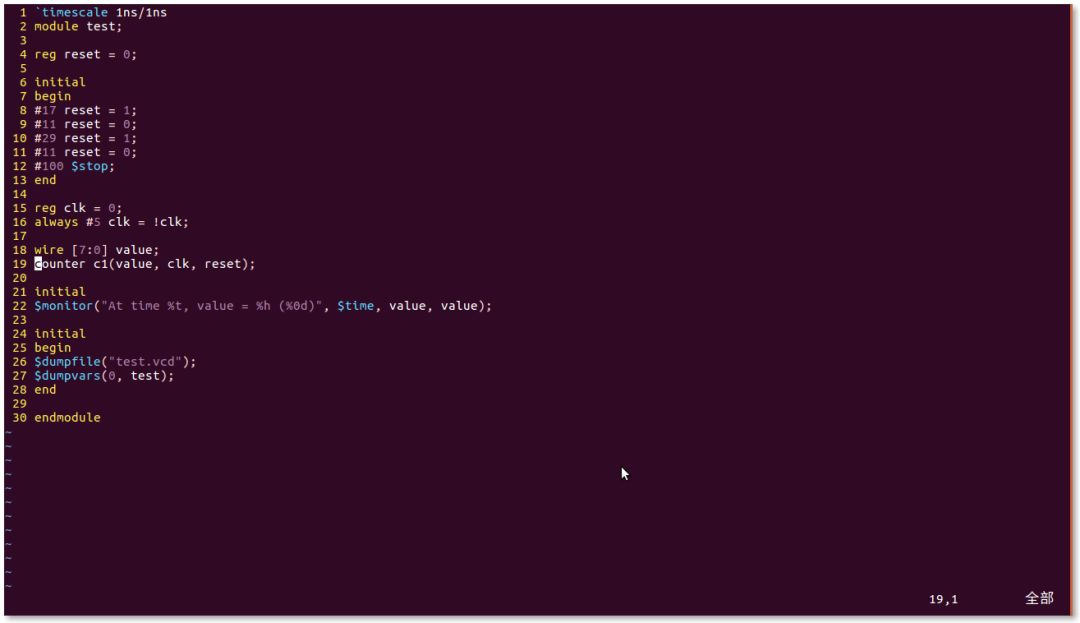

然后写一个testbench。

`timescale 1ns/1ns

module和testbench中这个时间刻度一定要标清楚。

$dumpfile("test.vcd");

$dumpvars(0, test);

这两行用来产生vcd波形。这个波形是给gtkwave用的。

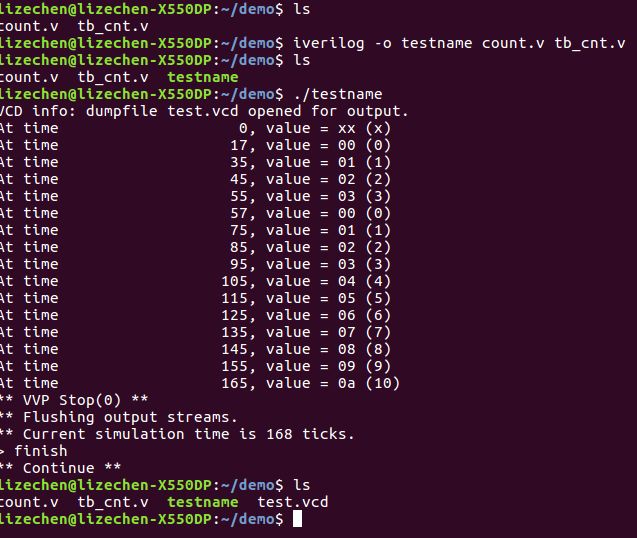

准备好了必要的代码。

现在准备使用工具开干吧。

执行iverilog命令如 iverilog -o testname count.v tb_cnt.v

按:-o name (name是输出的文件名,是一个可执行文件,执行止呕胡会出现.vcd波形文件,这个文件可使用gtkwave查看)

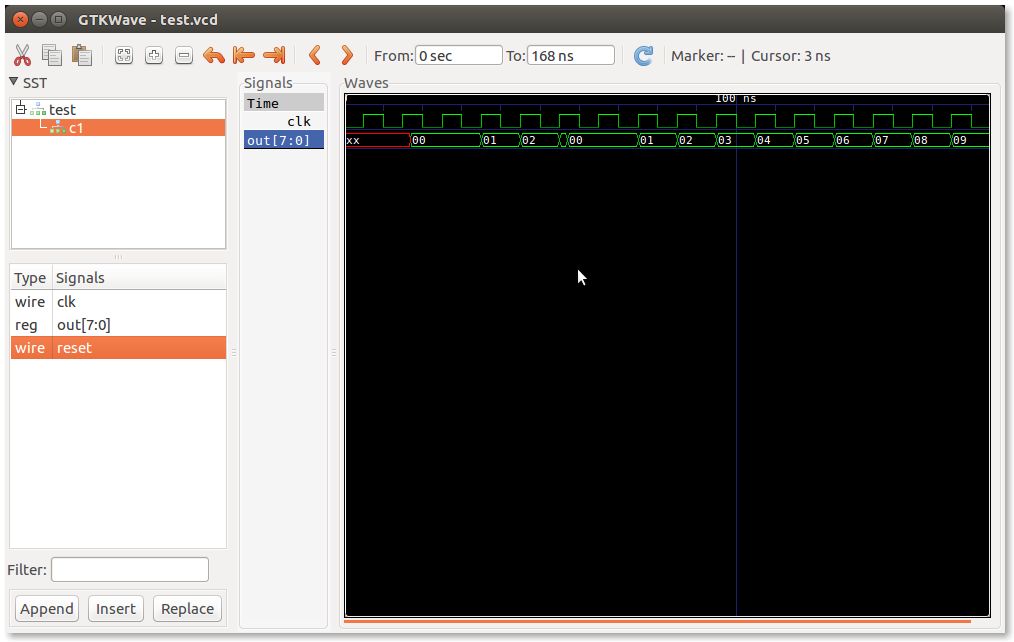

使用gtkwave命令如gtkwave test.vcd

这里需要将左边的信号拖动到右边才会显示。

相信聪明的你一定可以学会的。

说一说相关的参数。

iverilog:

-g2012 :使用这个参数,可以支持部分Systemverilog语法。方便验证。

-o :可以制定输出文件的名字,否则默认是a.out

3091

3091

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?