环境

软件:ISE 14.7

硬件:ALINX AX3091

错误思路

process(key)

begin

if(key = '1') then

t <= t xor '1';

end if;

end process;

process(t)

begin

led <= t;

end process;

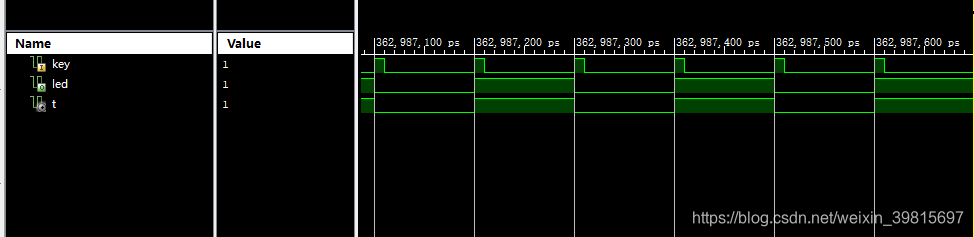

结果仿真

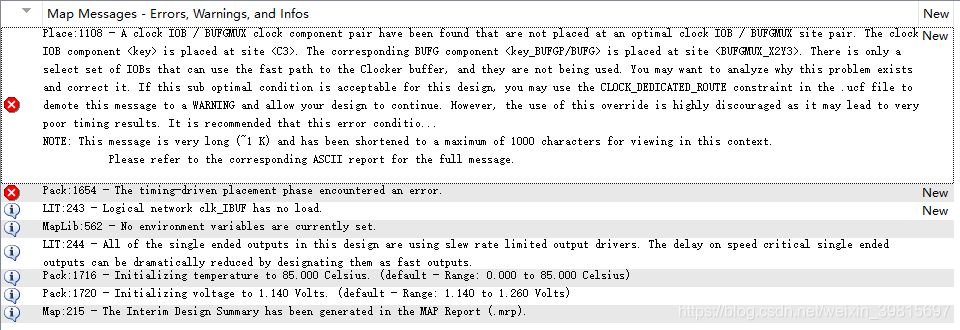

仿真正确,但是实际并不成功,错误提示如下:

经过一番查阅资料234后,觉得原因在于将普通IO引脚作为了时钟输入。

由于初学还不熟悉FPGA的架构及其时钟管理,这里等日后弄懂了再回来补充,也欢迎大家在评论中指出。

关键逻辑

由于用到D-Flip-Flop,因此需要引入时钟信号,在时钟上升沿时扫描按键是否被按下,是则将当前灯的状态反转,实现按键控制LED开关的功能。

按键扫描及消抖(50ms)

消抖逻辑需要自己花时间理解一下5

process(clk)

begin

if(clk'event and clk = '1') then

if(key = '0') then

count <= count + 1;

if(count = 2500000) then

t <= t xor '1';

end if;

else count<=0;

end if;

end if;

end process;

Code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity KeyLED is

Port ( clk : in bit;

key : in bit;

led : out bit);

end KeyLED;

architecture Behavioral of KeyLED is

signal t:bit:='0';

signal count:integer:=0;

begin

process(clk)

begin

if(clk'event and clk = '1') then

if(key = '0') then

count <= count + 1;

if(count = 2500000) then

t <= t xor '1';

end if;

else count<=0;

end if;

end if;

end process;

process(t)

begin

led <= t;

end process;

end Behavioral;

AX309.ucf(节选)

NET "CLK_50M" LOC = T8 | TNM_NET = sys_clk_pin;

TIMESPEC TS_sys_clk_pin = PERIOD "sys_clk_pin" 50000 KHz;

##

## reset pushbutton

NET RSTn LOC = L3 | IOSTANDARD = "LVCMOS33";

##

########LED Pin define#####################

## LED1

NET led<0> LOC = P4 | IOSTANDARD = "LVCMOS33";

## LED2

NET led<1> LOC = N5 | IOSTANDARD = "LVCMOS33";

## LED3

NET led<2> LOC = P5 | IOSTANDARD = "LVCMOS33";

## LED4

NET led<3> LOC = M6 | IOSTANDARD = "LVCMOS33";

########KEY Pin define#####################

## KEY1

NET key_in<0> LOC = C3 | IOSTANDARD = "LVCMOS33";

## KEY2

NET key_in<1> LOC = D3 | IOSTANDARD = "LVCMOS33";

## KEY3

NET key_in<2> LOC = E4 | IOSTANDARD = "LVCMOS33";

## KEY4

NET key_in<3> LOC = E3 | IOSTANDARD = "LVCMOS33";

在ALINX AX309平台上,我们可以通过文件ax309.ucf查看硬件资源及引脚:

1:时钟频率为50MHz,引脚为T8。

2:LED引脚分别为P4,N5,P5,M6,这里选了LED1,即P4。

3:KEY引脚分别为C3,D3,E4,E3,这里选了KEY1,即C3。

总结

这次实验,更进一步接触到时序电路,FPGA在时序上与STM32用delay实现的很多逻辑不一样。

1985

1985

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?