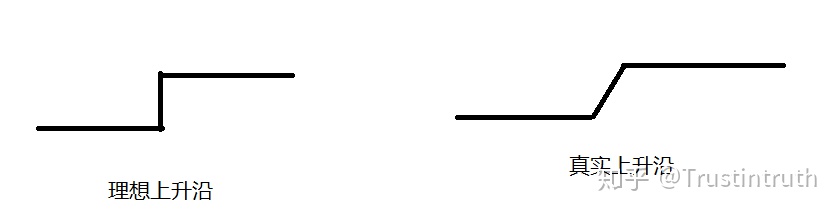

最近在做项目中遇到了一个问题,首先我们知道信号的边缘不会像我们想要的那么陡峭,而且不会像我们想的一样准时到达。

那如果是在多位翻转时,各个信号到来时间也可能不同,所以我们的多位变化时会发生误码的概率大大增加,例如位宽为5的信号由11111到00000变化时有可能会是是这样

11111——11011——11010——10010——00010——00000

出于对稳定性的考虑,我们采用格雷码,尤其是在FSM的状态我们经常使用格雷码表示。

格雷码在一组数的编码中,若任意两个相邻的代码只有一位二进制数不同,则称这种编码为格雷码(Gray Code),另外由于最大数与最小数之间也仅一位数不同,即“首尾相连”,因此又称循环码或反射码。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1132

1132

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?