今天又是没有课的一天。。

一、Verilog内部的基本门级元件

| 元件符号 | 功能说明 | 元件符号 | 功能说明 |

and or xor | 多输入端的与门 多输入端的或门 多输入端的异或门 | nand nor xnor | 多输入端的与非门 多输入端的或非门 多输入端的异或非门 |

| buf | 多输出端的缓冲器 | not | 多输出端的反相器 |

bufif1 bufif0 | 控制信号高电平有效的三态缓冲器 控制信号低电平有效的三态缓冲器 | notif1 notif0 | 控制信号高电平有效的三态反相器 控制信号低电平有效的三态反相器 |

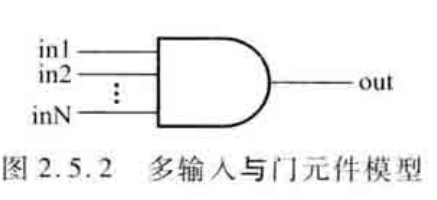

多输入的逻辑门:多个输入,一个输出。多输出门......

多输入门的输出不为高阻态z

多输入与门调用例举:

and A1(out, in1, in2, ..., inN);多输出门调用形式:

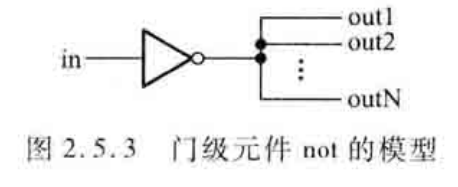

buf B1(out1, out2, ..., outN, in);not N2(out1, out2, ..., outN, in);三态门:一个门输出、一个数据输入、一个输入控制

输入控制信号无效时,输出为高阻态z

三态门调用形式:

bufif1 B1(out, in, ctrl);bufif0 B0(out, in, ctrl);notif1 N1(out, in, ctrl);notif0 N0(out, in, ctrl);二、Verilog基本结构

1、模块module

定义模块基本语法结构

module模块名(端口名1, 端口名2,端口名3,...);端口模式说明(input, output, inout); //说明部分 inout双向端口参数定义(可选);数据类型定义(wire, reg等);实例化低层次模块或基本门级元件; //逻辑功能描述部分,排序任意连续赋值语句(assign);过程块结构(initial和always) 行为描述语句;endmodule例

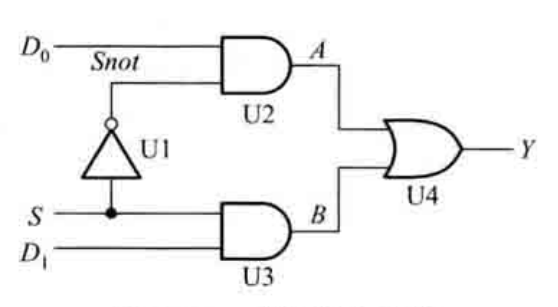

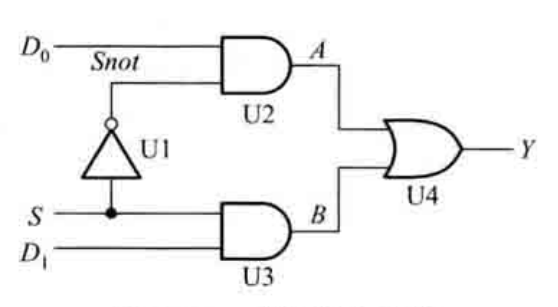

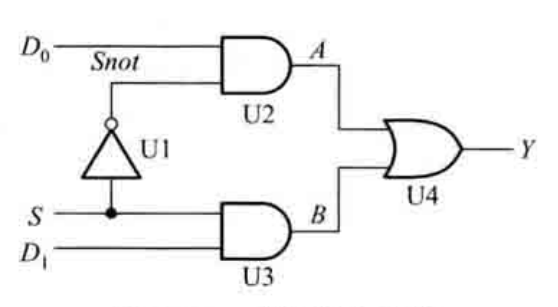

1、门级描述

/*module mux2to1(D0, D1, S, Y); //2选1数据选择器 input D0, D1, S; //输入端口声明 output Y; //输出... */module mux2to1(input D0, D1, S, output Y); wire Snot, A, B; //内部节点... //↓描述逻辑功能 not U1(Snot, S); and U2(A, D0, Snot); and U3(B, S, D1); or U4(Y, A, B);endmodule2、数据流描述

module mux2to1_dataflow(D0, D1, S, Y); input D0, D1, S; output Y; wire Y; //电路功能描述 assign Y = (~S & D0)|(S & D1); //★表达式左边变量的数据类型必须为wireendmodule3、行为描述(工作效率更高)

S=0时,Y=D0;S=1时,Y=D1

/*module mux2to1_bh(D0, D1, S, Y); input D0, D1, S; output Y; reg Y; //变量的数据类型声明 always@(S or D0 or D1) //S、D0、D1中有任何一个输入端信号变动都会执行 if(S==1) //if(S) Y=D1; Y=D1; else Y=D0; //★表达式的左边必须为reg型数据类型endmodule*/可简化为↓module mux2to1_bh( input D0, D1, S, output reg Y); always@(D0, D1, S) begin if(S) Y=D1; else Y=D0; endendmodulealways@(S or D0 or D1)无分号,表示括号中任一个变量发生变化时,下面的赋值语句会被执行一次,执行完最后一条语句后,执行挂起,always再次等待变量发生变化。

括号内的为敏感变量。

组合逻辑电路中所有输入信号皆为敏感变量。都应写在括号内。

过程赋值语句只能赋值寄存器型变量,输出Y的数据类型定义为reg。

always@(*) 对比 assign

| 被assign赋值的信号为wire型 | 被always@(*)结构块下的信号定义为reg型 这里的reg并不是一个真正的触发器,只有敏感列表为上升沿出发的写法才会综合为触发器,在仿真时才具有触发器的特性。 |

| 连续赋值语句assign可以并行执行,相当于描述的是连线 | always@(*)描述组合逻辑时, begin和end之间是串行,一条一条语句执行 |

三、仿真

搭建测试平台Test Bench

矢量波形文件(.vwf)

明天再做了,今晚弄不出来了。。

晚上吃的杂酱米线,太油了,下次换一家!

4229

4229

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?