目录

1.固件开发

1.1串口打印调试信息

在固件开发时,利用串口打印调试信息,获得代码执行情况的指示。固件中,用于打印调试信息的串口配置如下,其中波特率的设置为112500,停止位为1,无校验位。在程序设计过程中,可在适当位置调用CyU3PDebugPrint函数打印信息,固件工程中可查看该函数原型。赛普拉斯官方代码非常规范,很多地方会进行返回值有效性检测并打印相关信息,在数据发送过程中,可以关注串口信息,看是否数据有溢出或丢失,如下。

CyU3PUartConfig_t uartConfig;

CyU3PMemSet ((uint8_t *)&uartConfig, 0, sizeof (uartConfig));

uartConfig.baudRate = CY_U3P_UART_BAUDRATE_115200;

uartConfig.stopBit = CY_U3P_UART_ONE_STOP_BIT;

uartConfig.parity = CY_U3P_UART_NO_PARITY;

uartConfig.txEnable = CyTrue;

uartConfig.rxEnable = CyFalse;

uartConfig.flowCtrl = CyFalse;

uartConfig.isDma = CyTrue;

apiRetStatus = CyU3PUartSetConfig (&uartConfig, NULL);

例如在下发IO配置时调用串口打印函数返回值,示例如下:

CyU3PReturnStatus_t apiRetStatus = CY_U3P_SUCCESS;

apiRetStatus = CyU3PGpioSetSimpleConfig(59, &gpioConfig);

if (apiRetStatus != CY_U3P_SUCCESS)

{

/* Error handling */

CyU3PDebugPrint (4, "CyU3PGpioSetSimpleConfig failed, error code = %d\n",apiRetStatus);

CyFxAppErrorHandler(apiRetStatus);

}1.2控制传输BUG

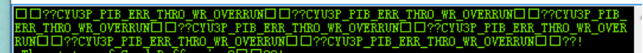

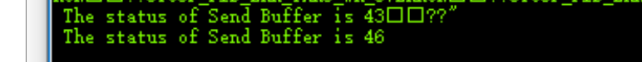

在控制传输实现既定方案时,在调用CyU3PDmaChannelSetupSendBuffer函数时有一个返回值为43的错误,随后调用CyU3PDmaChannelWaitForCompletion函数有一个46的错误,串口中打印错误信息如下:.

对于返回值的含义不得而知,但是可以就具体的返回值错误与赛普拉斯工程师交流,交流结果如下,结论是使用override mode(我将其理解为手动)DMA通道时,不能调用CyU3PDmaChannelSetXfer()函数的调用,运行正常。

1.3同步传输BUG

在同步传输固件程序的开发过程中,查看串口信息,遇到error code 77,如下。与官方工程师沟通的结论是,同步端点的设置出现故障,在端点属性中的isoPkts的值被设置为大于1时,端点不应为0x81,应为0x83或0x87。修改同步端点为0x83之后,故障修复。沟通过程附下图。

![]()

1.4其他注意

在烧写固件程序时应注意,如果是USB Boot的启动方式,应该先烧写固件程序,在烧写FPGA程序,否则会因具体的不同的FPGA程序出现意外结果。如果是将二者的代码都写在掉电不适的存储芯片中,则此处无风险。

在设置水印值的时候,官方文档中明确了有关水印值的计算公式,作为开发者应该注意,不同的水印值,应该对应有一个最小的数据包长度,如果数据包太短,则水印值标志无法正常工作。有两种解决办法,一是填充dummy数据在应用层区分;或者可以把GPIF总线位宽调整为最小位宽8位。当然如果数据收发两端明确了要传输数据的长度,也无需使用水印值,但通常不推荐这样做。

基于AN65974的固件程序,是兼容USB2.0和USB3.0的,不同模式下缓冲区大小设置不同,那么在FPGA端捕捉缓冲区的切换,计算缓冲区的大小,以此判断潜在的USB传输数据线故障(有可能数据线只能在2.0模式)。

USB固件的启动方式是根据PMODE三个管脚的输入状态决定的,应在USB Boot启动方式下,为存储器固化代码。

2.上位机

在上位机开发篇中介绍了不同长度的数据包有不同的发送方式,control center作为官方自带的上位机,他的发送如何进行呢?为了解释数据传输过程中出现的现象,一探究竟。(固件中缓冲区的大小为16KB)在进行读测试的过程中发现,每当上位机发送1024B数据时,FPGA检测FLAG不动作,但当我连续16次下发1024B数据时,FLAG正常工作。于是进行了以下测试。如表所示。

| 数据长度 | 64 | 1024 | 1074 | 1088 | 128 | 256 | 512 | 2048 | 4096 | 8192 | 16384 |

| 下发状态 | 成功 | 失败 | 成功 | 成功 | 成功 | 成功 | 成功 | 失败 | 失败 | 失败 | 成功 |

可以看到,control center可以下发短包,数据为1024及1024倍数且小于缓冲区大小的时候,control center并不会发送零包,因此数据在套接字中无法commit,因此开发过程中遇到这些现象是正常现象。

3.FPGA

3.1FLAG Bug

首先应该明确FLAG工作的原理,Flag的本质是用来进行数据流控制的。当缓冲区非空的时候,相关的Flag才会发生状态的改变,通过指示缓冲区的状态用此来进行流控制。接收到数据时缓冲区不为空,相关标志开始工作,那么何时接收到数据呢?A DMA buffer will be received by the USB socket and committed to the P Port only if any of the following cases are satisfied:

1. The buffer is full (16KB is received).

2. Short packet is received from host.

3. ZLP is received from host.

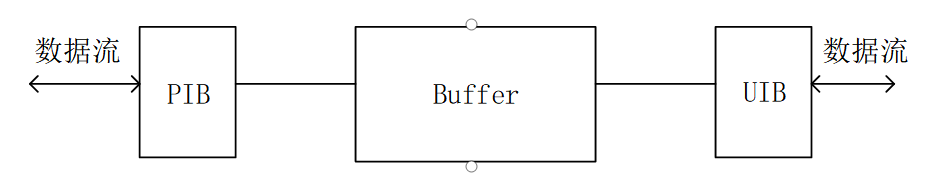

对于另外一个方向的数据同样也是如此。这个接收到数据指的是,只有当这三种情况发生的时候,flag才会发出状态的反馈,即才会改变状态。怎么理解呢?由于fpga和上位机之间是固件架起了通道,这个通道包括了缓冲区、DMA通道,套接字,物理线程,GPIF II接口。正常理解是一旦上位机发数,那么数据会立即传递到缓冲区,置位标志,阻塞数据流。但其实连接缓冲区的左右两端是PIB套接字和UIB套接字,只有当套接字把数据放到缓冲区并到达对端的套接字时(这个动作官方手册里面称之为commit)的时候,标志才会置位,而这个过程并不是只要有数据就会触发,而是有条件的,条件就是上述的3个条件,只有满足其中一个条件时,数据才能从套接字上取到缓冲区里并经DMA通道到达对端。套接字的工作原理示意图如下所示:

基于明确的Flag的工作原理,介绍碰到Flag工作不正常的排查思路。首先检查slcs、sloe、slrd、slwr信号时序是否正确,有一种可能是,这几个信号时序错误,导致流控制失败,发生了空读或者空写,导致了flag工作不正常。确保地址线fx3_addr驱动正常,地址出错,会导致flag不正常。确保GPIF的设置与FPGA代码是相匹配的,具体表现在局部标志初始为高还是为低是在GPIF II里面设置的。(The DMA_READY flag starts indicating the status of the DMA buffer only when the host has started transferring data to FX3. The partial flag is observed to reflect the status of the buffers only after one full DMA buffer is read out. So, when the state machine starts, the partial flag cannot be monitored to know the empty status of the buffers.)使用cypress官方的stram OUT代码进行测试,看flag是否正常,这是为了排除硬件问题。排查pclk时钟是否稳定。排查固件中的数据流通道是否正确。

3.2数据丢数

任何通信接口传输数据出现数据丢失的情况是最棘手的。具体开发过程中出现过各种各样的丢数、误码。应该首先确保控制信号的时序是正确的,然后结合硬件具体的布线确定各信号是满足Cyusb3014芯片的时序要求的。最后应该确保FPGA的代码是meet the timing requirements。大多数情况还是时序约束不满足导致的。

4.方向

自己也是为了完成工作任务浅尝辄止,不够深入。经过长时间的摸索,对于想要深入研究的朋友提供几个方向。1,关注USB4的发展,期待实现”大一统”;2.同步传输的应用可以尝试开发,有着巨大的独特优势,保证带宽;3.UVC应用;4.我的上位机使用的cylib相当的ugly,使用说明像是东拼西凑的,功能相当的不完善,试着使用那个动态链接库;5.感觉使用摄像头直接连usb芯片是个很有意思的应用;6.芯片中还有很多扩展的内容,看看能否在这个基础上做一些应用,有一些新奇的想法,集成了一颗arm9,简直是宝藏。

5.传送门

● 我的主页

END

🔈文章原创,首发于CSDN论坛。

🔈欢迎点赞❤❤收藏⭐⭐打赏💴💴!

🔈欢迎评论区或私信指出错误❌,提出宝贵意见或疑问❓。

2565

2565

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?