生成语句可以动态的生成Verilog代码,这一声明语句方便了参数化模块的生成。当对矢量中的多个为进行重复操作时,或者当进行多个模块实例引用的重复操作时,或者根据参数的定义来确定城西中是否应该包括某段verilog代码的时候,使用生成语句能够大大简化程序编写的过程。

生成语句能够控制变量的声明,任务活函数的调用,还能对实例引用进行全面的控制。编写代码时候必须在模块中说明生成的实例范围,关键字generate endgenerate用来指定改范围。

生成实例可以是以下的一个或者多个类型:

- 模块;

- 用户定义原语;

- 门级原语;

- 连续赋值语句

- Initial和always块。

生成的声明和生成的实例能够在设计中被有条件的条用(实例引用)。在设计中可以多次调用(实例引用)生成的实例和生成的变量声明。生成的实例具有唯一的标识名,因此可以用层次命名规则引用。为了支撑结构话的元件与过程块语句的相互连接,verilog语言允许在生成范围内声明下列数据类型:

- net,reg

- Integer,real,time,realtime

- Event

生成的数据类型具有唯一的标识名,可以被层次引用。此外,究竟是按照次序或者参数名赋值的参数重新定义,还是只用defparam声明的参数重新定义,都可以在生成范围中定义。

任务和函数的声明也允许出现在生成范围之中,但是不能出现在循环生成当中。生成任务和函数同样具有唯一的标识符名称,可以被层次引用。

在verilog中有3中创建生成语句的方法,他们是:

- 循环生成;

- 条件生成;

- Case生成;

1 循环生成语句

循环生成语句允许使用者对下面的模块活模块项进行多次实例引用:

- 变量声明;

- 模块;

- 原语;

- 连续赋值语句

- initial和always块

从例子中可以观察到下面几个有趣的现象:

- 在仿真开始之前,仿真器会对生成块中的代码进行展平,将生成块转换为展开的代码,然后对展开的代码进行仿真。因此,生成块的本质是使用循环内的一条语句来代替多条重复的Verilog语句,简化用户的编程。

- 关键词genvar用于声明生成变量,生成变量只能用在生成块之中,在确立后的仿真代码中,生成变量是不存在的。

- 一个生成变量的值只能有循环语句来改变。

- 循环生成语句可以嵌套使用,不过使用同一个生成变量作为索引的循环生成语句不能相互嵌套。

- Xor_loop是赋予循环生成语句的名字,目的在与通过它对循环生成语句之中的变量进行层次话引用。

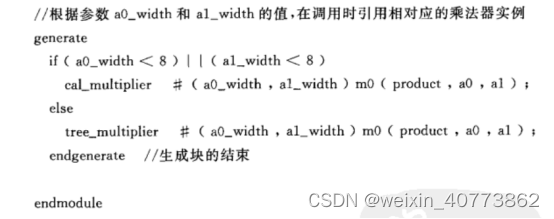

2 条件生成语句

条件生成语句类似于if_else_if的生成构造,该结构可以在设计模块中根据经过仔细推敲并确定表达式,有条件的调用以下verilog结构:

- 模块;

- 原语;

- 连续赋值语句;

- initial或always块。

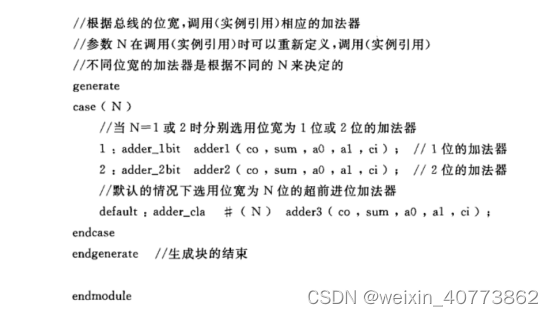

3 case 生成语句

4319

4319

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?