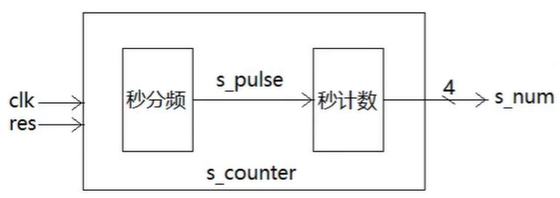

秒计数器(s_counter,0-9)

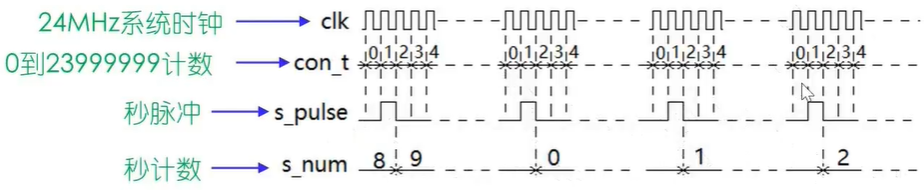

假设clk是24MHz系统·时钟,秒分频产生秒脉冲s_pluse;

秒计数模块对秒脉冲计数,计数范围0-9,秒计数结果s_sum(位宽4)。

系统时钟:24MHz

基于系统时钟的计数:cont_t(计数范围0-24000000-1),每循环一圈就是1秒。

秒脉冲:触发器,每看到0就置为1,不是0就置为0,就可以得到一秒一个脉尖冲,称为秒脉冲

秒计数:对秒脉冲进行计数,看到一个秒脉尖冲加一。(9加1变成0)

`timescale 1ns/10ps//testbench时间单位

module s_counter(

clk,//时钟

res,//复位

s_num//秒计数,输出

);

input clk;

input res;

output[3:0] s_num;

parameter frequency_clk=24;//24MHz;方便修改其他数值,比如16Mhz;

reg[24:0] con_t;//秒脉冲分频计数器;

//24MHz频率24000000,二进制25位

reg s_pulse;//秒脉冲尖;

reg[3:0] s_num;

always@(posedge clk

本文介绍了一种基于24MHz系统时钟的秒计数器设计方法,包括秒脉冲产生及秒计数逻辑,并展示了Verilog代码实现及数码管显示方案。

本文介绍了一种基于24MHz系统时钟的秒计数器设计方法,包括秒脉冲产生及秒计数逻辑,并展示了Verilog代码实现及数码管显示方案。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6461

6461

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?