一个学习信号完整性仿真的layout工程师

在我们的进行layout设计时,尤其是在一些差分走线上,经常会遇到串联电阻或者电容的情况,可能在信号速率不高或者spec要求不严格时,我们会忽略独立器件另一端较短走线的长度延时,但是在一些告诉信号的传输下是要把这段走线考虑进行去的,这就会涉及到Allegro中的XNet的设置,今天就和大家简单总结一下:

第一步:

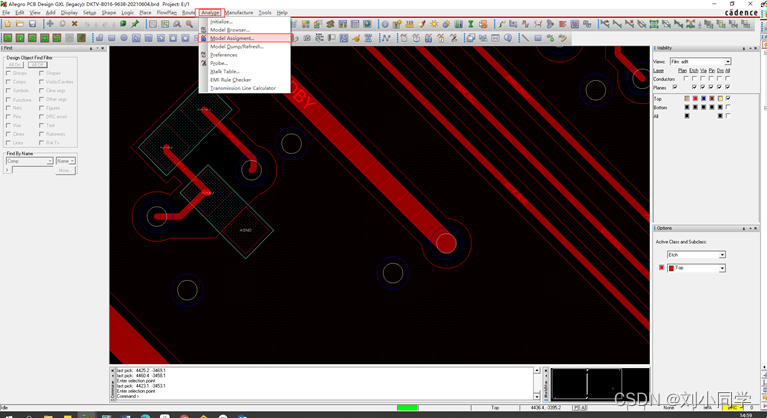

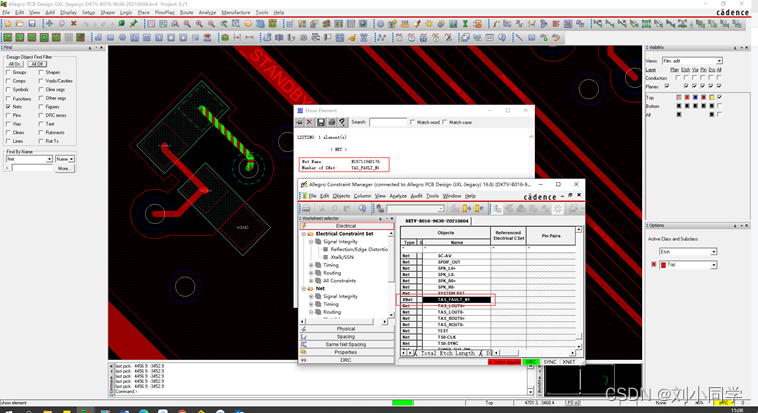

在Allegro的PCB Editor的菜单下选择点击Analyze,如下图操作:

第二步:

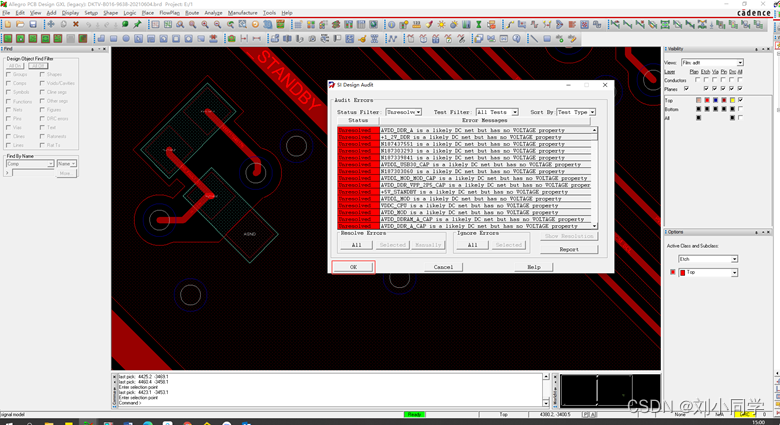

弹出如下对话框,点击OK,如下图操作:

第三步:

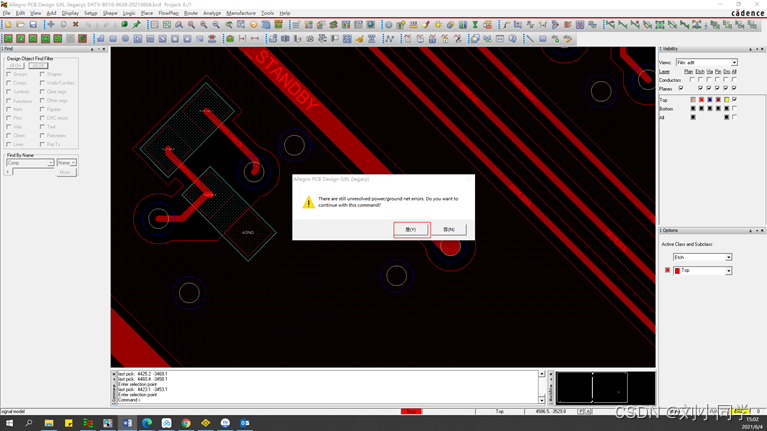

弹出如下对话框,点击是,如下图操作:

第四步:

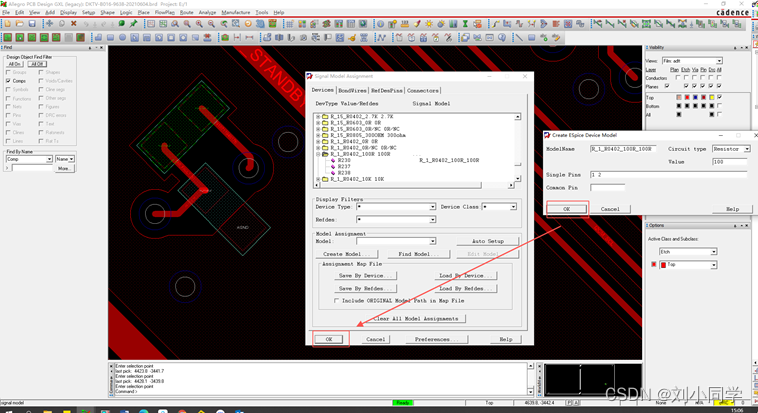

选择串联两个信号网络的独立器件,点击creat model ,再点击OK,如下图操作:

按照对话框的属性设置独立器件的参数,包括引脚数量,value等,如下图操作:

第五步:

设置完成之后会弹出如下对话框,表示创建成功:

第六步:

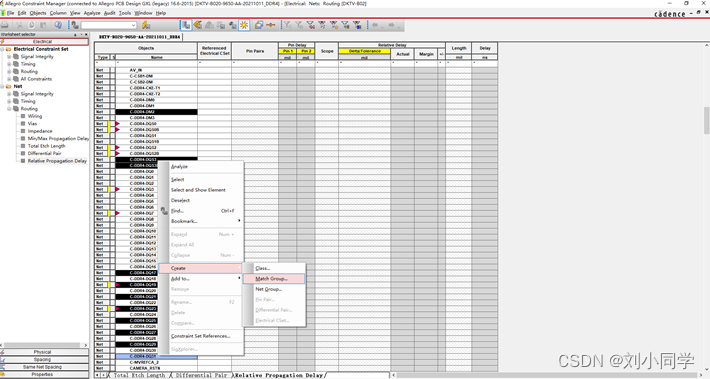

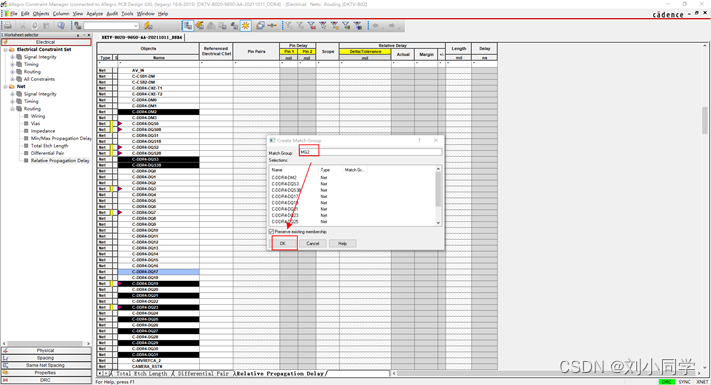

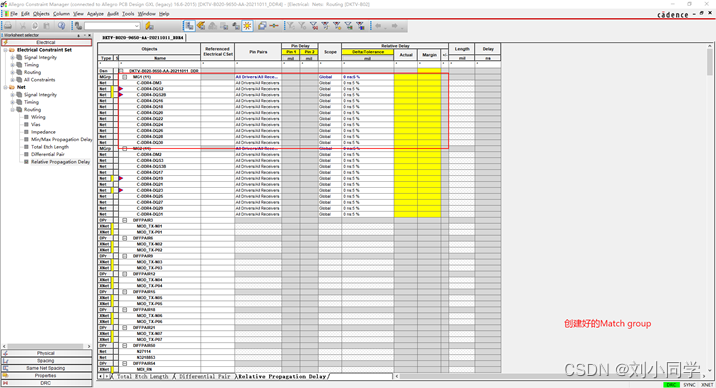

选中要添加到Match group中的网络,右键选择creat-Match group,如下图操作:

以上操作流程主要是自己在工作中的使用,大家可能会有不同的方法

如有雷同或错误,希望各位大神留言指正,感谢!!!

1125

1125

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?