1.RS485定义:

增强型低功耗半双工RS-485(Enhanced Low Power Half-Duplesx RS-485 Transceivers)

RS-485是一种串行通信标准,也被称为EIA-485或TIA-485。它定义了在多个设备之间进行数据传输的电气特性、信号线路和通信协议。

2.RS485通信电平:

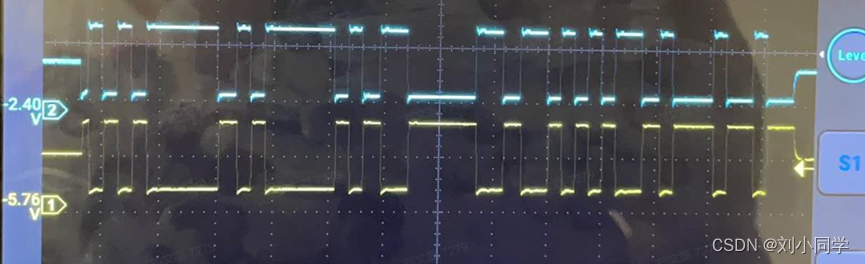

逻辑 1:两根信号线(A+和B-)的电压差在 +2V~+6V 之间。

逻辑 0:两根信号线(A+和B-)的电压差在 -2V~-6V 之间。

3.RS485通信线:

输出信号:传输线只有两根A和B,当发送信号时为T+/T-,当接收信号时为R+/R-;

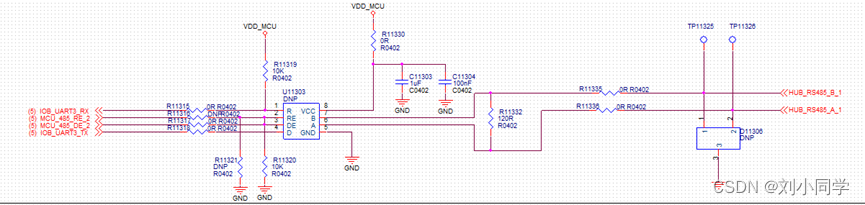

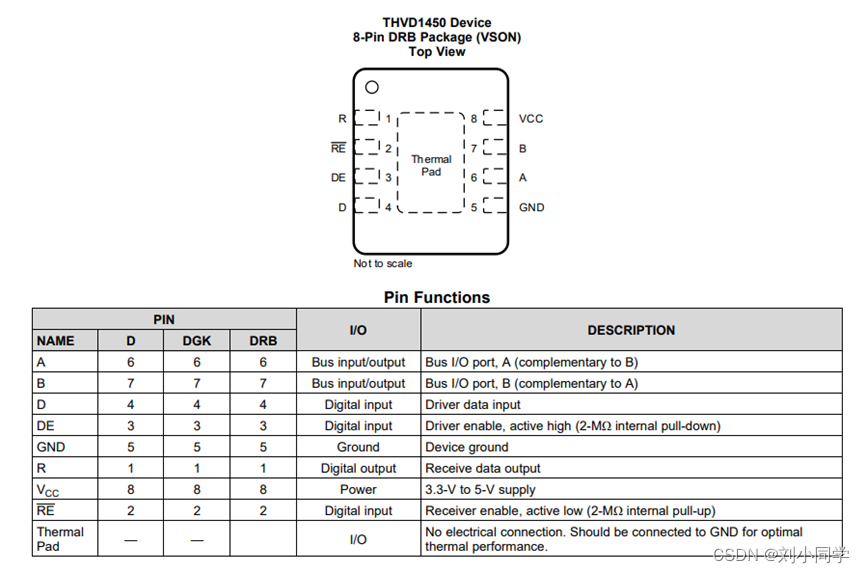

输入信号:RE和DE接到同一个GPIO上,RE是输入控制,低有效,DE是输出控制,高有效。R接到串口的RX上,D接到串口的TX上。

异步通信数据以字节的方式传送,在每一个字节传送之前,先要通过一个低电平起始位实现握手。为防止干扰信号误触发RO(接收器输出)产生负跳变,使接收端MCU进入接收状态,建议RO外接10kΩ上拉电阻。

4.RS-485通信协议:

RS-485通信协议定义了物理层和数据链路层的规范,包括信号电平、线路连接、传输速率、数据帧格式等。以下是RS-485通信协议的一些关键特点:

- 物理层规范:RS-485使用差分信号传输数据,其中两根线分别为正向和反向信号线(A线和B线)。这种差分传输方式可以提高抗干扰性能,并允许实现较长的通信距离。

- 线路连接:RS-485可以支持多个设备通过同一条总线进行通信,每个设备在总线上有一个唯一的地址。通信可以是点对点的,也可以是多点通信,其中一个设备作为主设备(主机)控制通信过程。

- 传输速率:RS-485支持多种传输速率,通常在2.4 kbps到10 Mbps之间。具体的传输速率取决于设备的能力和通信距离。

- 数据帧格式:RS-485通信协议定义了数据帧的格式,包括起始位、数据位、校验位和停止位。常见的数据格式有ASCII码和Modbus等。

- 抗干扰能力:RS-485采用差分信号传输,可以有效抑制共模噪声和电磁干扰。此外,它还支持硬件流控和奇偶校验等机制,以增强数据传输的可靠性。

- RS485 通信采用差分信号传输,通常情况下只需要两根信号线就可以进行正常的通信。在差分信号中,逻辑0和逻辑1是用两根信号线(A+和B-)的电压差来表示。

- 在 RS485 通信网络中,通常会使用 485 收发器来转换 TTL 电平和 RS485 电平;通常在这些节点中只能有一个主机,剩下的全为从机。在总线的起止端分别加了一个 120 欧的匹配电阻。

5.转换芯片:

1. 起到电平转换的作用,通常TX和RX端的电平是3V3,但是A和B两端的电压相对高出2-3倍(根据使用的芯片不同,电压不同)

2. 起到隔离的作用,因为A和B有可能接到外围线束,有可能烧坏单片机引脚端;

6.备注:

硬件层协议:规定 线上的定压多少V代表0,多少V代表1。使用都多少根线进行传输,选择使用什么材质的线进行传输。

软件层协议:指的是通讯双方在软件编码方面约定的通讯规则

以上资料主要是本人在设计中和网络搜索整理而成

如有雷同或错误,希望各位大神留言指正,感谢!!!

上一篇文章:硬件设计 之 M.2接口常用知识 链接如下,大家可以点击查看哟 , 链接: link

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?