一、前情提要

上一节内容介绍了LabVIEW中比较实用的ngc文件,并通过分析底层代码的编写进一步说明了LabVIEW中IP集成节点导入与编写方法以及LabVIEW图形化的优点,本节内容将手把手带大家编写一个频率计实验的IP集成节点。

【LabVIEW FPGA图形化】 ngc、edf网表文件的编写:LED流水灯

【LabVIEW FPGA图形化】 IP集成节点:按键控制LED

【LabVIEW FPGA图形化】IP集成节点:串口通信

二、FPGA蔡氏定律

FPGA有两条蔡氏定律:

1、FPGA不仅仅是FPGA。

2、FPGA的最终目的是做出可用的电路。

FPGA的学习脱离不了硬件电路,在本节实验中,由于FPGA是数字电路,在处理数字频率时只需要将信号连接到FPGA IO上即可实现采集功能,若信号为模拟信号,则需要在前级加入模数转换电路,这个模数转换电路不同于AD采集,只需要将模拟信号根据门限电平,分成0和1即可,最简单的就是LM393电压比较器,根据电压是否大于阈值电压决定输出-VCC或+VCC,若信号存在比较大的噪声,可以设置双限比较器或者滞回比较器实现模拟信号到数字信号的转换。

笔者试过将正弦波信号接入频率计IO,发现也有对应频率,且与原始信号频率呈一定的倍数关系,这种情况下的频率是不准的,频率大小下来的倍数也都不一样,本节实验仅限讨论数字频率,该数字频率可以用NE555产生。

三、频率计功能分析

频率的定义是:单位时间内完成周期性变化的次数,是描述周期运动频繁程度的量。

在定义中所指的单位时间,通常是1秒钟,通俗的说就是1秒钟变化的次数,FPGA通过去数这个变化的次数,最终得出频率的数值,因此底层代码可以分成两部分,一部分是计时1秒钟,另一部分是计数边沿的次数,因此我们的模块接口有信号输入端口和次数输出端口。

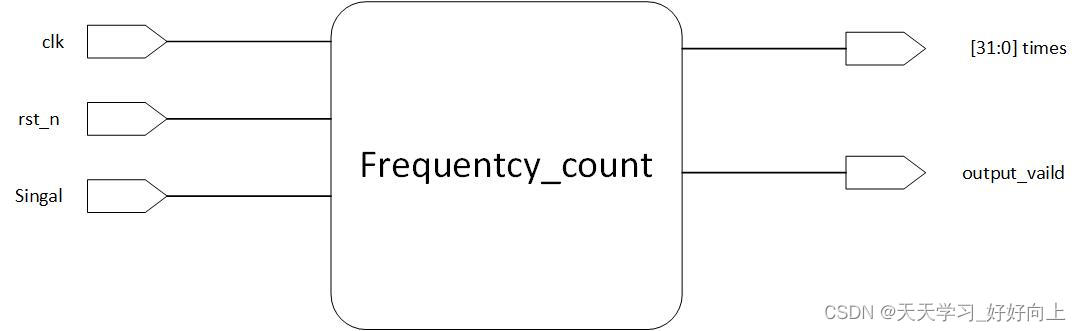

RTL视图:

由RTL视图可以看出,计数值输出范围为长整型,能够满足频率的计数需要,输出有效一个单位时间输出一次即一秒刷新一次数据,根据RTL的思路,我们可以编写出频率计数模块的代码:

module counter (

input clk,

input rst_n,

input Singal,

output reg [31:0] times,

output reg output_vaild

);

reg Singal_d0;

reg Singal_d1;

wire pos_single;

wire neg_single;

reg start_flag;

reg [31:0]cnt;

assign pos_single=~Singal_d1&Singal_d0;

assign neg_single=~Singal_d0&Singal_d1;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

Singal_d0<=1'b0;

Singal_d1<=1'b0;

end

else begin

Singal_d0<=Singal;

Singal_d1<=Singal_d0;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

start_flag<=1'b0;

else if(cnt==32'd49_999_999)

start_flag<=1'b0;

else if(neg_single==1'b1)

start_flag<=1'b1;

else

start_flag<=start_flag;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt<=31'd0;

else if(cnt==32'd50_000_000)

cnt<=1'b0;

else if(start_flag==1'b1)

cnt<=cnt+1'b1;

else

cnt<=cnt;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

times<=32'd1;

else if(start_flag==1'b1) begin

if(neg_single==1'b1)

times<=times+1'b1;

else

times<=times;

end

else

times<=32'd1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

output_vaild<=1'b0;

else if(cnt==31'd49_999_999)

output_vaild<=1'b1;

else

output_vaild<=1'b0;

end

endmodule

代码中通过打两拍对一个信号进行延迟判断边沿,这种操作是很常见了,为了更好的找到信号变化的时钟周期,我们通过组合逻辑得到信号变化的脉冲信号,FPGA根据这个脉冲信号进行计数,得到频率值。

编写好.v文件后需要修改综合参数,在Xilinx Specific Options中去掉 Add I/O Buffer选项,不添加I/O buffer并综合。

四、FPGA图形化程序编写

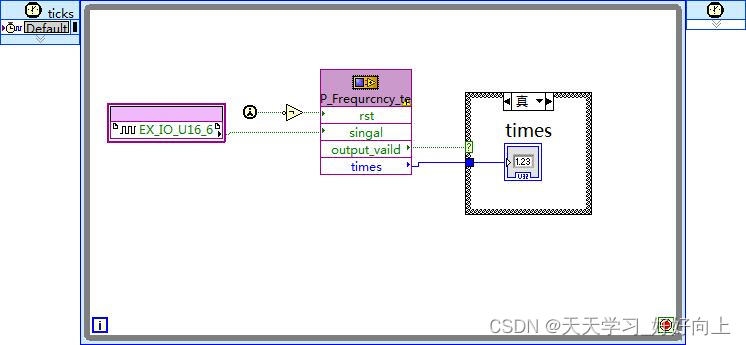

将上面程序生成的counter.ngc(要求.v的文件名与模块名字相同

) 添加到vi所在的工程目录下,调用IP节点,对其各个端口进行连线。

在上面的端口中,外部的信号输入于任意一个端口,由一个条件语句过滤出1秒后刷新的数据,LabVIEW的在线前面板可以看到当前频率的值。

总结

FPGA图形化编程其优势在于逻辑图形化,若不去考虑底层verliog,在顶层设计上FPGA的图形化编程是有优势的,可以更有效率的完成FPGA的设计,本节实验的Verliog网表文件和LabVIEW的vi均开源在 我的资源 如有需要可以下载学习。

4006

4006

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?