一、前情提要

本篇文章是就这一段时间LabviewFPGA制作IP集成节点遇到的问题而写的一篇综合bug的文章,包含了IP集成节点的常见错误类型,同时大家对IP集成节点有关的疑问可以看看往期文章。

【LabVIEW FPGA图形化】 ngc、edf网表文件的编写:LED流水灯

【LabVIEW FPGA图形化】 IP集成节点:按键控制LED

【LabVIEW FPGA图形化】IP集成节点:IIC通信实验

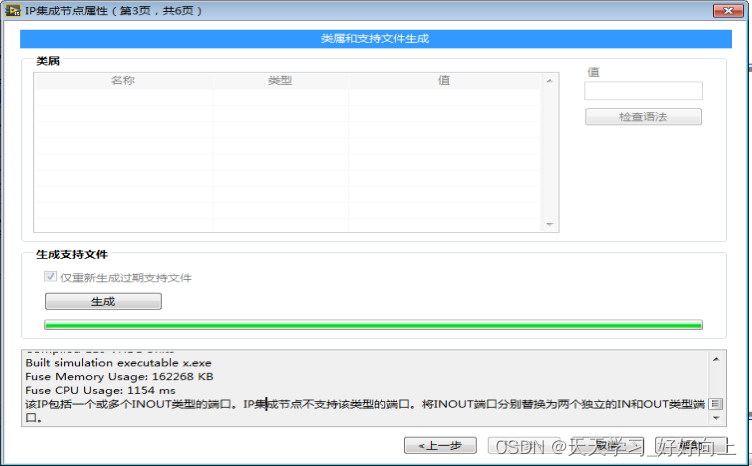

二、该IP包含一个或多个INOUT类型的端口,IP集成节点不支持该类型的端口。

出现上述问题原因主要在Verilog文件中有inout类型端口,但是在Labview下它的新型的EIO节点(Elemental I/O)不支持这一种三态门的形式,这也是Labview的IP集成节点与传统FPGA的不同之处。

一般来说NI工具包里的IO资源提供了就不可更改,在《Labview FPGA开发宝典》中,作者根据不同的bank分别封装了传统的IO节点和新型的EIO节点

BANK0~BANK2 属于 FPGA 里面传统的 EIO 节点,BANK3 属于 NI 后期推出的可以在一个 CLK 周期实现高阻态的新型 EIO节点模式。

以上针对新型EIO节点只在老版本的Labview下可用,对于新版本的Labview大家可以用以下的方法:

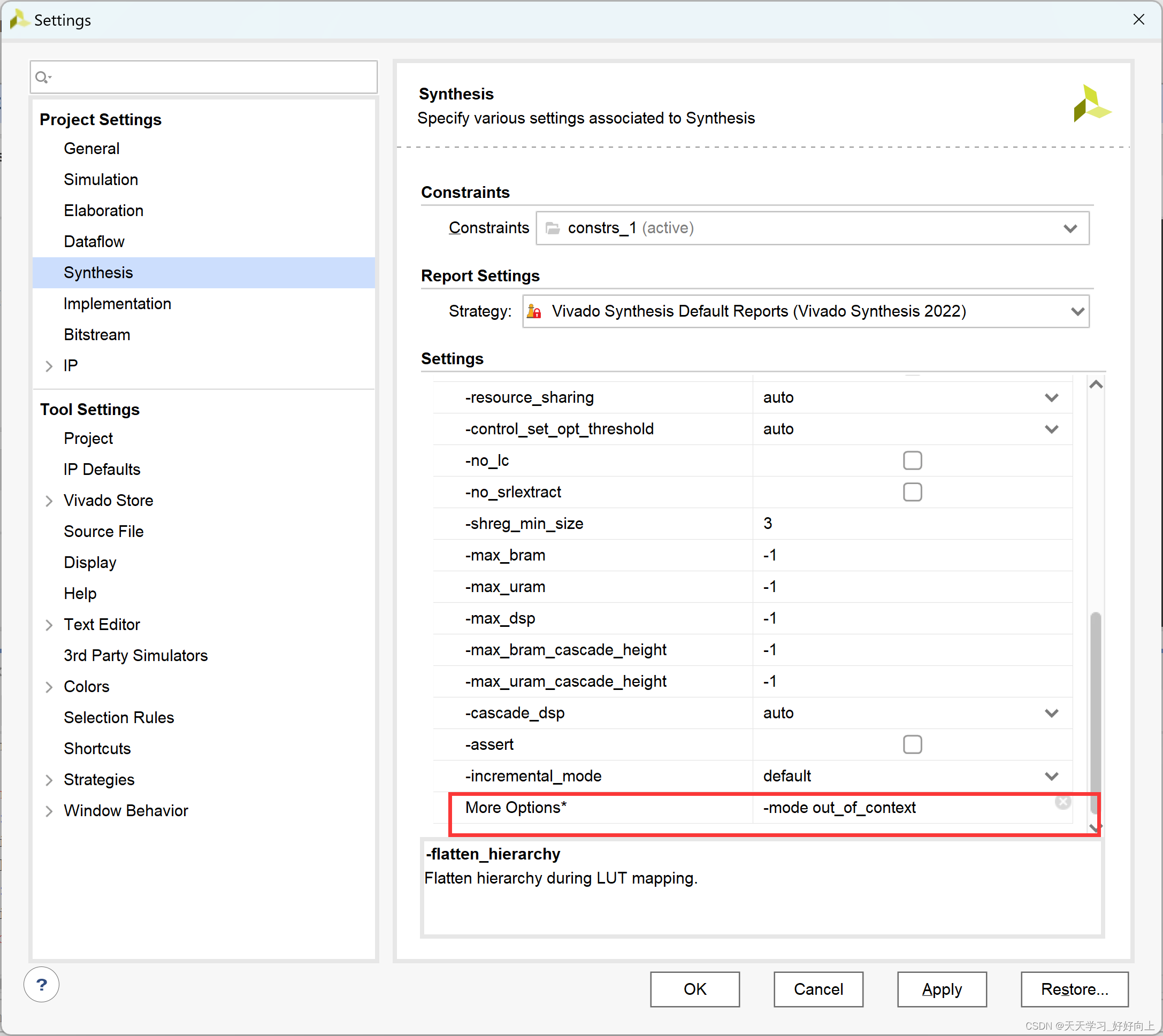

低版本 LabVIEW FPGA 2015 开发环境里面的编译器是 Vivado 2014.4,它支持所有 IO引脚都可以设置成新型 EIO 节点(实现三态:IN、OUT、ENA),但是 Vivado 2017.2 却不支持,即使 FPGA VI 程序什么 EIO 都不使用,编译的时候也一样会报错:[Place 30-415],类似以前在 ISE 里面遇到的,IO 全部占用了,布线过不了,其实是一个 BUG;Vivado 2014.4

搞定了,但是 2017.2 又回来了,就是模板 VHDL 文件里面全部使用新型 EIO 的话,高版本的 Vivado 反而不支持、有问题!

解决办法就是:

低版本的2015继续沿用之前的VHDL文件,高版本的LabVIEW FPGA(2018/2019/2020)将所有自定义终端模板 VDHL 文件里面的 OUT 和 ENA 禁用掉,默认保留全部的 IN 类型,这里的 IN 即代表了所有 FPGA 芯片 IO 引脚,可以直接在 LabVIEW FPGA VI 里面进行双向读写,反而变简单了,如果后续有一些用户需要用到部分 IO 引脚来实现单总线或者 IIC之类的,可以联系我们,我们会根据客户选择的 IO 引脚,将高版本 VHDL 文件里面的这些 IO 引脚的 OUT 和 ENA 取消注释,重新开放出来,毕竟一个 CLK 周期之内需要实现高阻态的 IO 数量不多。这样处理能最大程度减少客户的麻烦,同时也不需要修改模板文件里面的 XML 和XDC 文件,保持原样即可,针对高版本 LabVIEW FPGA 唯一要做的就是将所有的 OUT 和ENA 注释掉,用户把 IN 当成双向的 IO 口 EIO 节点就可以了,在 FPGA Target 项目里面新建 EIO 节点的时候,OUT 和 ENA 不用添加就可以了,反而简化了编程,跟 Pro1 里面的

Spartan6 差不多了。

遇到INOUT节点编译不过的情况下,大家可以去修改底层的.v文件,将节点类型分为IN OUT ENA分别引出,其实也是一种三态门的形式

三、源文件不适用于选择的FPGA系列

以上网表采用Vivado生成,但导入LabVIEW中出现错误,造成以上情况的原因有很多,应该按照顺序排查。

- 检查是否去掉IBUFG

- 是否调用Vivado的IP核,如果调用vivadoIP则网表不能用于Spartan6系列FPGA

- 检查顶层名称是否与edf网表名称相同,如果不同也会产生该错误

ISE编译器和Vivado编译器的编译逻辑不同,对代码的规范程度也要求不同,因此对于一些Verliog代码,NI的FPGA会出现不支持的情况,主要是因为VerliogHDL不够严谨,如果是VHDL就不会出现这个问题,但很多工程师都不会VHDL。所以遇到这个问题只能换编译器多试试。

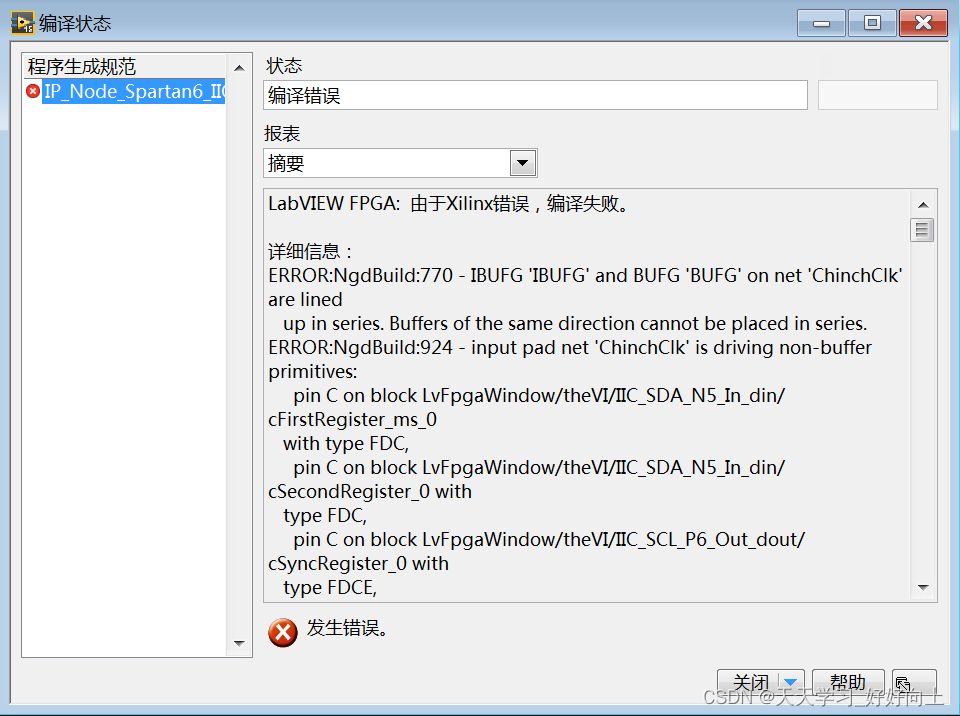

三、LabVIEW FPGA: 由于Xilinx错误,编译失败

若出现图示错误,主要原因是labview调用底层Xilinx编译器产生的错误,需要根据错误类型逐一排查,图示错误中说明了网表文件中有IBUFG,网表文件需要修改。

如果遇到其他错误,那也是有底层的编译器引起的,包括约束文件、clip模块、IO资源等。

5468

5468

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?