项目场景:

`基于Labview_for_FPGA的开发由于VHDL和Verilog以及ISE编译效率的原因,亟需一种提高开发效率的方法

问题描述

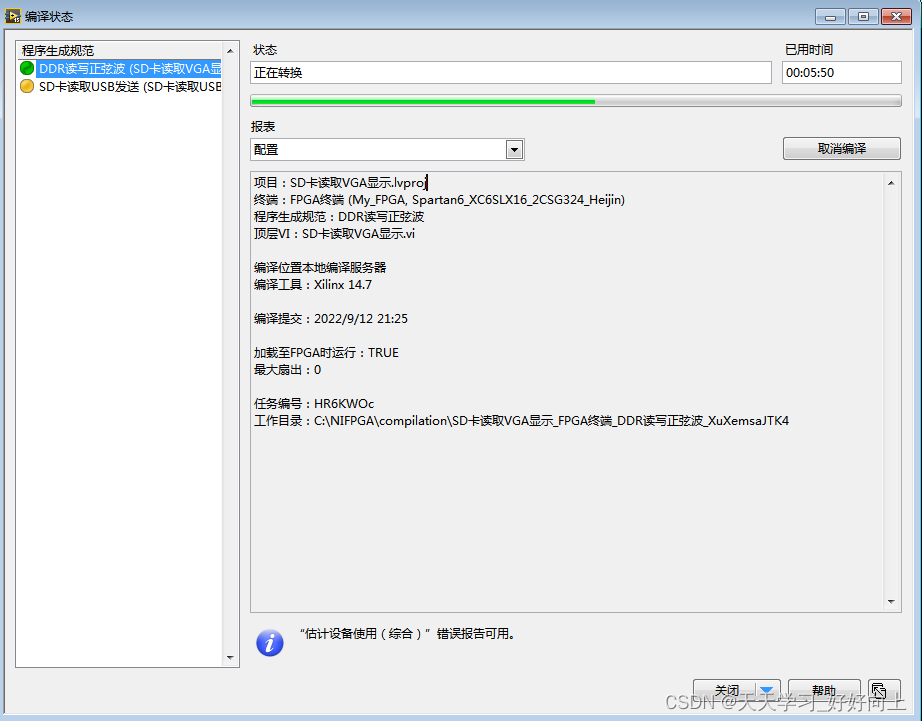

在Labview的编译过程中,小工程的编译效率较快,但大工程的编译效率非常非常慢,对于一些相对中等的LabviewFPGA的程序,编译时间长达1小时,由于该软件有在线前面板调试,对于一些工程上未定参数的调试大有裨益。但往往程序需要编译很长的时间,工程师不能把这些时间都浪费了。

基于编译时间长的原因,目前Labview也没有较好的解决办法,但对于工程师来说,编译的这几十分钟也是整理思路的好时间,构思下一个框架,验证上一个框架这是提高编程效率的好模式。

解决方案:

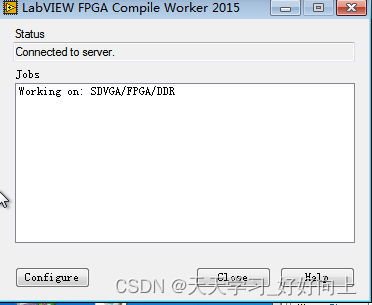

在编译程序的过程中,LabviewFPGA的Compile Worker会在后台进行编译,这个时候即使关闭工程也不影响程序在后台的编译。

在编译一个工程时,我们可以利用编译时间打开下一个工程进行调试修改,或者一个工程复制多个副本,同时对多个参数进行修改,这样可以大大的提高的编程的效率。

本文就是利用编译的空余时间编写的,如果有更好的方法欢迎在评论区留言评论,我们下期见。

2695

2695

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?