大概是数字电路的第三节、第五节有关Verilog的部分

Verilog HDL描述CMOS电路

重点是要搞清楚pmos、nmos、cmos三种。

关键字已经定义好了 例如:

nmos N1(漏极、源极、控制栅极)

cmos C1(输出信号,输入信号,TN 管控制信号,TP 管控制信号)

关键词supply1、supply0分别定义了电源线和地线。

像这种coms类似的Verilog内置的基本单元。

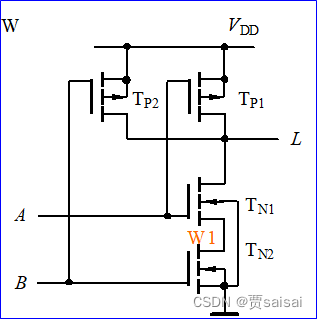

实例:试用Verilog语言的开关级建模描述CMOS与非门

module NAND2 (L,A,B); //IEEE 1364—1995 Syntax

input A,B; //输入端口声明

output L; //输出端口声明

supply1 Vdd;

supply0 GND;

wire W1; //将两个NMOS管之间的连接点定义为W1

pmos (L,Vdd,A); //PMOS管的源极与Vdd相连

pmos (L,Vdd,B); //两个PMOS管并行连接

nmos (L,W1, A); //两NMOS管串行连接

nmos (W1,GND, B); //NMOS管的源极与地相连

endmodule

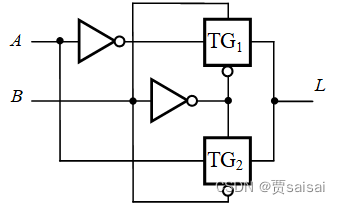

实例:用Verilog语言的开关级建模描述下列异或门

module mymux2to1 (A, B, L); //IEEE 1364—1995 Syntax

input A, B; //输入端口声明

output L; //输出端口声明

wire Anot, Bnot; //声明模块内部的连接线

inverter V1(Anot, A); //调用底层模块inverter,见下一页

inverter V2(Bnot, B);

cmos (L, Anot, B, Bnot); //调用内部开关元件

cmos (L, A, Bnot, B); //(output,input,ncontrol,pcontrol)

endmodule

Verilog语法补充

always

always@(posedge CP or negedge CR)这样的写法也可以用逗号替代or。

阻塞赋值

具体解释应用在:

FPGA学习笔记(三) 流水灯入门FPGA设计流程

2438

2438

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?