随着CMOS器件尺寸的持续缩小,栅介质泄漏电流、短沟道效应(SCE)等效应成为器件尺寸进一

步等比例缩小的障碍。短沟道效应使得器件的阈值电压变小,亚阈值泄漏电流增大

1 MOSFET 的短沟道效应

**短沟道效应简单来说就是导致器件的性能在器件沟道长度很小时而变得与长沟器件不同的效应。**并且很小的器件尺寸导致工艺制造难度的增加,造成了尺寸的不确定性,从而造成器件性能的不确定性。所以可以说我们在追求器件尺寸越来越小的过程,就是我们不断探索如何抑制短沟道效应的过程。

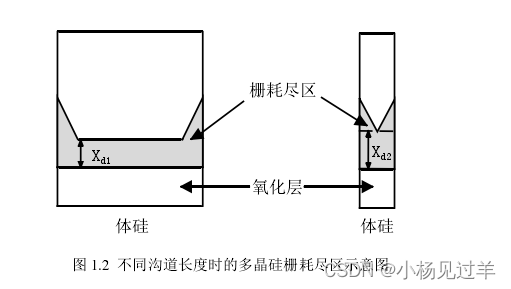

短沟道效应对器件性能的影响在器件沟道长度降低到与源结和漏结耗尽层的厚度相比拟时明显增强。此时,沟道内电势分布既受到栅压及衬底电压控制的纵向电场的影响,而且也会受到漏极偏压决定的横向电场的影响。这样的二维电场分布使源漏的共享电荷增加,从而使得栅对沟道耗尽区的控制力逐渐减弱,从而减弱了对源漏电流的控制,导致了阈值电压的减小,亚阈值斜率的衰减,泄漏电流的增加以及热载流子效应的出现。并且因为短沟道效应导致的穿通效应使电流不能达到饱和,在沟道内出现电势的二维分布并形成高电场。沟道内载流子的迁移率是跟电场有关的,电场的增大使载流子速度增大而达到饱和。电场继续增大,就使靠近漏端处发生载流子倍增效应引起阈值电压漂移,跨导下降等.

短沟道效应影响着晶体管方方面面的性能,我们可以从以下几个方面去分析和了解短沟道效应,从而探索解决的方法。

**

1.1 阈值电压漂移

**

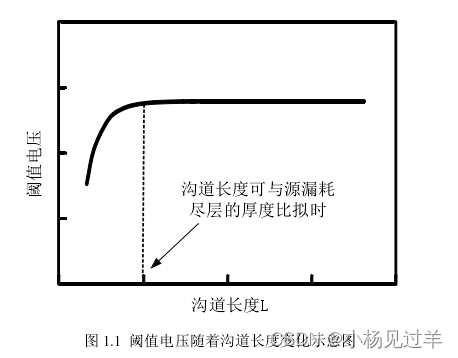

当器件沟道长度不断减小至深亚微米结点后,阈值电压有非常显著的下降,这就是短沟器件的阈值电压漂移。

在短沟器件中,随着漏端电压的升高,源漏的耗尽区在沟道中靠的非常近,从而降低了沟道区的电势,这种现象就成为漏至势垒降低(DrainInducedBarrier-Lowering,DIBL)效应。

沟道区势垒降低从而使得器件的阈值电压也随着源漏偏压升高而降低,DIBL

效应随着漏端偏压升高和沟道长度减小而变得越来越严重。通常我们可以用使器件分别工作在线性区和饱和区的漏端偏压下得到的阈值电压的差值来表示器件 DIBL 效应的严重程度。由于沟道区的势垒降低了,即使当栅源电压小于阈值电压时,也会有少数的载流子从源端漂移到漏端,也就是器件的亚阈值电流增大。因此 DIBL 效应造成了器件的阈值电压会随着源漏偏压的改变而发生漂移。

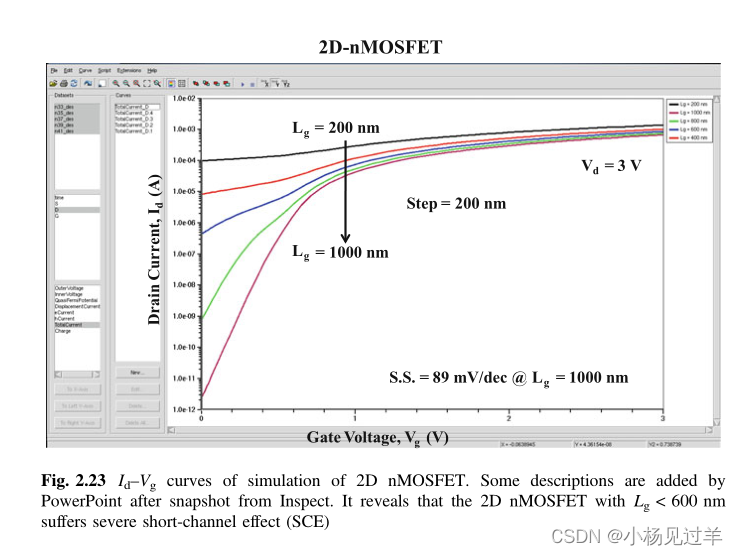

2D nMOSFET仿真的id–Vg曲线。结果表明,Lg < 600 nm的2D nMOSFET具有严重的短沟道效应

2 MOSFET

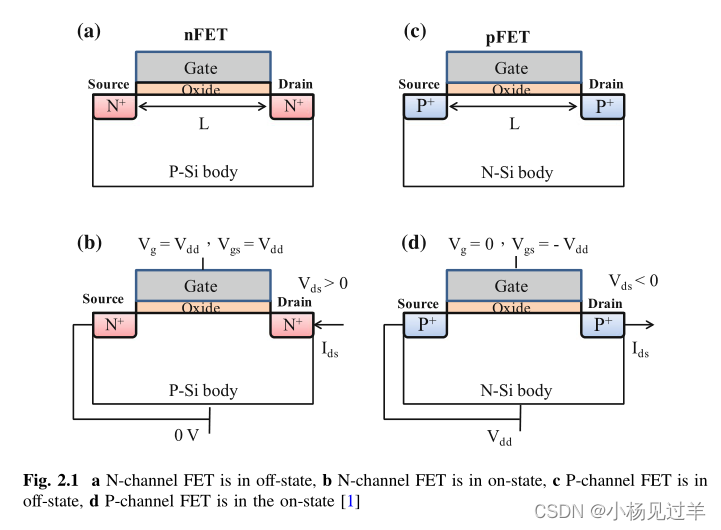

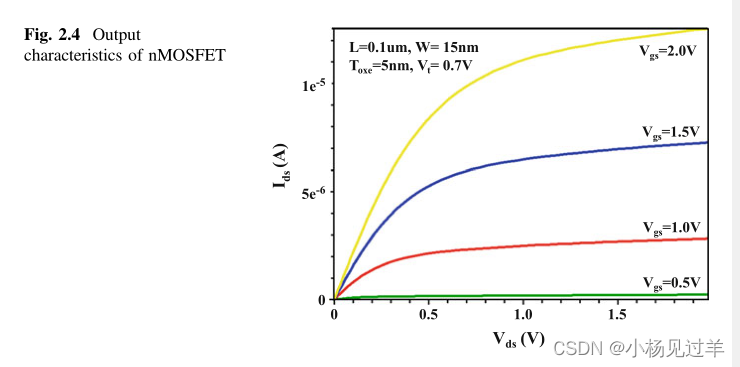

在正常操作中,系统通过向栅电极施加电压来导通MOS晶体管。当漏极上的电压增加时,漏极电流也增加,直到它达到饱和。饱和电流取决于栅极电压。

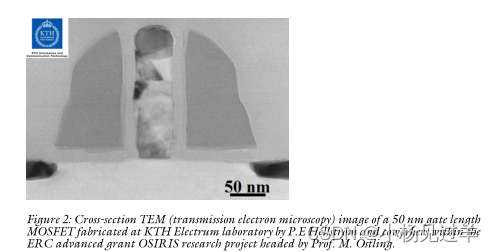

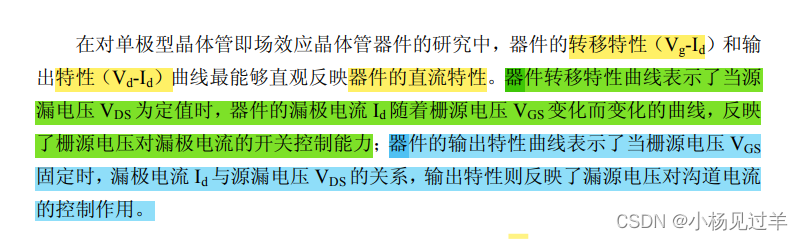

MOSFET(金属氧化物半导体场效应晶体管)是迄今为止最常见的半导体器件,它是所有商用处理器、存储器和数字集成电路的主要构建模块。自从大约40年前引入第一个微处理器以来,这种器件经历了巨大的发展,今天它被制造成具有22 nm和更小的特征尺寸。MOSFET本质上是一个小型化的开关。在这个例子中,源极和漏极接触(开关的输入和输出)都是到器件的重掺杂n型区域的欧姆(低电阻)接触。在这两个触点之间是一个p型半导体区。栅极接触位于p型半导体之上,与两个n型区域稍微重叠。它与半导体之间被一层薄的氧化硅层隔开,从而与下面的半导体形成一个电容器。向栅极施加电压会通过场效应改变其下方的局域能带结构。足够高的电压可以使半导体在栅极下面的薄层(沟道)中从p型变为n型。这被称为反型,并且沟道有时被称为反型层。沟道将半导体的两个n型区域与栅极下的薄n型区域连接起来。该区域的电阻明显低于在栅极电压产生反型层之前将源极和栅极分开的np/pn结的串联电阻。**因此,施加栅极电压可以用于将器件的电阻从高值改变到低值。显著电流开始流动的栅极电压被称为阈值或导通电压。**图1显示了一个MOSFET原理图,其中突出显示了主要的电气连接。图2显示了现代MOSFET器件的电子显微镜图像。

随着漏极和源极之间的电压增加,沟道承载的电流最终通过被称为夹断的过程而饱和,在夹断过程中,由于平行于表面的场的影响,沟道在一端变窄。**沟道宽度由栅极电压控制。**通常,对于给定的漏极电压,较大的栅极电压导致较宽的沟道,从而导致较低的电阻。此外,栅极电压越高,饱和电流越大。

3 FinFET特性分析

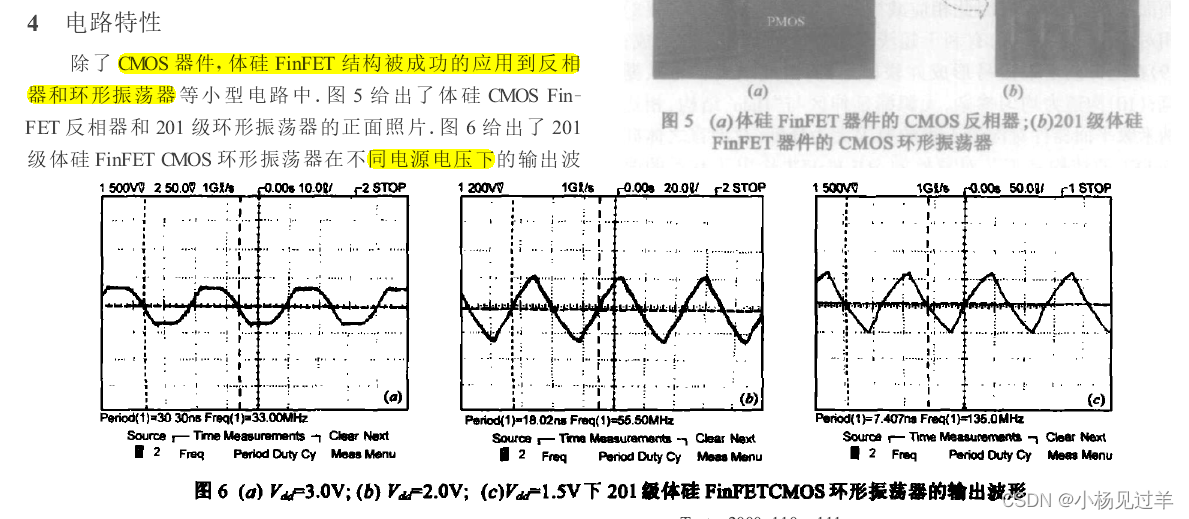

第二代14纳米FinFET的鳍形更高更窄,就像酒瓶形,用于提高栅极控制能力和更高的导通电流(ion)

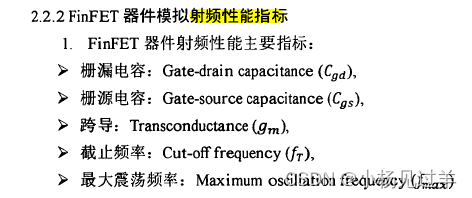

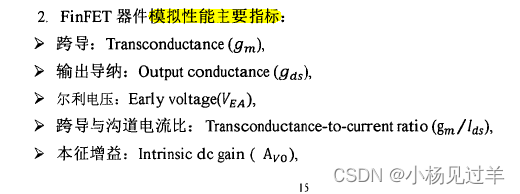

北邮2016 新型FinFET器件的模拟射频特性研究

4 高K栅介质

高k栅介质

https://wenku.baidu.com/view/1ee9c058a26925c52cc5bf7e.html

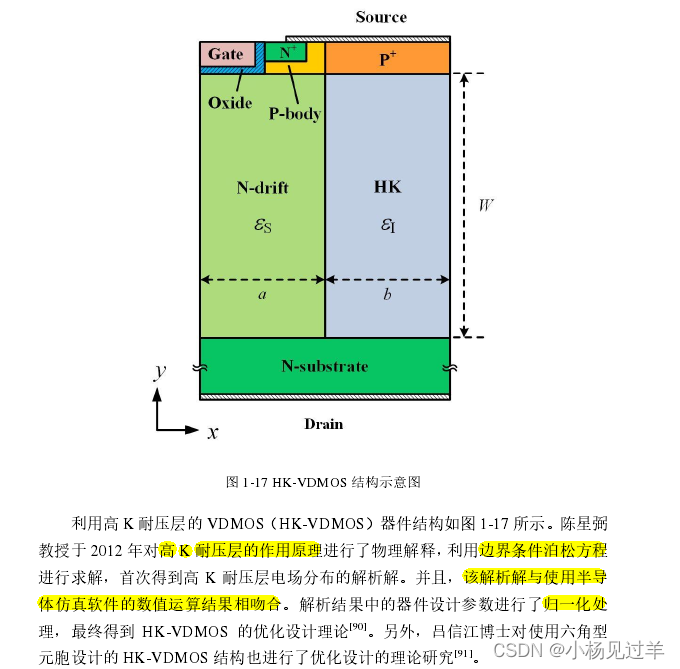

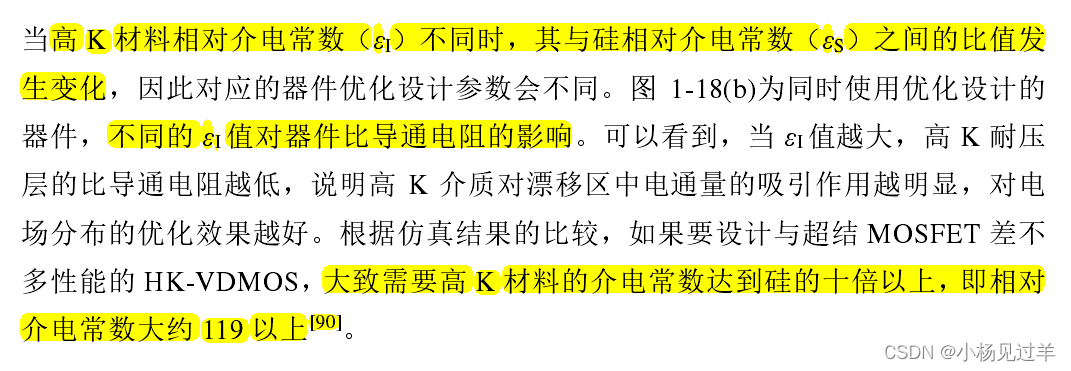

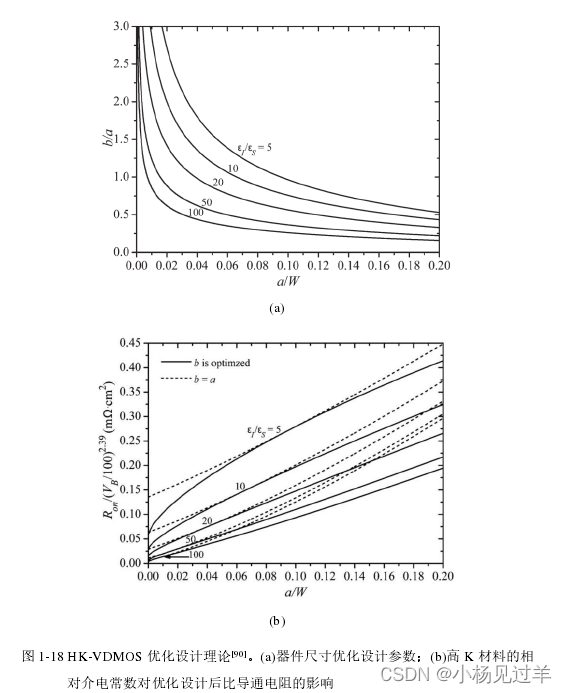

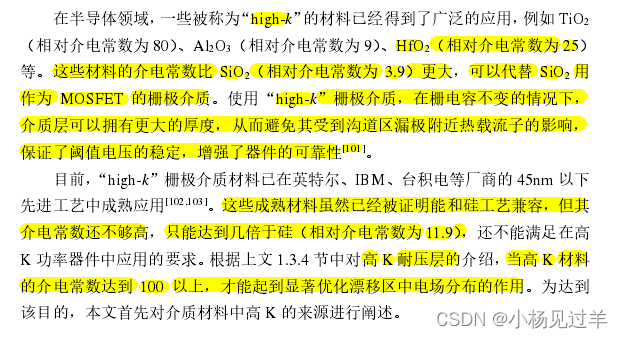

电子科大2020 新型高 K 功率器件中高 K 的研究(以上)

Yung-Chun Wu • Yi-Ruei Jhan 2018

3D TCAD Simulation for CMOS Nanoeletronic Devices

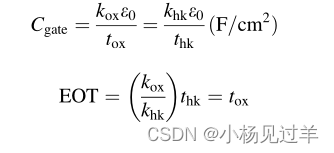

在等效氧化物厚度(EOT)相同的情况下,**使用高k材料可以降低栅极漏电流,**因为高k材料比传统的SiO2介电常数3.9更高,从而导致相同厚度下的相对电容更高。更高的栅极电容增加了更高的驱动电流

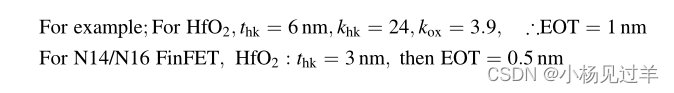

如何计算等效氧化物厚度(EOT):

各种材料的能隙与相对介电常数的关系

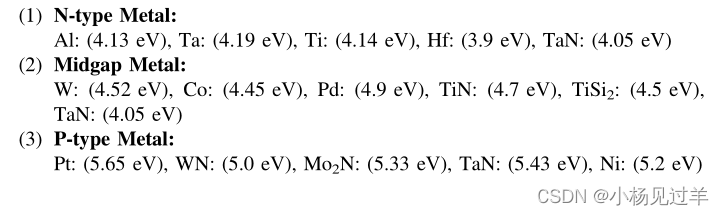

除了高k材料的影响,正在使用的不同金属栅的功函数(WF)也会影响Vth阈值电压

当前半导体技术中常用的各种金属的功函数值如图所示

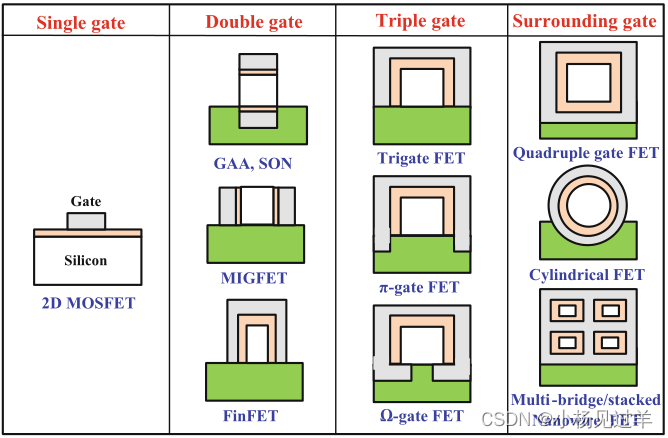

场效应晶体管的栅极结构演变

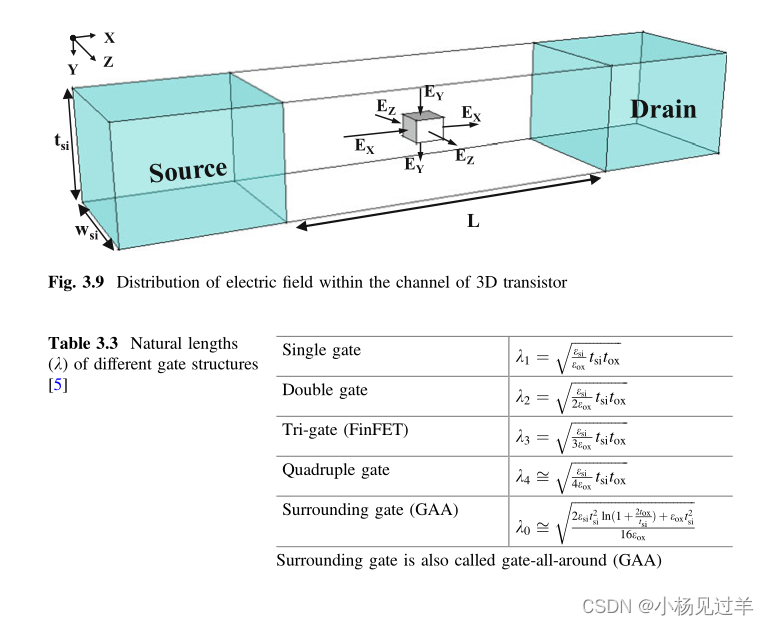

不同栅长结构的自然长度(lamda)

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?