DIBL vs. 源漏穿通 vs.

DIBL效应,是漏端引入的势垒降低(DIBL,Drain Induced Barrier Lowering)效应,指的是是小尺寸场效应晶体管(FET)中所出现的一种不良现象。

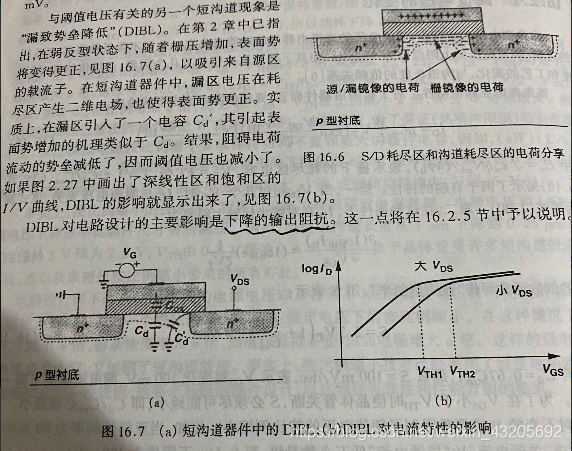

这是小尺寸场效应晶体管(FET)中所出现的一种不良现象,即是当沟道长度减小、电压Vds增加、使得漏结与源结的耗尽层靠近时,沟道中的电力线可以从漏区穿越到源区,并导致源极端势垒高度降低,从而源区注入到沟道的电子数量增加,结果漏极电流增加。沟道长度越短,DIBL效应就越严重。

实际上,DIBL效应往往与沟道长度调制效应同时发生,因为这些效应都是小尺寸场效应晶体管中容易出现的问题。

这种效应的影响主要有三个方面:

a)使场效应晶体管的阈值电压降低,影响到器件的整个性能;

b)使输出伏安特性曲线不饱和,即导致输出交流电阻降低、器件的电压增益下降。(DIBL的这种作用与沟道长度调制效应的一样,都将导致小尺寸晶体管的电压增益下降。)

c)限制着小尺寸MOSFET 进一步缩小尺寸,实际上这往往也就是ULSI进一步提高集成度所受到的一种限制。

沟道穿通效应(Channel punchthrough effect )就是场效应晶体管的源结与漏结的耗尽区相连通的一种现象。这种效应是在小尺寸场效应晶体管中有可能发生的一种效应,因此也往往就是限制MOSFET尺寸缩小的一种重要的因素。这是VLSI中很值得重视的一个问题。

沟道穿通效应的影响:当沟道一穿通,就使源-漏间的势垒显著降低,则从源往沟道即注入大量载流子,并漂移通过源-漏间的空间电荷区、形成一股很大的电流;此电流的大小将受到空间电荷的限制,是所谓空间电荷限制电流(与源漏电压的平方成正比,与沟道长度的立方成反比)。这种空间电荷限制电流是与栅压控制的沟道电流相并联的,因此沟道穿通将使得通过器件的总电流大大增加;并且在沟道穿通情况下, 即使栅电压低于阈值电压,源-漏间也会有电流通过。

DIBL vs. 源漏穿通两者一般都发生在短沟道器件中,只是发生的先后顺序不同,穿通(源漏之间bulk击穿)一定发生在DIBL之后,因此穿通可以看做是DIBL的终极情况,即漏端电位被拉低到源电位。

拉扎维P478

3126

3126

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?