题: 分析该时序逻辑电路 的功能, 写出电路的驱动方程、状态方程和输出方程, 画出电路的状态转换图和时序图.

分析:

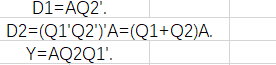

第一步, 根据电路逻辑图写出驱动方程和输出方程.

第二步, 根据驱动方程写出状态方程.

Q1*=D1=AQ2'.

Q2*=D2=(Q1+Q2)A.

第三步, 根据状态方程绘制状态表.

第四步, 根据状态表绘制状态图.

题: 分析该时序逻辑电路 的功能, 写出电路的驱动方程、状态方程和输出方程, 画出电路的状态转换图和时序图.

分析:

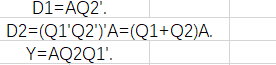

第一步, 根据电路逻辑图写出驱动方程和输出方程.

第二步, 根据驱动方程写出状态方程.

Q1*=D1=AQ2'.

Q2*=D2=(Q1+Q2)A.

第三步, 根据状态方程绘制状态表.

第四步, 根据状态表绘制状态图.

1万+

1万+

713

713

7093

7093

2348

2348

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?