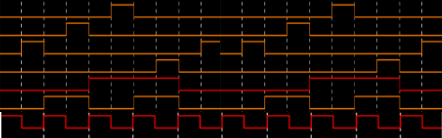

(15分)8. 请用D触发器和必要的门电路, 设计能产生上图示时序图波形的电路.

注: 上图中自上而下为P4、P3、P2、P1、Q1、Q0.

在真题中, 只给出了CLK、P4、P3、P2、P1的波形图, 这无疑增加了设计难度.

拿到时序图, 先自左到右观察各输出变量的取值情况, 发现在一次变化周期中, 只有一个输出变量为高电平, 其余都为低电平. 再仔细观察, 会发现每个输出引脚的脉冲宽度≠CLK脉冲的周期(这一点相当重要), 且只有当CLK为低电平时, 四个输出引脚才有可能为高电平.

再观察时序图, 我们可以得知, 电路共需要4个有效状态, 每个有效状态对应一种输出情况. 所以, 我们先设计一个同步四进制加法计数器.

| 同步四进制加法计数器状态表 | |||

| Q1 | Q0 | Q1* | Q0* |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 同步四进制加法计数器状态激励表 | |||

| Q1 | Q0 | D1 | D0 |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

由状态激励表, 得知 D1=Q1异或Q0, D0=Q0'.

再由上面的时序图, 得到四个输出变量P4、P3、P2、P1和电路状态以及CLK的关系.

| 输出设计真值表 | ||||||

| CLK | Q1 | Q0 | P1 | P2 | P3 | P4 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 |

由此, 我们可以得知 P1=Q1Q0CLK', P2=Q1'Q0'CLK', P3=Q1'Q0CLK', P4=Q1Q0'CLK'.

按照这里的结论进行接线, 得到电路的原理图.

本题能设计成功的关键在于①看到时序图后, 能明确先要设计同步四进制加法计数器, ②根据同步四进制加法计数器, 将四个有效状态分别分配给四个输出. 本题为二〇二〇考研真题(数字电路906), 为全网第一手(本人刚参加过研究生初试, 且专业课成绩十优秀)资料.

1585

1585

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?