概念

分频器的性能一般用四个参数来规定:(1)分频比,(2)最大允许输入频率fmax,(3)功耗,(4)最小允许输入电压摆幅(也叫“灵敏度”)。虽然分频器的相位噪声也很重要,但在大多数情况下它可以忽略不计。

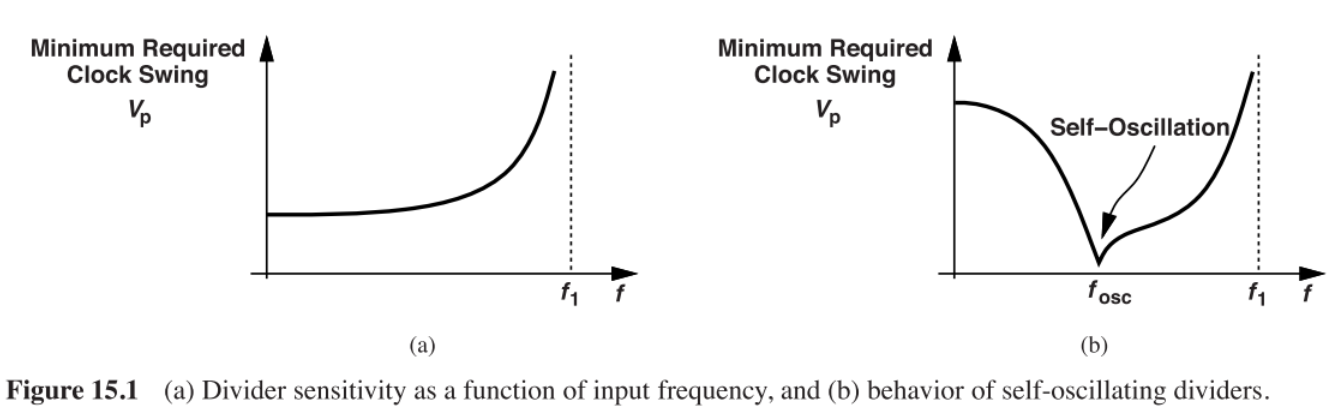

把一般分频器的输入灵敏度画成输入频率的函数。我们期望更高的频率需要更大的输入波动。其中灵敏度Vp是输入频率的函数。该图上的每个点代表一个fmax对应于某一输入摆幅。当f > f1时,无论摆幅有多大,电路都会失效。当输入为零时,一些分频环可以作为振荡器,表现出如右图的行为。在这种情况下,电路在fosc处振荡,输入幅度为零。

大多数分压器在轨对轨输入波动时运行,如果这些波动下降超过10%,就会接近故障。在某些情况下,即使频率远低于f1,也会发生故障。必须区分两种类型的故障,“静态”或“动态”。前者即使在低频时也会发生,表明电压波动不足、跨导或直流电压增益不足。后者是由阶段的有限延迟引起的。因此,在高速下发生故障的分频器必须首先在较低频率下进行测试,以确保适当的静态条件。例如,针对输入频率为10ghz的分频器首先在几GHz测试以检查其静态行为。如果输入边缘不够锐利,分频器也可能在非常低的频率下失效。此外,必须仔细设计压控振荡器和分压器之间的接口。

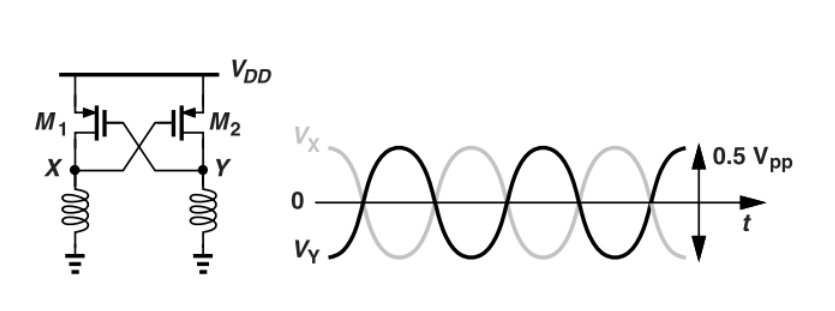

假设LC振荡器的振荡摆幅只有0.5Vpp(为了降低闪烁噪声),如何驱动需要轨对轨摆动的分频器?

VX和VY在半个周期内低于零。也就是说,即使他们的波动高达1vpp,也不能直接驱动分频器(幅度为-VDD/2-VDD/2,需要将波动改成0-VDD才能驱动分频器)。

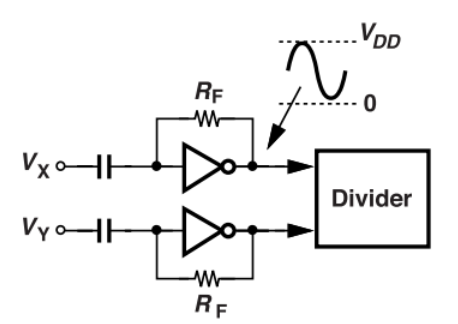

可以在VCO和分压器之间插入电容耦合、自偏置逆变器。由于其电压增益,逆变器提供轨道到轨道的摆动。耦合电容的选择大约是逆变器输入电容的5到10倍,反馈电阻必须远大于逆变器的输出电阻此外,该网络的高通角频率必须选择远低于最小输入频率。

当频率较大时,自偏置逆变器的小信号输入电阻近似等于1/(gmN + gmP)。这个电阻在一定程度上降低了振荡器Q。

该电路一个问题是电源噪声:该噪声会调制逆变器的延迟,从而在振荡器信号中增加相位噪声。出于这个原因,逆变器(和VCO)通常由片上低噪声稳压器(例如LDO)提供。

锁存器类型

感兴趣的是最大速度、功耗和时钟晶体管数量(以及输入端呈现的负载)等参数。

静态

D锁存器

一些分频器必须在低频可靠地工作。对于低于100 MHz的操作,我们更喜欢静态锁存器,因为它们不容易由于晶体管的亚阈值和结漏而发生故障。至于上限,静态锁存器在当今的CMOS技术中可以达到5到10 GHz的速度。

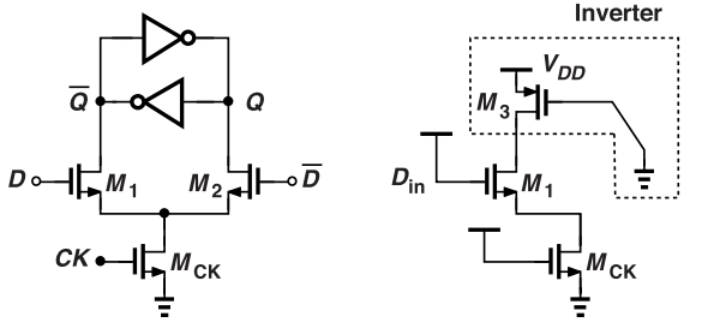

当CK高时,Din被传输,当CK低时,它的值被存储。单端拓扑结构由8个晶体管组成,每个时钟相位各有2个晶体管。注意,当电路从感测模式切换到锁存模式时,时钟转换时间必须足够短,以最小化Din和DF之间的冲突。

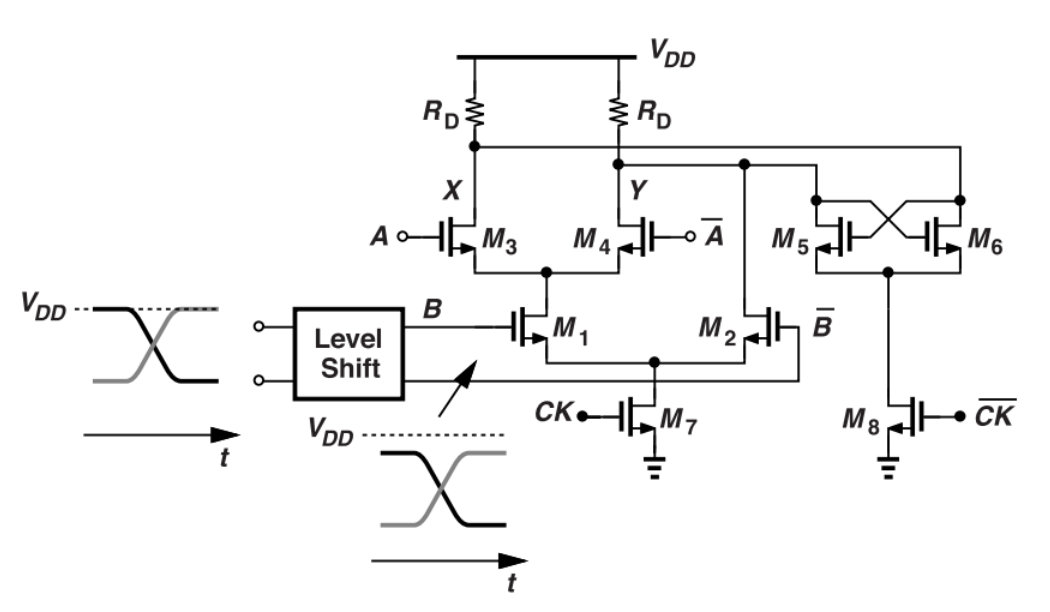

互补输入D锁存器

具有互补数据输入和输出的D锁存器。CK变高时,M1或M2导通,覆盖之前由两个逆变器保持的状态。当CK变低时,新状态无限期保留。采用七个晶体管,只有一个时钟器件,这种拓扑结构往往比上一个锁存器的更有效。然而,设计需要适当的器件比例。如右图,为了使输入数据覆盖之前的状态,MCK和M1(或M2)的串联组合必须足够强,以克服其中一个逆变器的PMOS晶体管。即使在SF角的过程中也必须满足这个条件。因此,我们选择M1,2和MCK至少与PMOS器件一样宽。

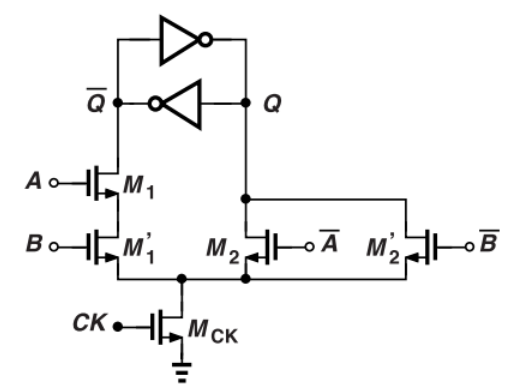

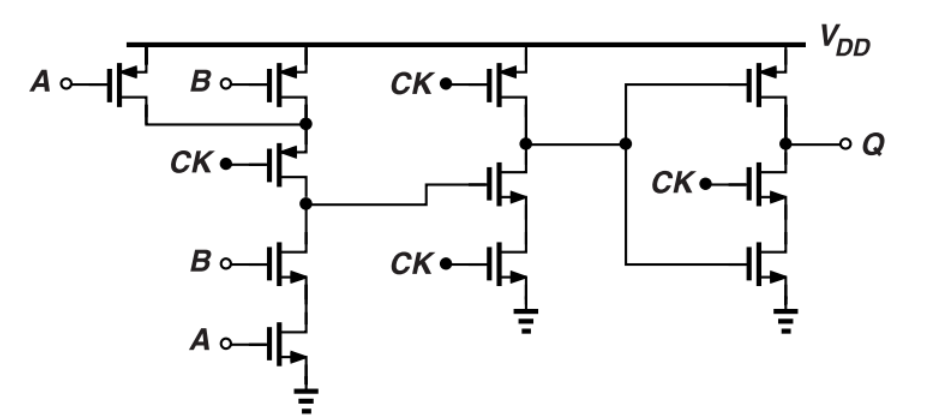

实现“与”功能的锁存器

在一侧插入一个NMOS NAND分支,在另一侧插入一个NMOS NOR分支。请注意,与分支使左侧更弱,除非它包含更宽的晶体管。

上面的拓扑中,状态通过两个背靠背的逆变器或背靠背的“逆变放大器”来存储。这是静态锁存器的一个特征:当时钟器件失活时,该状态由通往地或VDD的低阻抗路径保持。

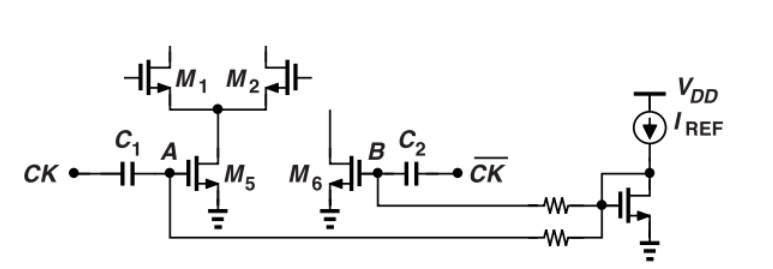

CML

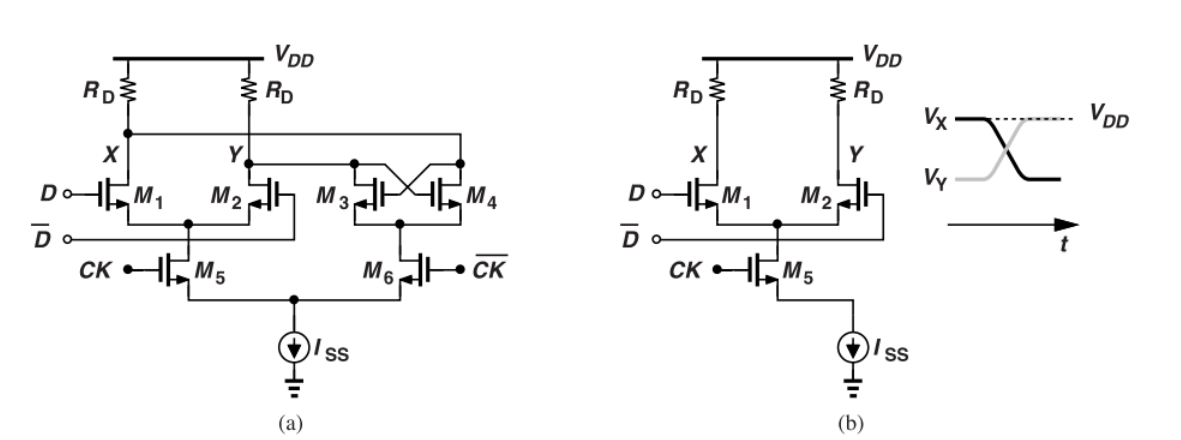

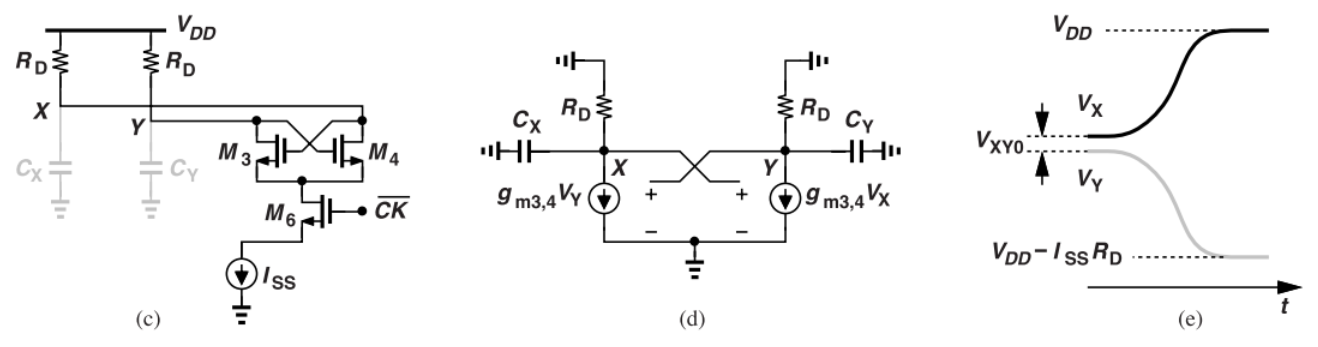

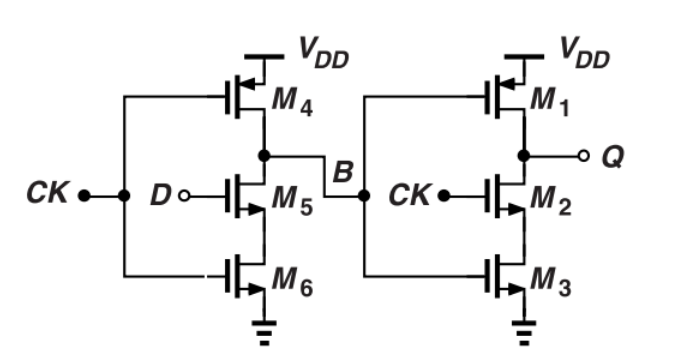

第三个静态锁存器结合了电流转向和非轨对轨输入和输出摆动。这种结构被称为“电流模式逻辑”(CML)拓扑,它吸收静态功率,仅在非常高的频率下使用。在感测模式下,CK高,M5导通,M6关断,电路简化为图(b)。因此,输入被M1和M2放大,并在节点X和Y上留下印象。接下来,CK变低,M5关断,M6导通,再生对M3-M4继承、放大并存储差分电压VX−VY[图(c)]。将这一对及其负载电阻视为两个背靠背反相(共源)放大器。如果晶体管完全开关,则单端电压摆幅=RDISS。

CML电路的速度优势源于两个特性:(a)使用适度的电压波动,例如ISSRD≈300-400 mV,因此转换可以更快地发生;(b)在数据和时钟路径中仅使用NMOS器件。然而,静态功率损失限制了它们的使用,只有在其他宽带分频器拓扑失败的情况下。

τreg = RDCD/(gm3,4RD−1)为再生时间常数。指数增长是由正反馈引起的,更根本的是由电路在右半平面的极点引起的。如图(e)所示,VXY遵循下式,直到电路进入大信号状态,一个晶体管的跨导下降,尾电流完全转向一侧。只有当τreg > 0,即当gm3,4RD > 1时,指数放大才会发生。

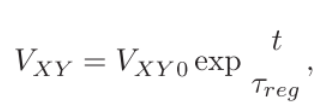

单端电压摆幅IDRD通常选择在300至400 mV左右。然而,M1-M2和M3-M4对叠加在M5-M6对之上,使得CML锁存器无法低压工作。作为补救措施,我们移除尾部电流源,并通过电流反射镜布置使时钟晶体管偏置。偏置电流由IREF定义,耦合电容器将M5和M6的栅极偏置与CK共模电平隔离开来。电阻器和电容值足够大,可以产生远低于时钟频率的高通角频率。

可以选择C1和C2的值为M5和M6栅极处电容的5到10倍,以便尽量减少时钟波动的衰减。但是,如果时钟摆动是轨道到轨道的,我们可以允许一些衰减,例如,对达到A和B的振幅进行2或3倍的衰减,因为M5和M6可以以适度的摆动工作。事实上,避免A和B的轨对轨振荡是可取的,这样M5和M6就可以在饱和状态下工作,而电路对M1和M2保持一定的共模抑制。为了理解这一点,假设VA上升到VDD,从而驱动M5进入深三极管区域。然后,流过M1和M2的电流对其栅极处的CM电平有很强的依赖性。在这种情况下,电路(通过数据路径)的CM增益可能超过1,在锁存器级联中引起显著的CM误差。

由于其有限的输入波动,CML锁存器不能轻易地使用NAND门。互补输入D锁存器所示的NAND原理在这里失败了,因为只有适度的输入波动才能关闭M1和M±1。下图显示了一个包含适当NAND操作的CML锁存器,其中只有当A和B在感测模式下都高时,VX才会低。该电路需要对B输入进行直流电平移,以确保M1和M2不进入三极管区域。这种结构在低压设计中很少使用。

CML锁存器可以包含OR门,如图所示,其中M1和M1'可以在X处施加低电平,在Y处施加高电平。在这种情况下,M2简单地由恒定偏置电压Vb驱动,该恒定偏置电压=A和B的共模电平。输入的单端特性使得该电路的鲁棒性比全差分CML拓扑略低,需要密切关注输入。具体而言,A和B电压摆动以及M1和M1'的宽度必须足够大,以确保尾电流的完全转向。此外,如图右图所示,R1和I1以生成Vb以跟踪A和B的CM水平。例如,如果前级的平均尾电流为ISS,负载电阻为RD,则其输出CM电平等于VDD−RDISS/2,要R1I1=RDISS/2。

CML电路消耗静态功率,只有当所需的速度太高以至于其他拓扑无法满足时才应使用。在本节研究的三个静态锁存器中,前两个不消耗静态功率但速度有限,而CML拓扑可以在非常高的频率下运行并消耗高功率。另一方面,动态锁存器通常比前两种拓扑运行得更快。

动态

在动态锁存器中,状态存储在器件电容上,而不是通过背靠背的放大级。这种锁存器比静态锁存器包含更少的晶体管,并且通常提供更有利的速度-功率权衡。但是,由于器件泄漏,如果时钟频率不够高,它们可能会失去其状态。也就是说,动态锁存器对工作频率施加了一个下限。

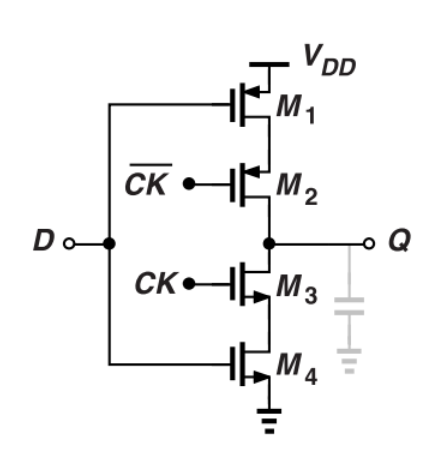

Clocked CMOS

时钟CMOS”(c2mos)动态锁存器。当CK高时,

该电路充当逆变器,感应输入。当CK变低时,P和N支路被禁用,状态存储在输出电容上。与前一节研究的静态结构相比,这一阶段只需要四个晶体管,没有正常工作所需的电流率。

使用构建二分频器,这个分压器能跑多快?对于给定的输入频率fin,我们要求环路支持频率为fin/2的波形。如果粗略地将电路视为三个逆变器,是一个环形振荡器,可以估计最大输出频率约为1/(6TD),其中TD表示各级的平均延迟。我们认为电路的自振荡频率为1/(6TD)。此时,fin≈2/(6TD) = 1/(3TD),(逆变器内的时钟晶体管增加了它们的延迟)。我们甚至可以说这个电路是一个对输入时钟“注入锁定”的三级环形振荡器。注意,这个÷2电路不提供正交输出。

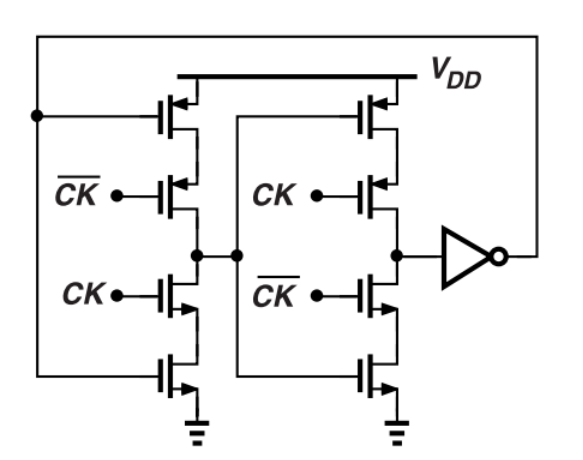

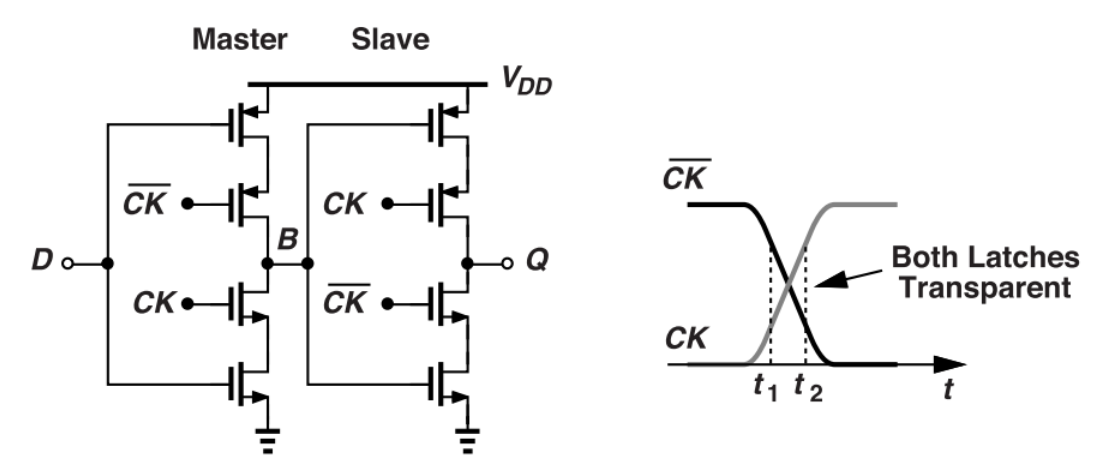

c2mos锁存器的主要缺点是它们在时钟转换期间的“透明性”。为了理解这一点,考虑图中具有真实时钟波形的主从FF。当CK上升到将从机置于存储模式而将主机置于感知模式时,这两个阶段在一段时间内变得透明。因此,D可以改变B,从而改变Q。存储在Q处的寄生电容上,如果D的新值与Q不一致,则由于这种“馈通”,输出状态会大幅降低。作为保守措施,两个锁存器应该由不重叠的时钟相位驱动:即两个不重叠的时钟及其互补。但对于分频器实现,快速时钟转换就足够了。

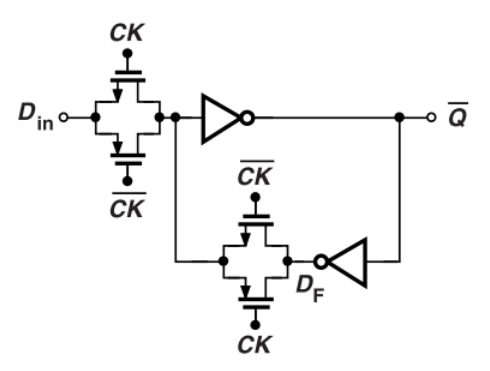

True单相时钟

避免使用互补时钟,真单相时钟电路比c2mos表现出更高的速度和更低的功耗。

含非与门

不想写了。。。。。。

3620

3620

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?