目录

差动对与反相器优劣

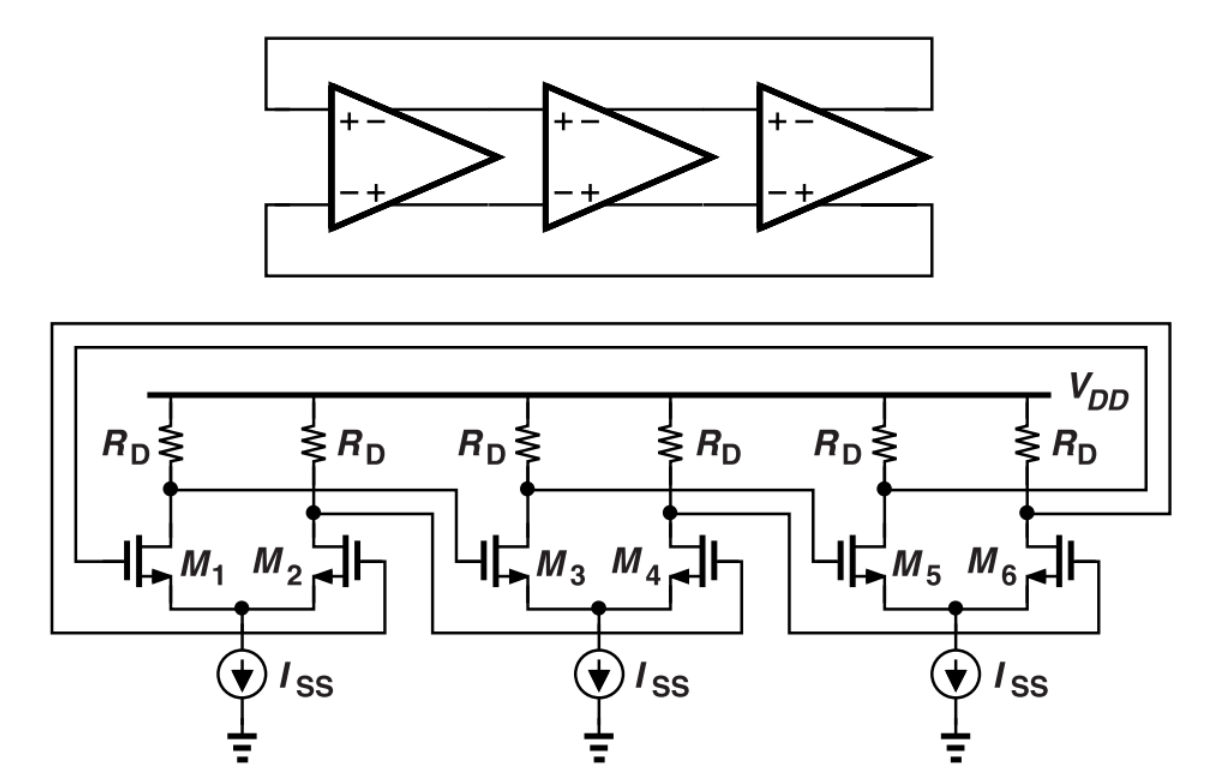

使用差动环可以大大减轻电源噪声,三级拓扑每一级提供60◦的相移,低频电压增益为2。电源灵敏度比单端环小得多。

例题:当上面的电流没有尾电流时,电路如何运转。

答:没有尾电流时,电路可以看成两个独立的单端环振,每个环振以自己的频率和初始相位运行。

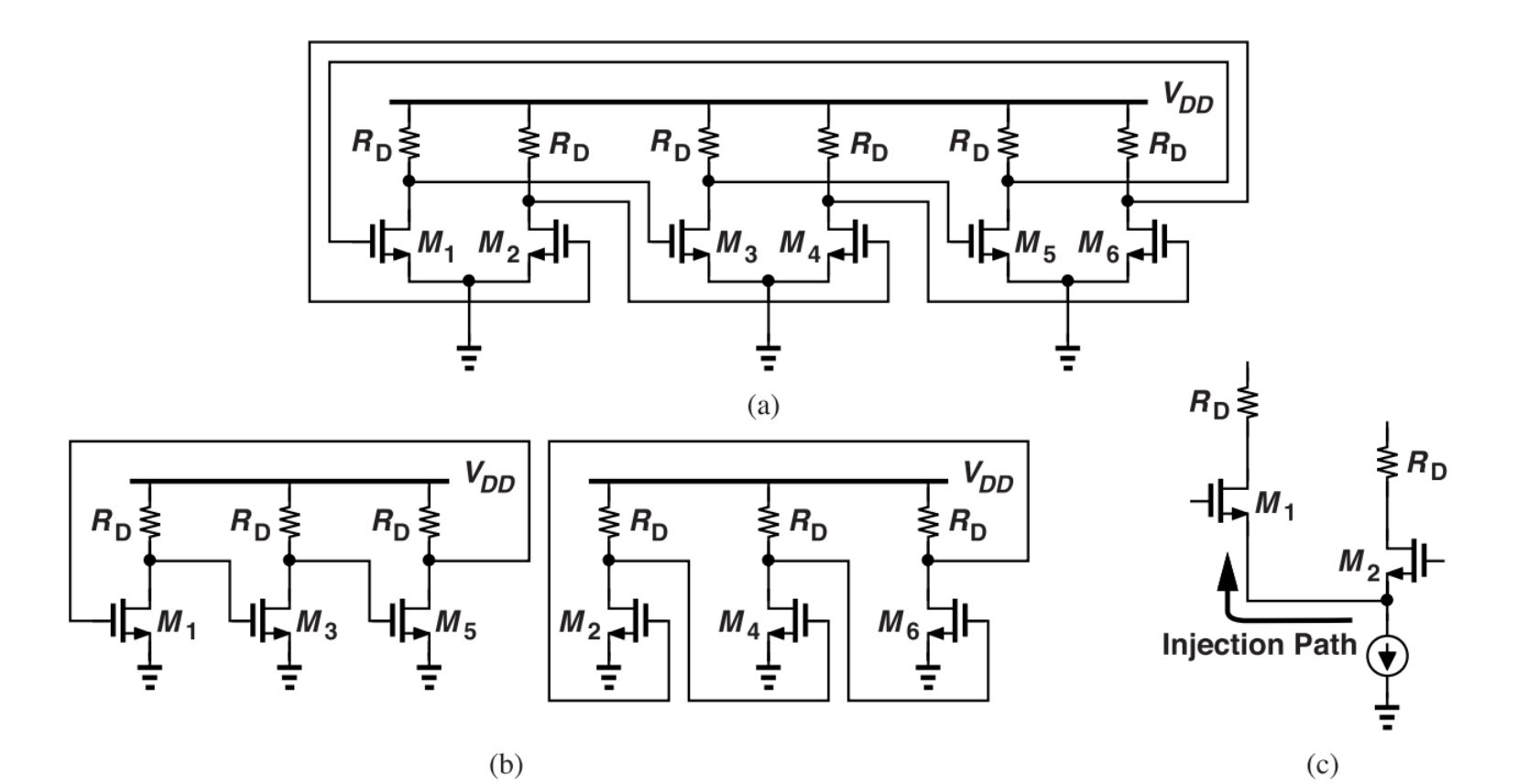

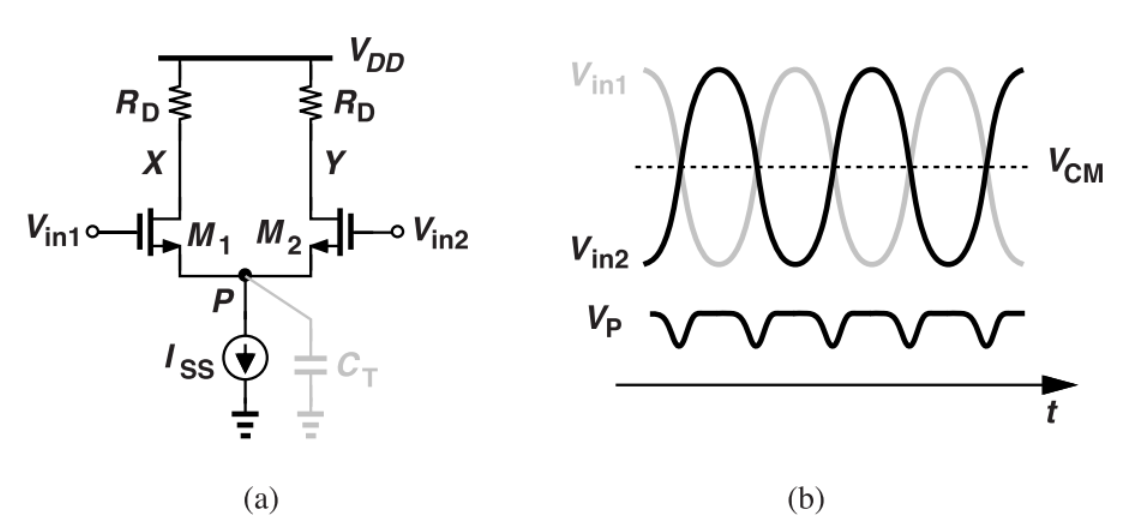

带尾电流的差动对环振可以看成两个单端环振,通过输入对管的源极互相注入锁定。如图,M1充当源极跟随器,M2充当共栅极,一个环振可以向另一个环振注入电流。为了使两个单端环路相互同步并以不同的方式运行,注入必须有足够的“强度”,因此需要一个高阻抗的尾部装置。(如果用小电阻代替尾电流源,则一个振荡器的注入大部分会分流到地。)

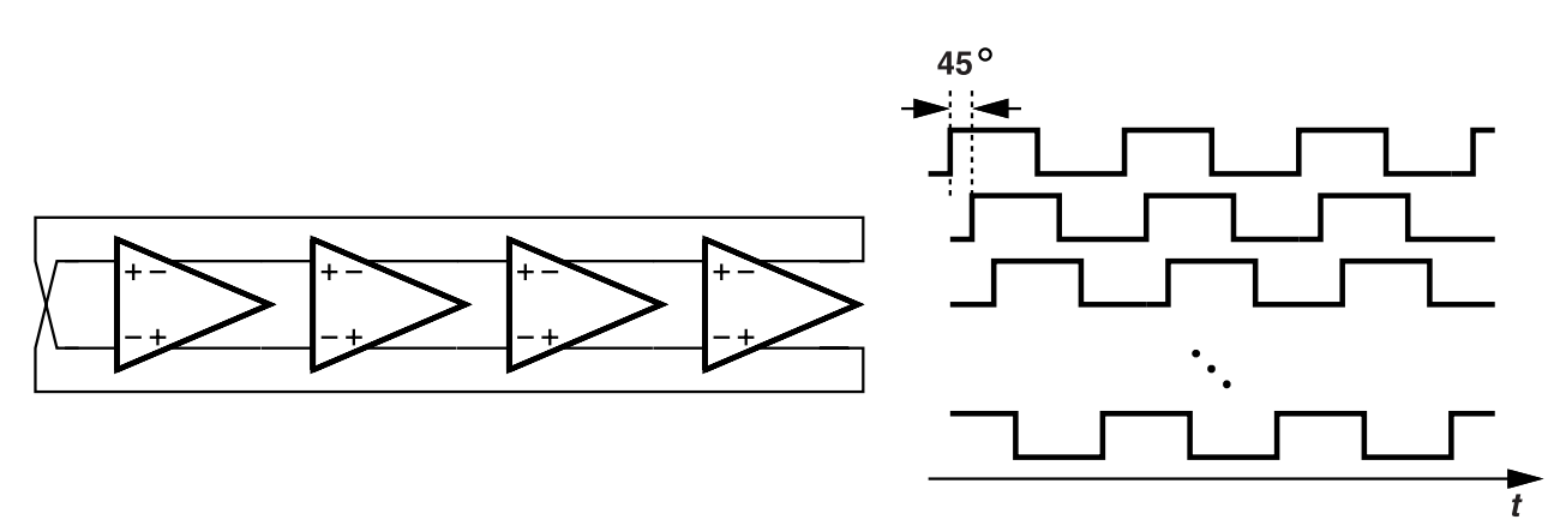

差动环相对于其单端的第二个优点是,它们可以轻松地产生多个所需的输出相位。例如,四级环路产生8相45◦分离。

差分拓扑的第三个优点是速度更快。每级延迟比反相器的延迟要小,有两个原因:(1)单端电压摆幅ISSRD更小,例如在300 mV左右,需要更少的过渡时间;(2)与反相器中的PMOS相比,差动对的电阻负载对输入和输出没有贡献电容。

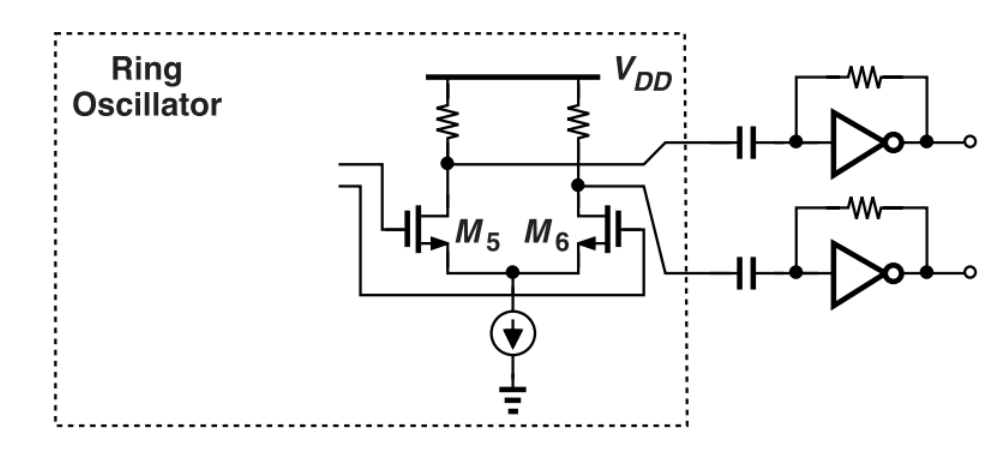

缺点:不提供轨道到轨道的电压波动,因此需要电平转换器(放大器)。常见的方法是使用电容式感应输出的自偏置反相器,代价是更大的功耗。

相位噪声

热噪声

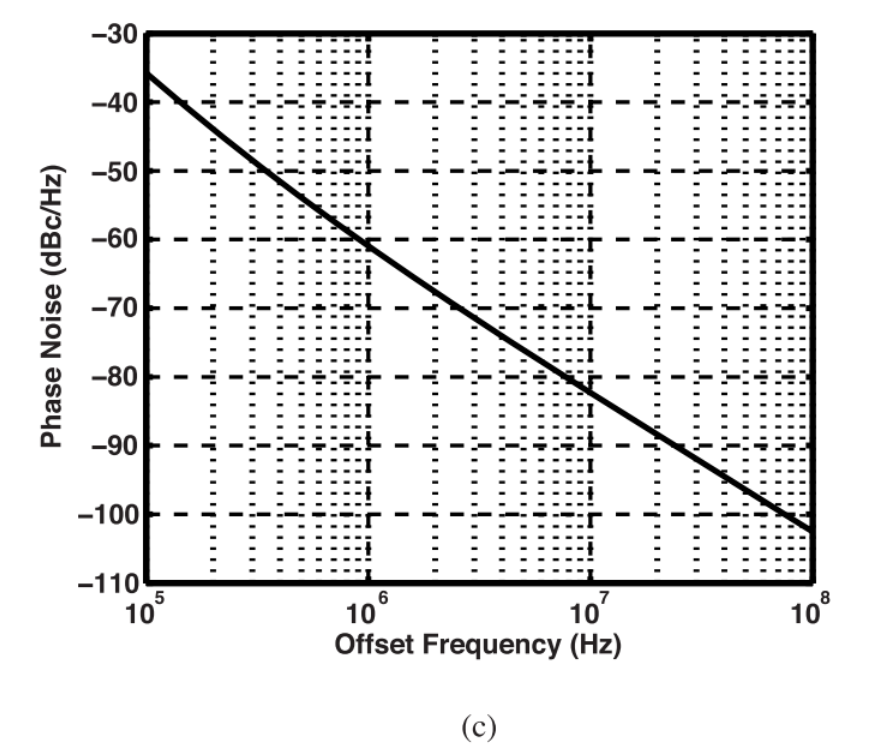

差动环振荡器的主要缺点是相位噪声较高。热噪声:

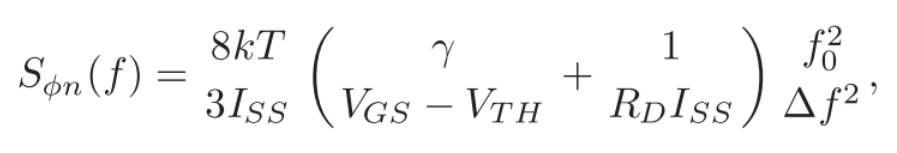

启动时,gmRD必须≥2。将gm写成2ID/(VGS−VT H) = ISS/(VGS−VT H),得到下式,这两项表示晶体管和负载电阻对Sφn的相对贡献。

如果N增加时,相噪如何?为了公平比较,保持功耗、电压波动和振荡频率随N的增加而恒定。按比例减少ISS和W/L,增加RD。所有晶体管的电容都缩小了,而VGS−VT H和RDISS保持不变。因此,相位噪声按8kT/(3ISS)的比例上升。例如,如果N增加一倍,ISS减半,则Sφn增加3db。

闪烁噪声

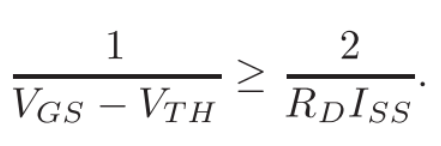

如果单端漏极电压波形没有对称的上升和下降转换,差分对晶体管的闪烁噪声会导致相位噪声。这种情况可以看作是上升边和下降边的斜率不等,特别是在交叉点。

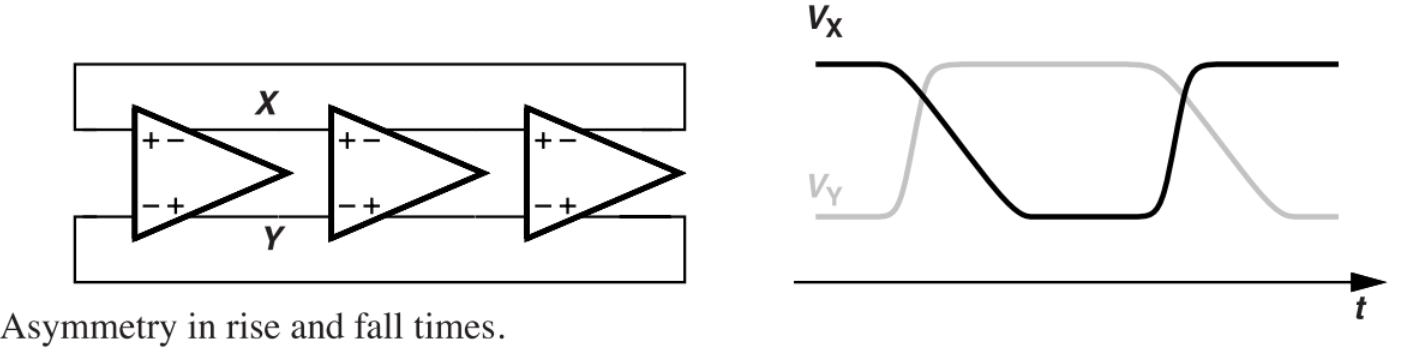

VX和VY中二次谐波的存在导致不相等的斜率。假设VX (t) = V1 sinω0t + V2 sin(2ω0t) + VCM。二次谐波加速了上升沿,减慢了下降沿。VCM周围的斜率在V1ω0 + 2V2ω0和- V1ω0 + 2V2ω0之间交替。使用第一次和第二次谐波幅值的比值来衡量波形的不对称性。

二次谐波的来源:VP在Vin1和Vin2的交叉点附近下降,频率为2ω0。(每次Vin1达到最大值时,M2关闭,M1作为源跟随器,提升VP。因此,VP每循环提升两次。)

初始环振设计

设计一个三级差动环振荡器,尾电流、负载电阻和晶体管尺寸的选择取决于以下要求:(1)每一级的小信号低频电压增益必须至少为2,以保证起振;(2)电压摆幅必须足够大,以降低相位噪声。目标是单端峰对峰摆幅约为300 mV;(3)期望差分对几乎完全控制其尾电流,以便在给定的ISS(因此对于给定的功耗)中最大限度地提高电压波动。

摆幅不可能达到ISSRD,峰间单端电压摆幅大致等于0.54RDISS。因为通过环路的延迟太短,不允许VX和VY到达VDD。

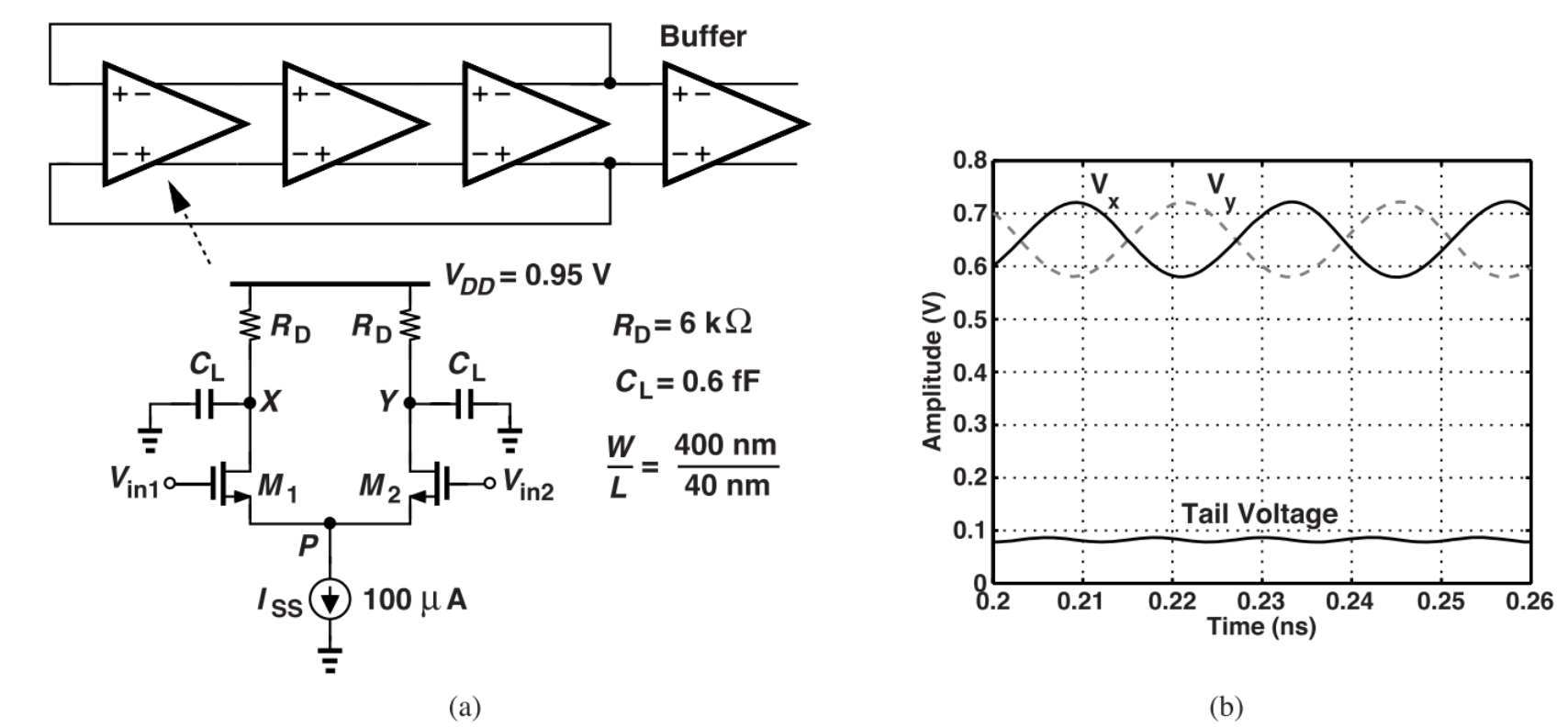

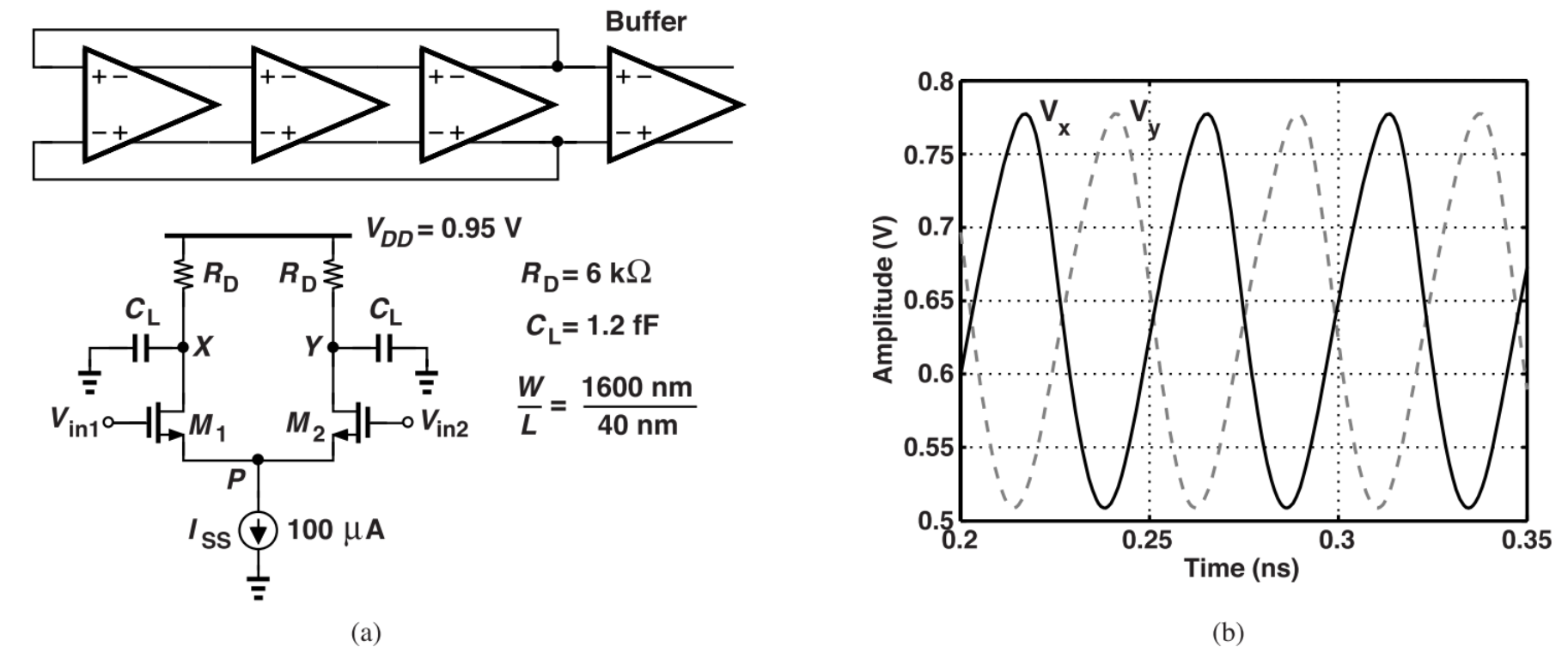

选择ISS = 100µA和RD = 6 kΩ,单端摆幅约为0.54ISSRD≈320 mV。W/L = 400 nm/40 nm以满足起振条件gmRD≥2。考虑极端工艺角,在75°C和VDD = 0.95 V时设计电路。估计互连电容为0.6fF, 使用理想的尾电流源。

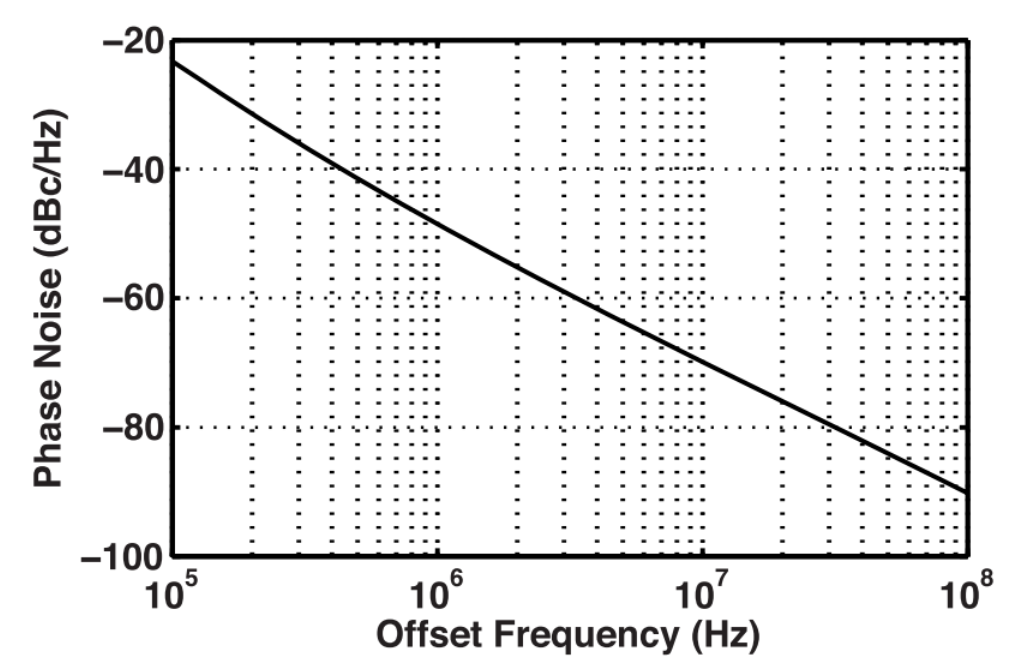

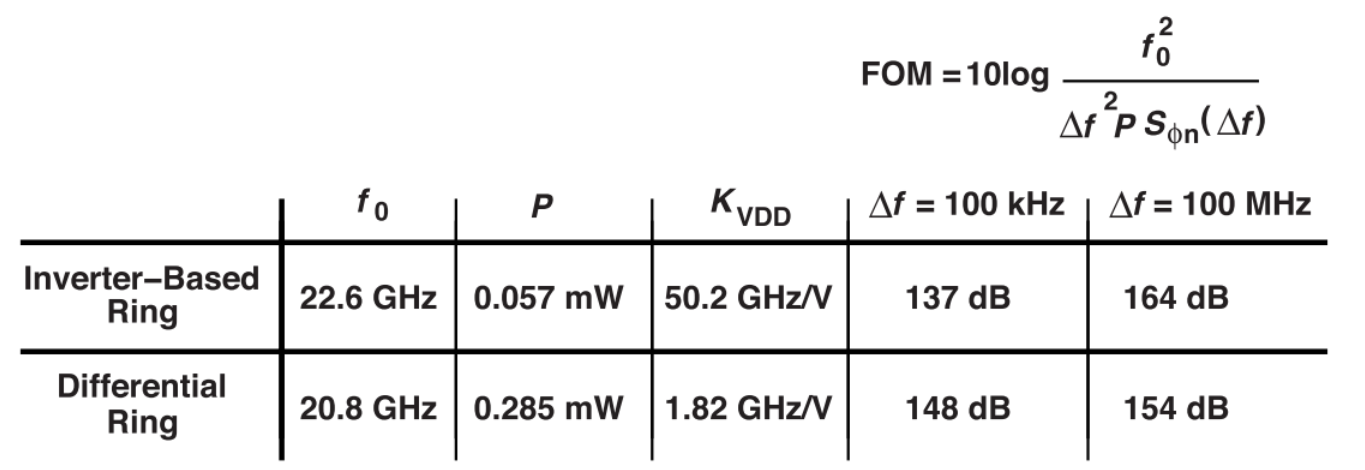

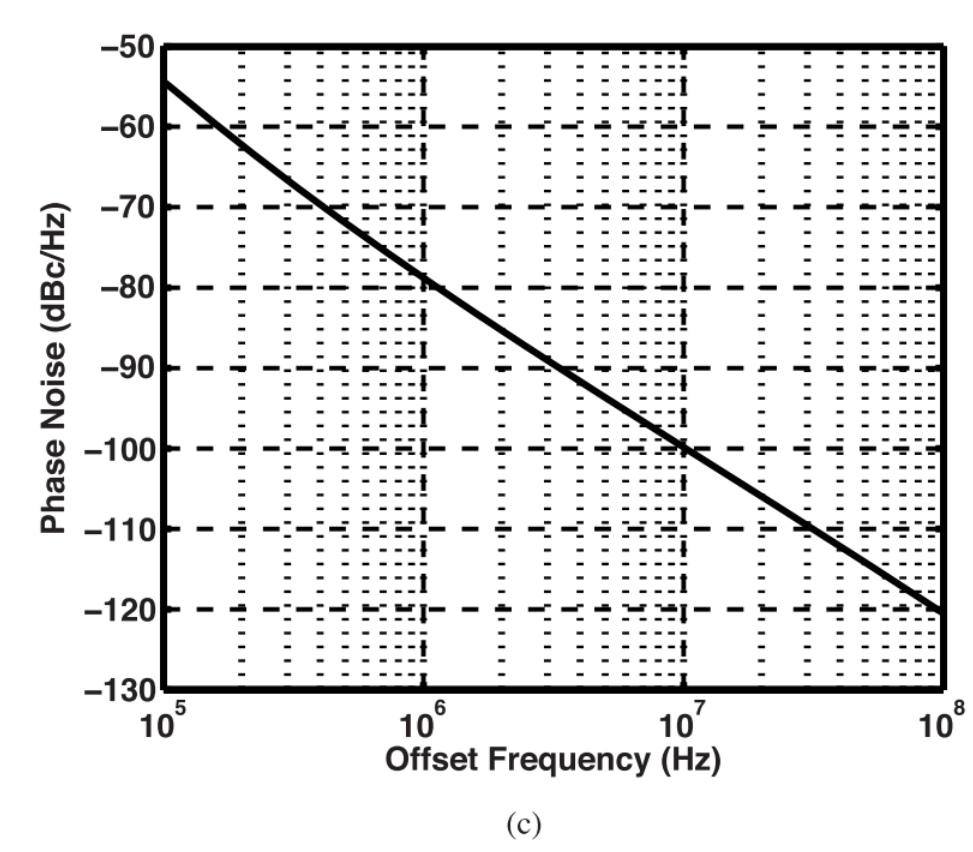

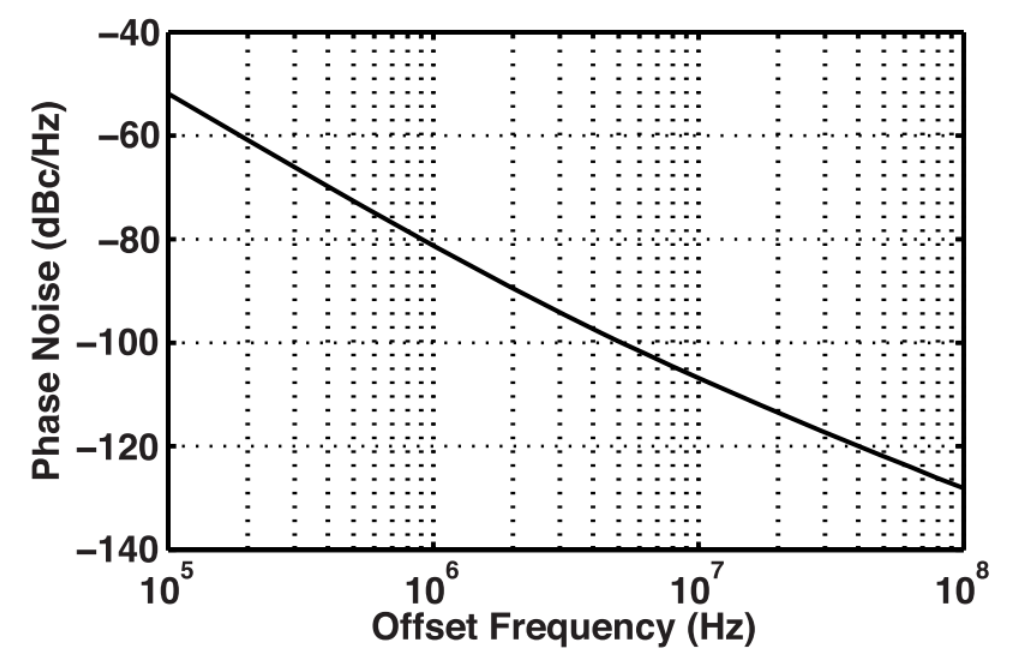

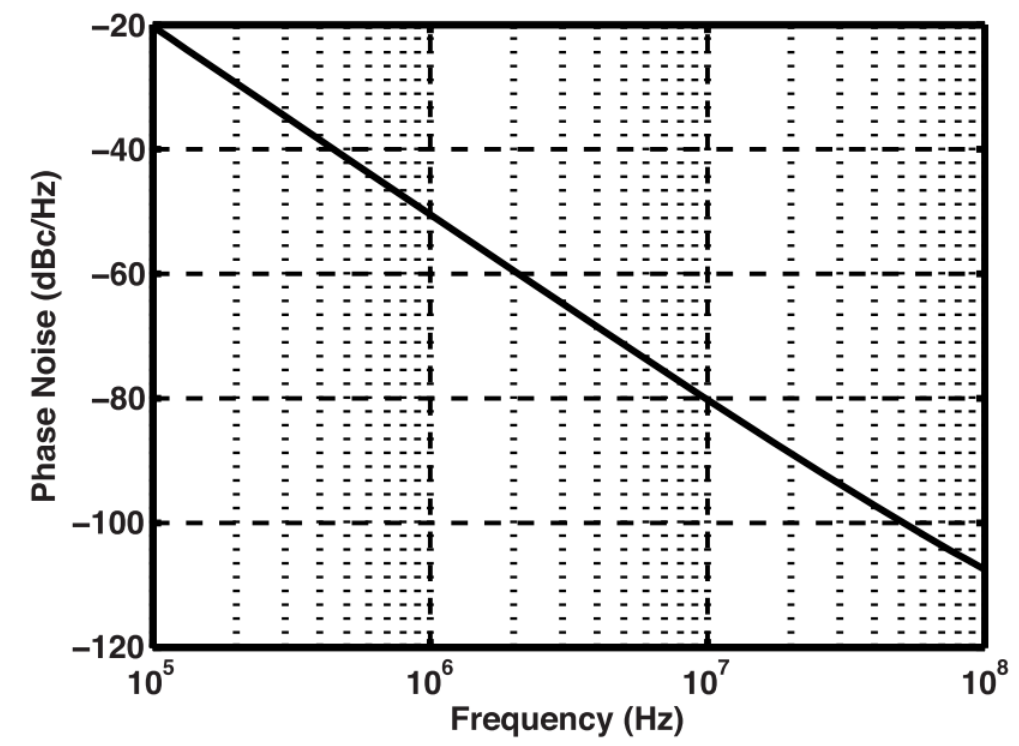

100 MHz处闪烁噪声上转换。f0 = 42 GHz, Sφn(100 MHz) =−90 dBc/Hz, P = 3×100µA ×0.95 V = 285µW。相噪比基于反相器的环振的初始设计要差很多。基于反相器的环形振荡器,功耗,相噪,频率折中-CSDN博客

改进设计

将晶体管的宽度加倍(W/L = 800 nm/40 nm),为尾电流源提供更大的电压净空,单端漏极电压波动增加到250 mVpp.漏端电流从17.5µA到87µA,电路振荡频率为31.3 GHz。尾部节点电压摆幅已上升到约35 mVpp。

100-MHz偏移的相位噪声将下降8dB。

再次加倍晶体管宽度(W/L = 1600 nm/40 nm)

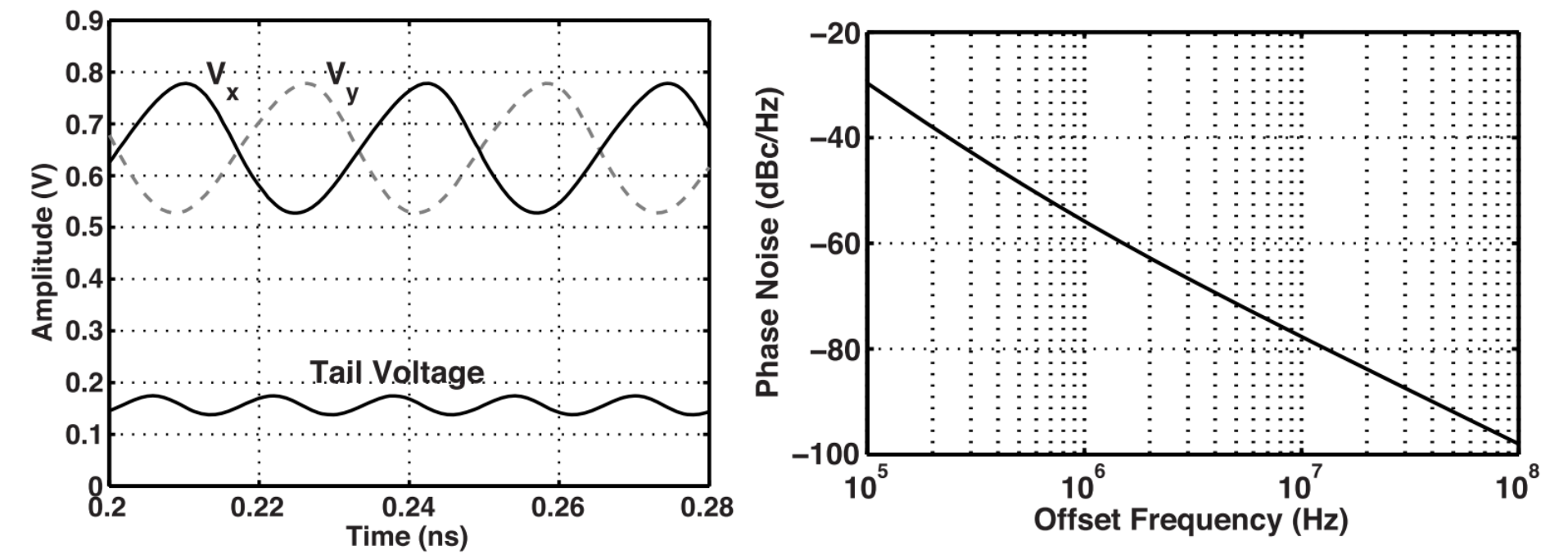

环振荡频率为20.8 GHz,单端摆幅为270 mVpp。上升和下降时间分别约等于21 ps和28 ps。

电源灵敏度约为1.82 GHz/V,比基于22.6 GHz反相器的设计低28倍。

基于反相器的环振和基于差分对的环振对比

降低振荡频率

上面的VCO工作在20.8 GHz,高于目标2 GHz。为了达到期望的频率,有3个选择:

1. 为每个节点增加电容。

2. 增加阶段的数量。

3. 增加晶体管的长度。宽度也应增加,以确保尾电流源有足够的电压净空。

更大的节点电容

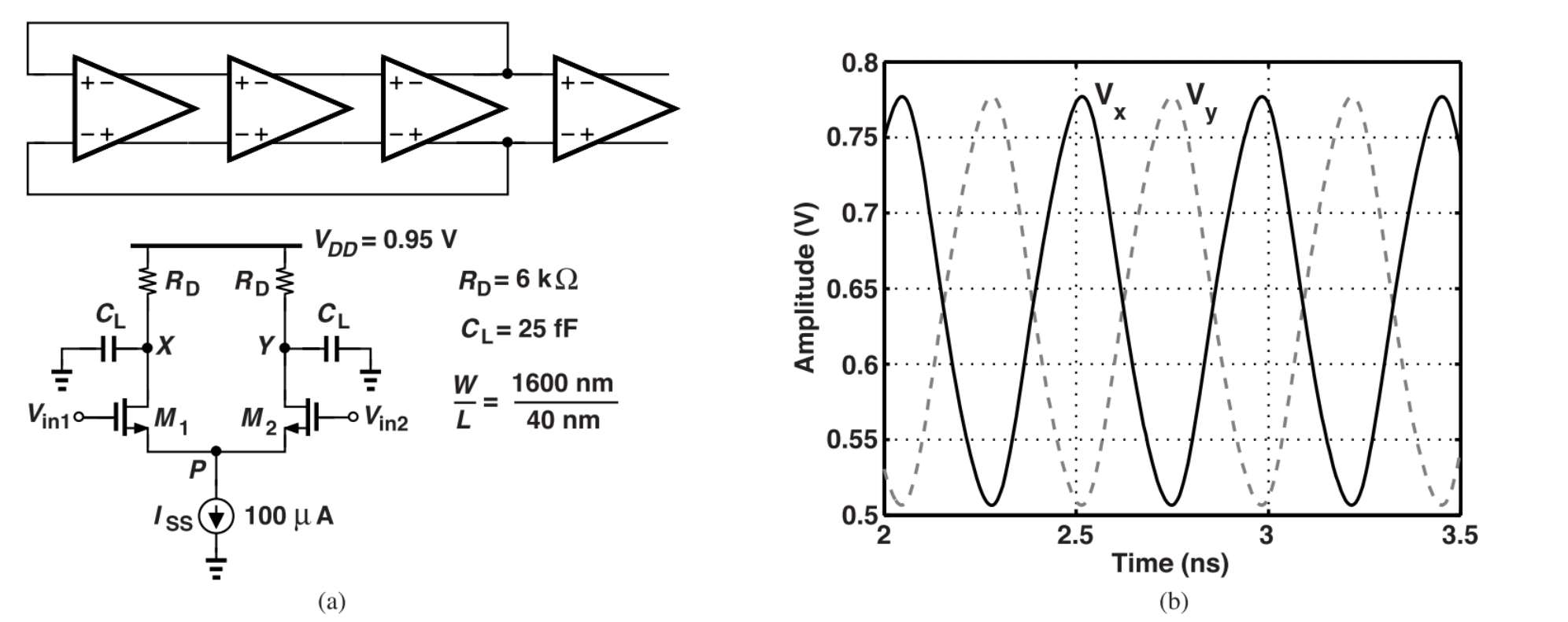

初始设计中,RD = 6 kΩ和f0 = 20.8 GHz条件下,可以从f0 =√3/(2πRDCL)中估计出节点电容为2.21 fF。为了使f0降至2ghz,将CL提高约10倍。

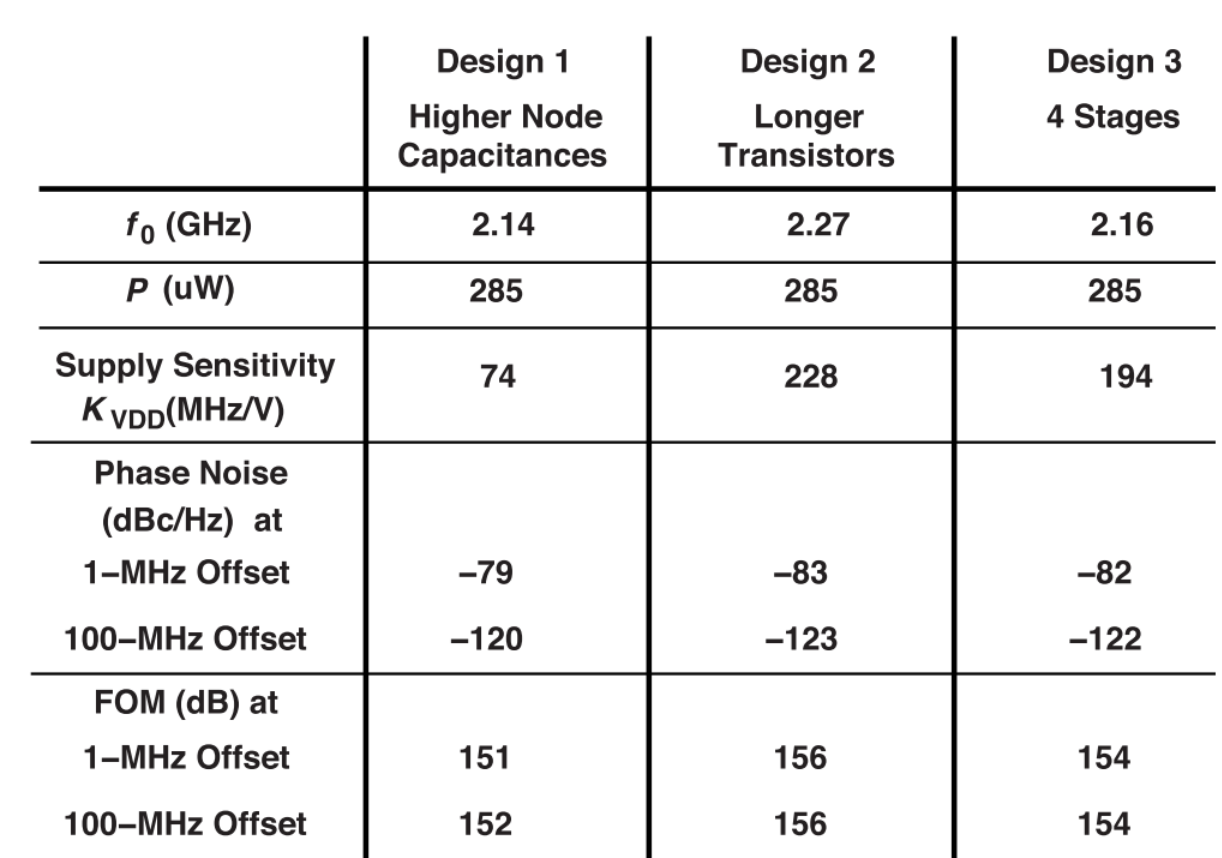

25fF的外部电容产生f0 = 2.14 GHz。对于热和闪烁噪声系统,实际下降约为18 dB。降低了电源灵敏度,KV DD = 74 MHz/V。

更大的级数

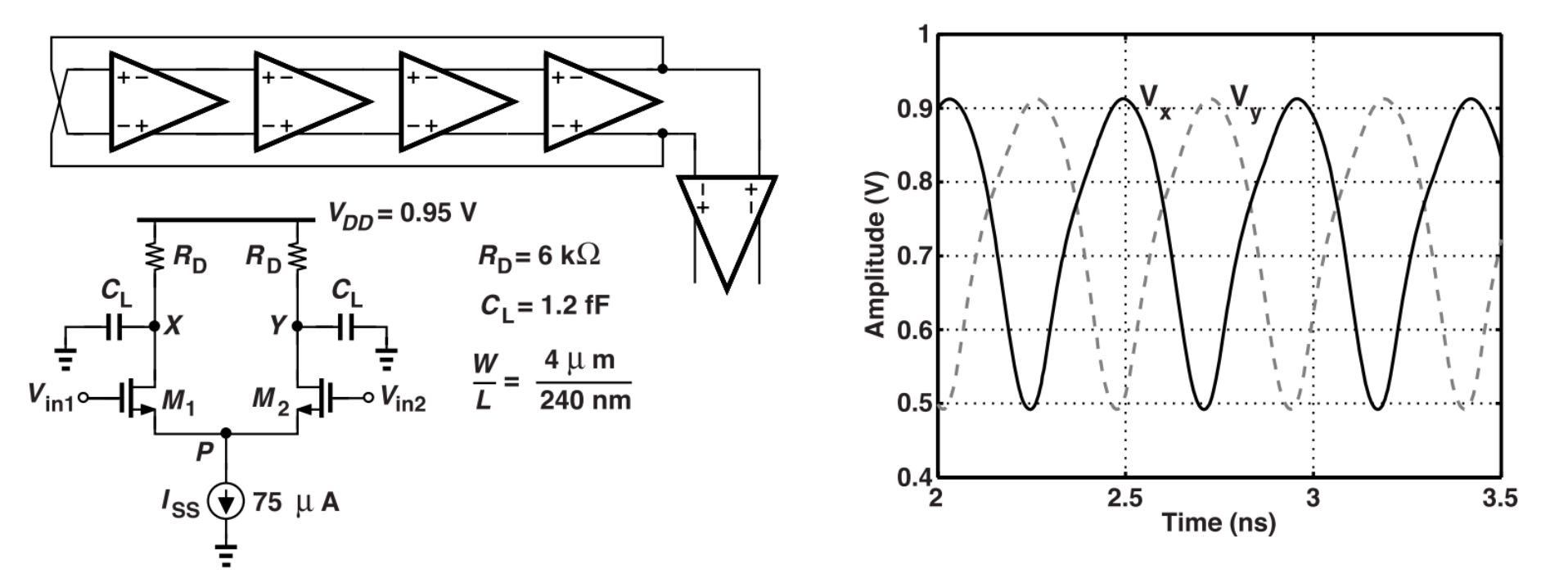

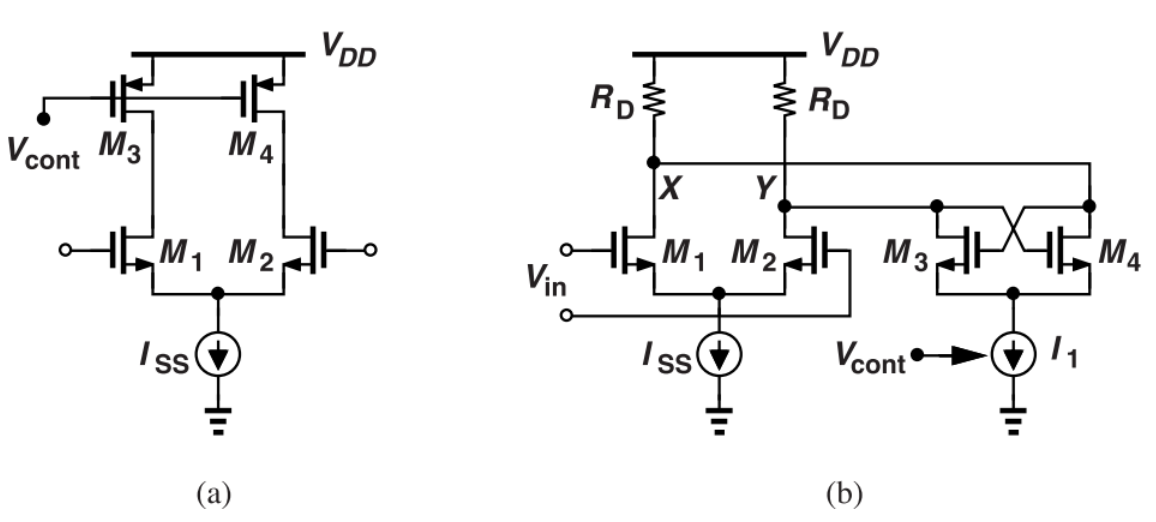

如果功耗恒定,较大的N转化为较高的相位噪声。当N从3到4再到5时,电压波动增加,降低归一化相位噪声。因此,仅将N提高适度,并通过使用更大的晶体管进一步缩放频率。四级回路,其中ISS降低到75µa, W/L = 4µm/240 nm。

摆动现在达到420 mV。f0 = 2.16 GHz处振荡,电源灵敏度为194 MHz/V

更长的晶体管长度

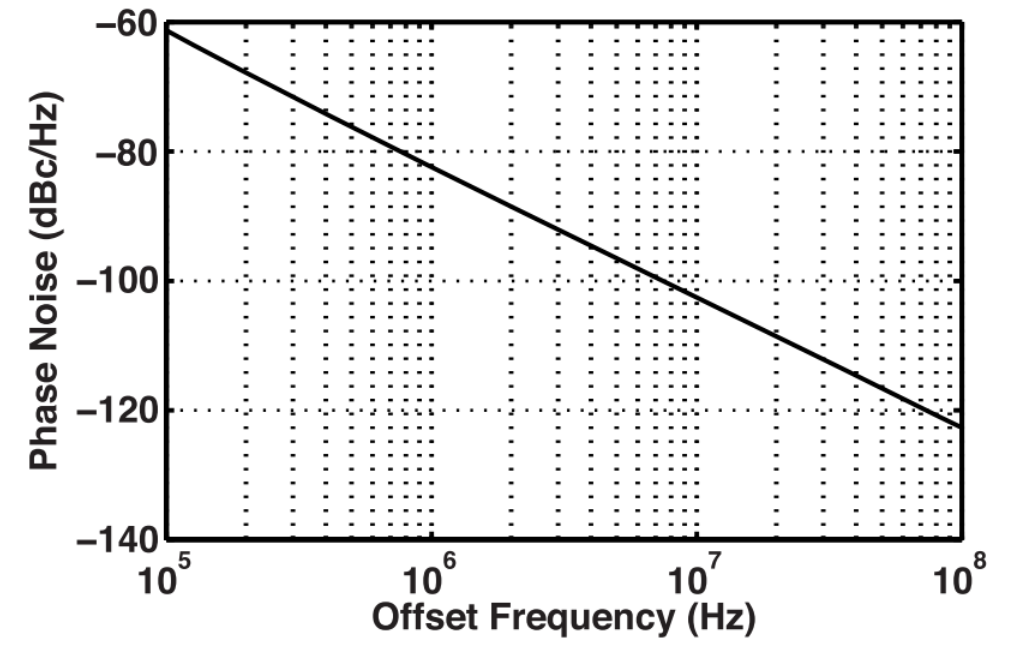

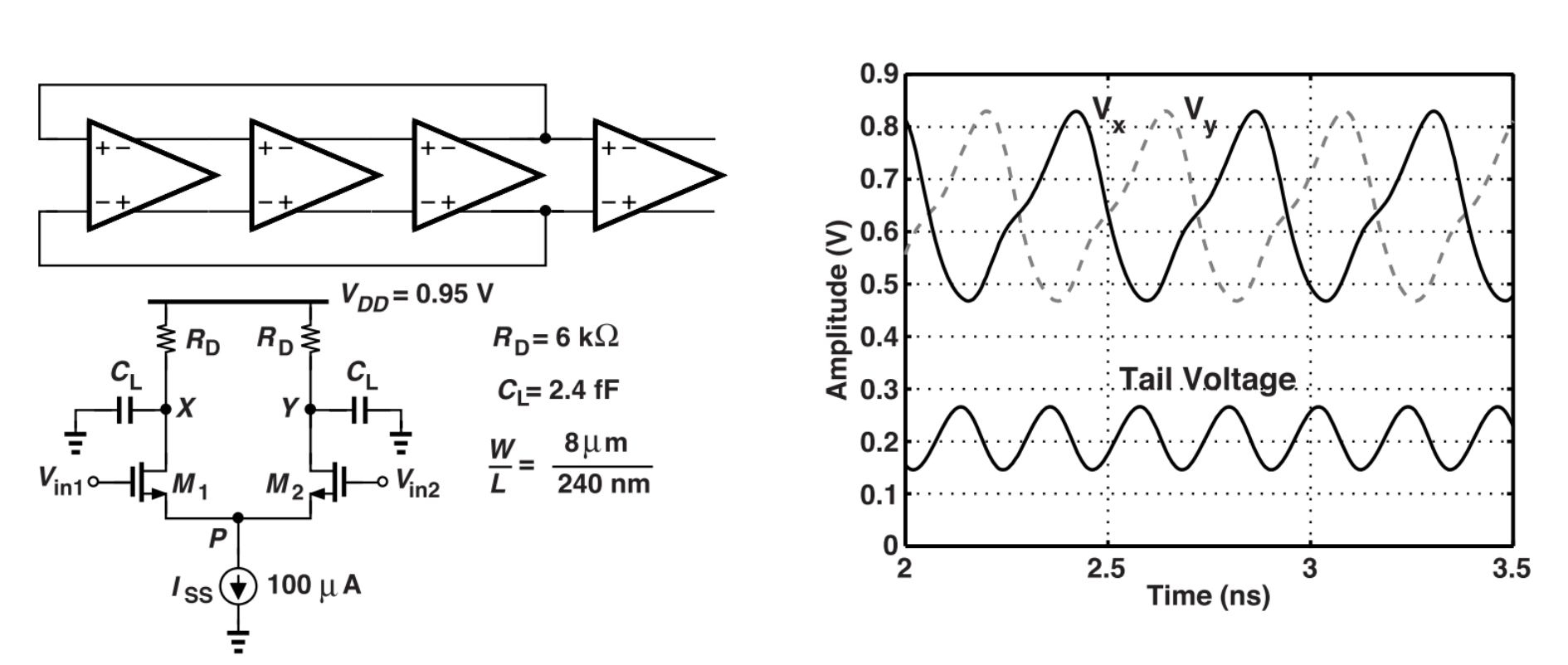

将晶体管的尺寸从W/L = 1600 nm/40 nm增加到8µm/240 nm,得到f0 = 2.27 GHz。

X和Y处的电压波动从参考设计中的270 mVpp增加到360 mVpp,接近0.54RDISS估计值。事实上,晶体管现在经历了完全的开关。其次,100-MHz偏移的相位噪声下降了21.5 dB,电源灵敏度约为228 MHz/V。

总结

采用大晶体管的三级环可以获得最佳的FOM。另一方面,四级环的优点是产生更大的电压波动和相位,是45度的整数倍。

Tuning Techniques

创建一个相对线性的连续调谐特性,随后添加离散调谐。对于N级环。小信号估计表明,振荡频率相对独立于尾电流,应该通过改变RD、CL或N来调谐。因此,设想了三种调谐技术。

电阻调谐

将差动对的负载电阻替换为PMOS在深三极管区域工作的控制电阻。但是,随着PMOS导通电阻的变化,电压摆幅也会发生变化。此外,如果M3和M4保持在三极管区域,则Vcont的上界远低于VDD−|VT HP |。这个问题转化为频率调谐中的大量非线性。

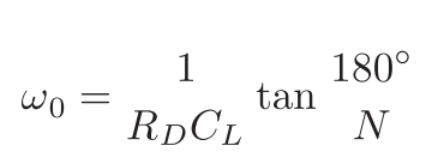

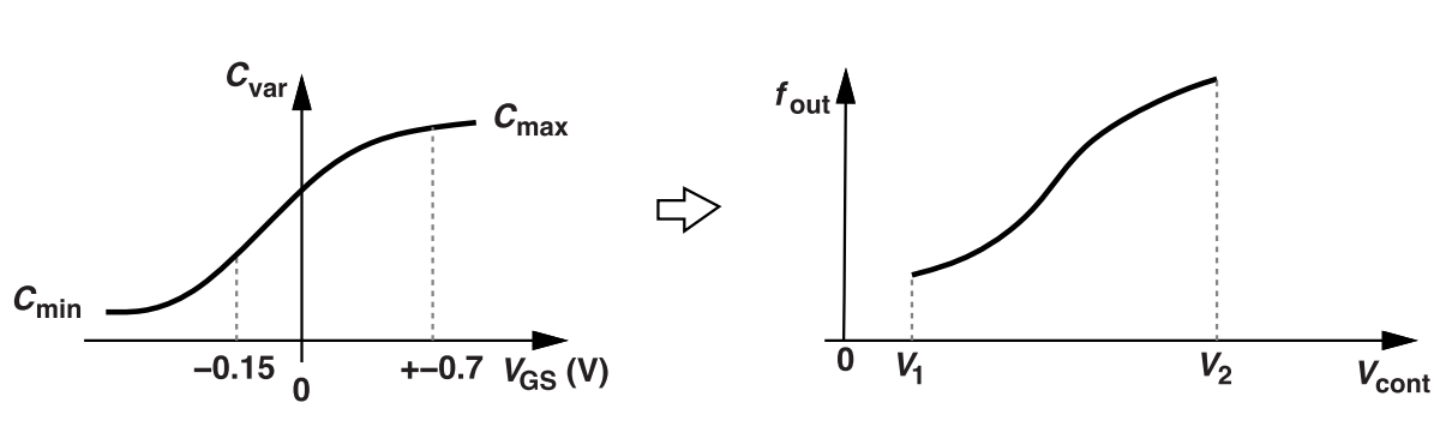

另一种调整负载电阻的方法是将可变负电阻与负载电阻并联。通过交叉耦合晶体管M3和M4在X和Y之间引入一个等于−2/gm3,4的电阻。如果连续调谐范围限制在f0的10-20%,那么调谐应该可以忽略相位噪声的降低。

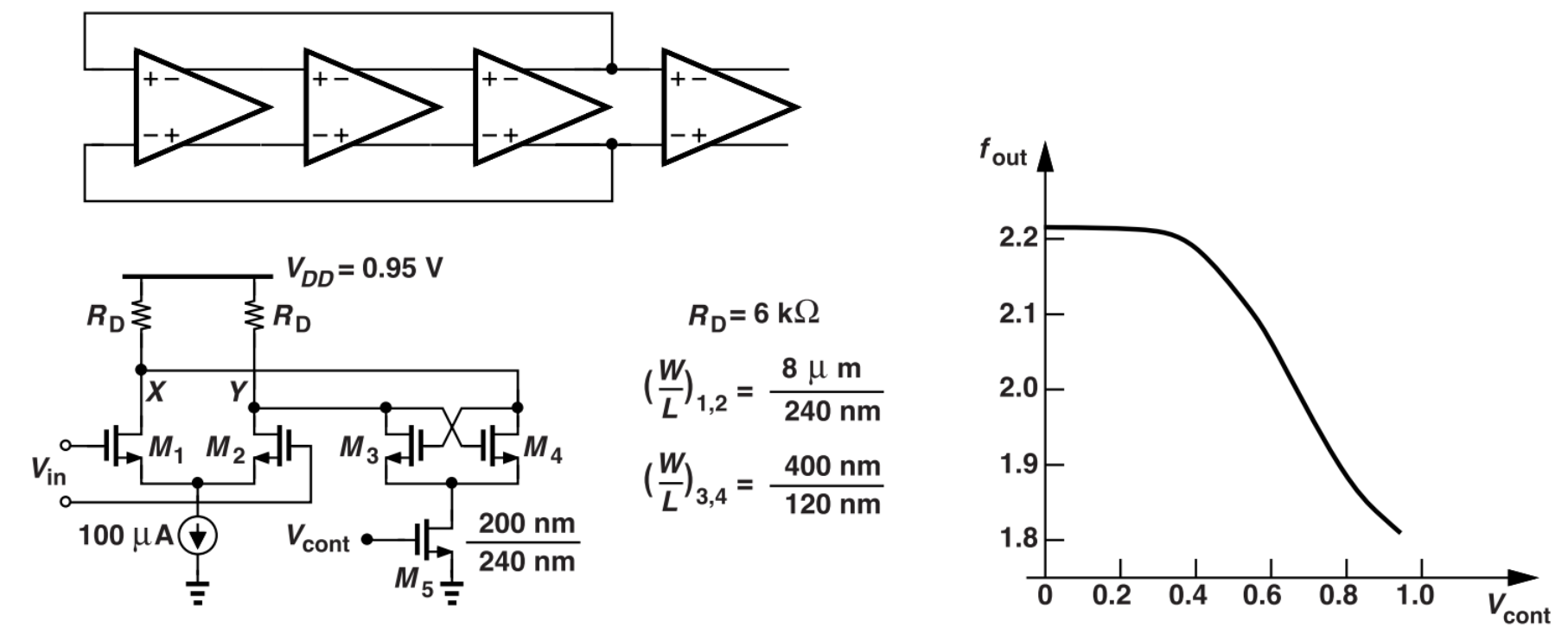

M3-M5的尺寸选择是为了提供必要的调谐范围,并避免降低相位噪声。当Vcont从250 mV(略低于VT H)上升到900 mV时,f0从2.2 GHz下降到1.83 GHz,电压波动从360 mV增加到480 mV。最大KV CO约为1ghz /V。不幸的是,如果M5必须保持饱和状态,则不能允许Vcont达到900 mV。

电源抑制随着M5进入三极管区域而降低。因为如果M5工作在三极管区域,则交叉耦合对的偏置电流成为VDD的函数,因为在VX = VY的瞬间,有VDS5 = VDD - VRD - VGS3,4。因此,VDD波动引起id3,4和gm3,4变化,调制负电阻和f0。

M5的闪烁噪声电压直接增加到Vcont。这是负电阻调谐的主要缺点。

Vcont = 0和Vcont≈400 mV之间的平坦区导致400 mV < Vcont < 900 mV的高KV CO。与基于反相器的环振不同,这种差分拓扑不适合结合PMOS和NMOS器件来去除平坦区

电阻负载差分环的一个重要优点是其pvt引起的频率变化小于基于反相器的环。ω0 = (RDCL)−1 tan(180◦/N)表明,振荡频率随RD和CL的变化而变化,与信号通路中晶体管的强度关系不大。RD的典型变化为±15%,CL的典型变化为±5%,对于窄带应用,总体调谐范围约为±20%。

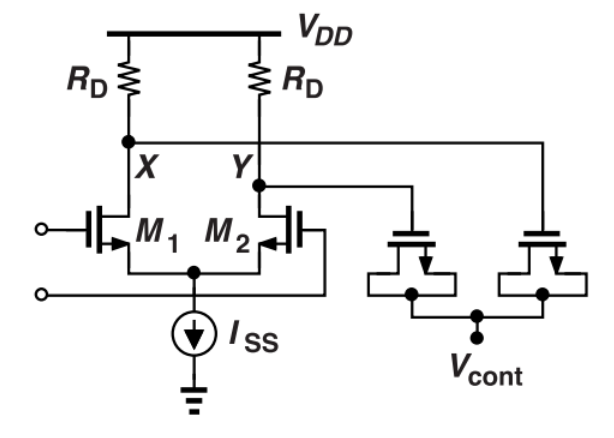

变容二极管调谐

通过调谐网络可以忽略不计地增加相位噪声,但它依赖于变容模型来建立所需的调谐范围。变容器调谐通常是优选的技术,因为它在控制路径中引入了可忽略不计的噪声。相比之下,路径中的任何晶体管都会注入闪烁噪声,从而调制振荡频率。

MOS电容,变容器的平均电压约等于X和Y处的共模电平减去Vcont。因此,当Vcont从V1到V2时,变容管的电压从VDD−ISSRD/2−V1变为VDD−ISSRD/2−V2。例如,如果V1 = 50 mV, V2 = 0.9 V, ISSRD/2 = 200mV, VDD = 0.95 V,则VGS的范围为-150 mV至+700 mV。如果Cvar在VGS接近+700 mV时没有明显变平,那么当Vcont降至V1时,Cvar也不会明显变平。

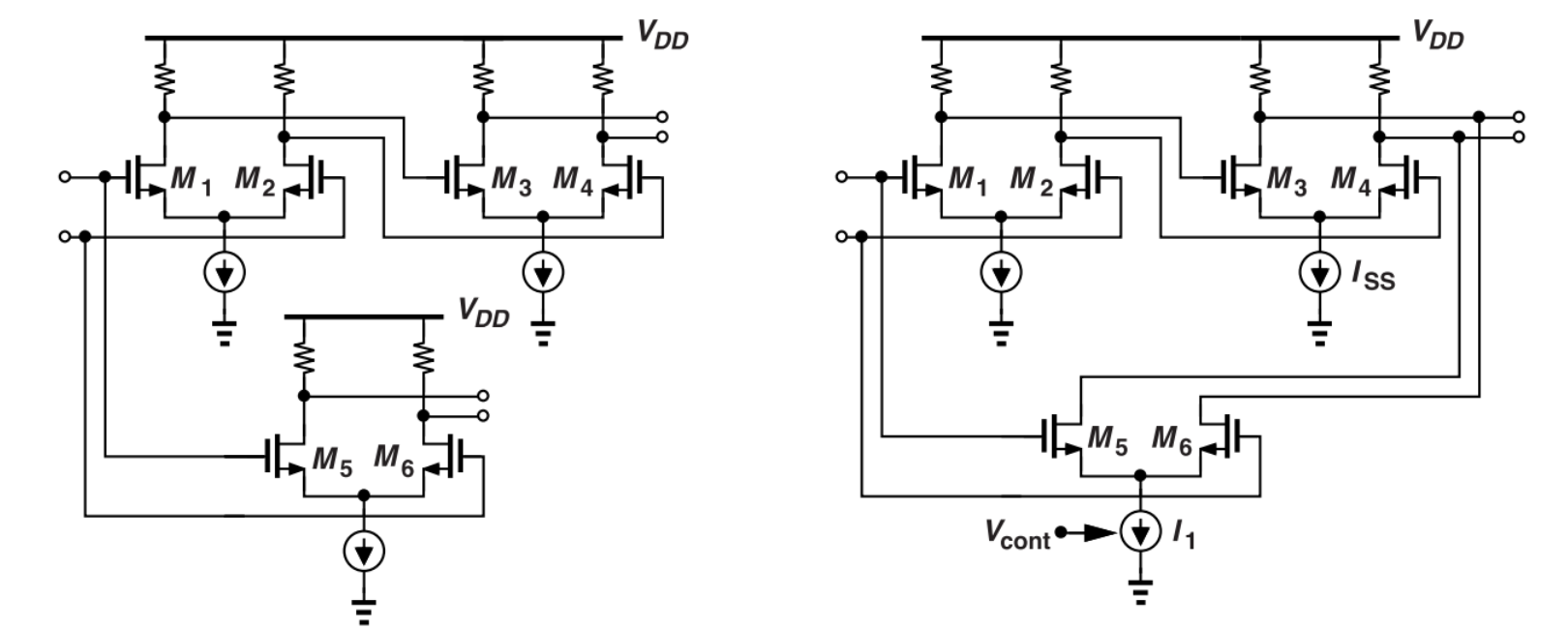

调整级数

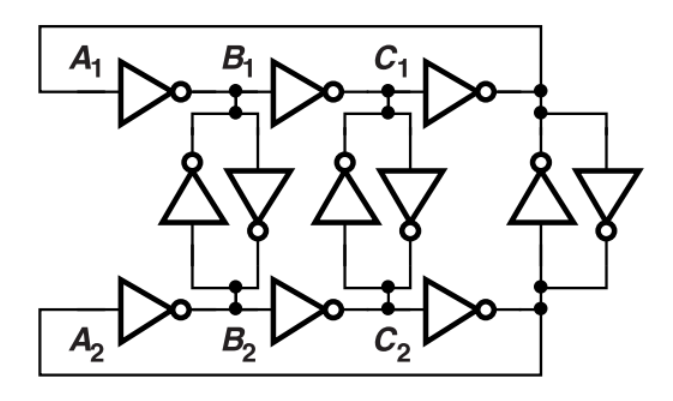

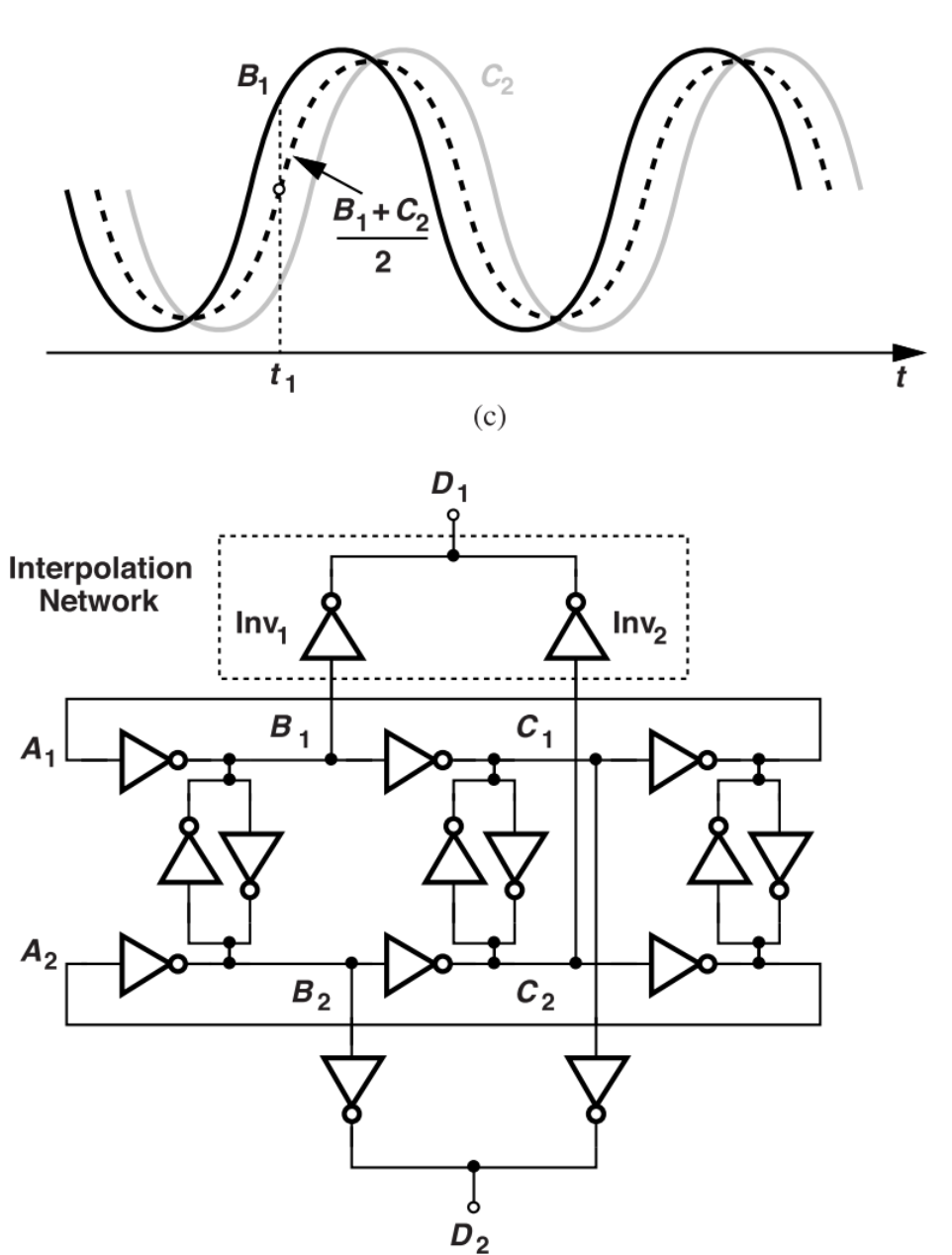

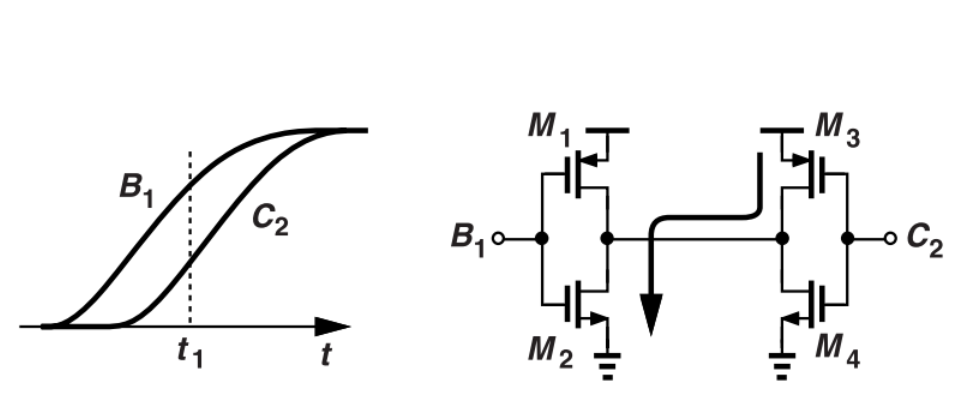

每个阶段包含一个慢路径和一个快速路径,它们的输出求和并应用到下一个阶段。快速路径的强度由Vcont调节。当快速路径关闭时,环达到最小振荡频率,因为环路中的阶段以最长的延迟运行。如果快速路径完全开启,信号在每个阶段大多绕过慢路径,产生最大的f0。对于这两者之间的Vcont值,电路在慢路径和快路径之间“插值”。把相应的波形分别称为慢信号和快信号。在这个例子中,我们看到环中的总级数从6到3不等。

注意到M3-M4和M5-M6的漏极电流分别与慢速和快速信号成正比,可以首先将这些电流求和,然后将结果通过电阻传递。如下面有图所示,Vcont调整了添加到慢速信号中的快信号的比例。输出电压的波动现在随I1变化,但变化幅度很小,因为我们对窄(连续)调谐范围感兴趣。

从低值到接近VDD的控制电压。对于这个Vcont的最大值,NMOS电流源位于三极管区域,加剧了电源的敏感性

上述振荡器通常存在高相位噪声。当快速通道关闭时,所需的振荡频率是用六个差分对(在一个三级环中)而不是用三个差分对获得的。

在总功耗保持不变的情况下,随着差分对数量的增加,相位噪声趋于上升。此外,当快速通道开启时,I1的噪声会调制频率。

总结

综上所述,在各种调谐技术中,我们更喜欢连续变容调谐和开关电容器进行粗控制。这种设计在调谐特性中受到的平坦区影响更小。

具有正交输出的反相器振荡器

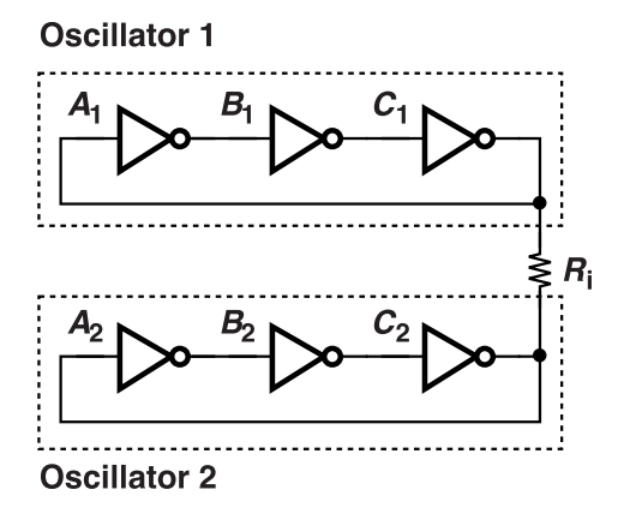

耦合振荡器

电路架构

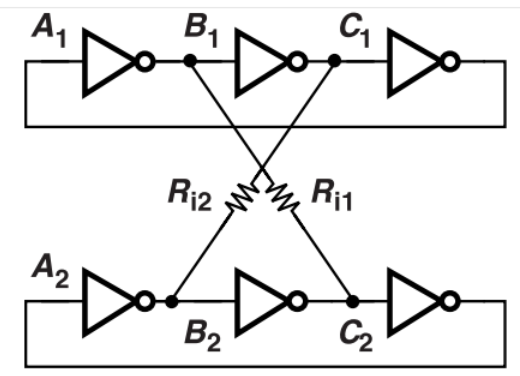

如果一个振荡器的输出的一小部分被“注入”到另一个振荡器中,那么它们可以同步。假设这两个电路同相振荡。节点A1和A2一起改变,没有电流流过Ri,没有能量交换。两个振荡器更倾向于同相工作,而不能产生互补输出。振荡器达到最小能量交换点。

相等的电阻Ri1和Ri2偶接B1到C2和C1到B2。发现能量交换发生在t1到t2和t3到t4(为什么?)也就是说,能量在三分之二的周期内进行交换。

另一方面,如果两个振荡器180度相差工作,则波形显示能量交换仅为周期的三分之一。因此,我们得出结论,电路更倾向于后一种模式。

上面两个振荡器不能在0到180◦之间的其他相位差下工作。在这种情况下,B1和C2之间的能量流比B2和C1之间的能量流持续的时间更长。这不可能发生,因为它与两个振子之间的对称性相冲突。

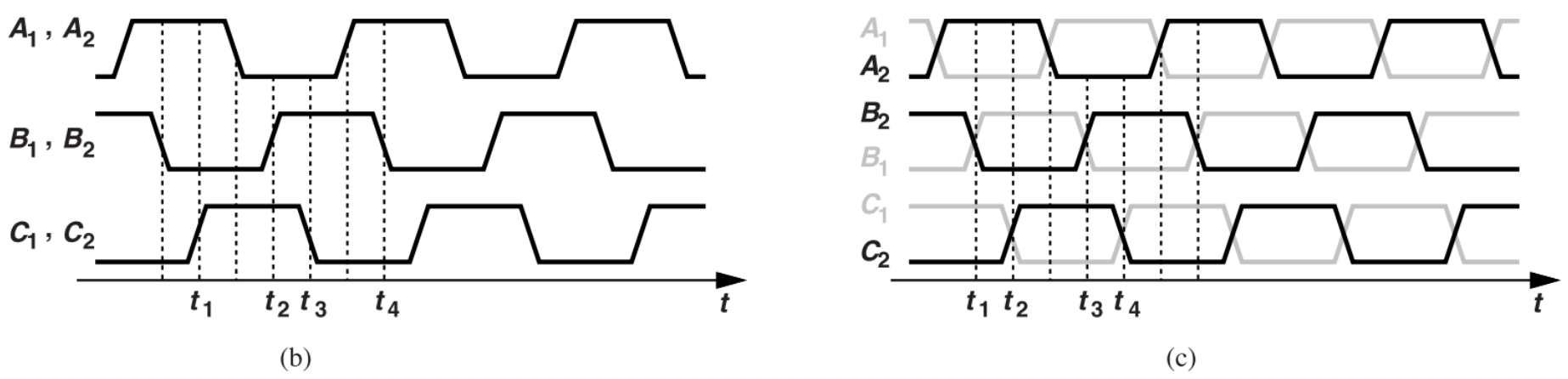

另一种产生互补波形的耦合布置如图所示。两个“反并行”(交叉耦合)反相器Inv 1和Inv2将一个振荡器信号的一小部分注入另一个振荡器。这里不鼓励同相操作(A1 = A2),因为它意味着耦合反相器的输入和输出电压相等(而不是互补),振荡器更倾向于以180◦的相位差操作,以便Inv1和Inv2仅注入瞬态电流。电路的对称性也阻止了其他相位差值。

Inv1和Inv2不能任意弱或强。如果它们很弱,并且振荡器的频率不匹配,那么同步(“注入锁定”)就不会发生。在这种情况下,振荡器相互“拉”,显示出损坏的输出。如果Inv1和Inv2过于强大,然后它们充当再生锁存器,在一个输出处永久地强制为1,在另一个输出处强制为零。根据经验,这些反相器的强度选择在两个回路内的主反相器的强度的20%左右。

耦合逆变器仅在A1和A2处呈现负载,从而在每个环周围产生系统相位不匹配。在需要所有相位的应用中,这个问题可以通过在其他节点之间添加类似的逆变器来解决。相分离是60◦的倍数,而不是180◦/(2^M)。

相位噪声

在2 GHz频率下设计耦合振荡器。主反相器的强度是耦合反相器的四倍。VDD = 0.95 V, T = 75℃,SS工艺角。

(W/L)N = 120 nm/240 nm, (W/L)P = 240 nm/240 nm,电路包含30个这样的单元反相器。因此,新设计消耗了大约10倍的功率。电源电流为115µA而不是10×14µA,但振荡频率也较低。实际上,10 log(140µA/115µA)恰好等于10 log(2.5 GHz/2.3 GHz)^2。因此,与简单的三级环相比,我们仍然期望相位噪声降低10db。因此,电流产生互补输出,几乎没有FOM损失。

电路仍然存在逆变器强度与VDD的依赖关系。随着VDD的波动,逆变器的延时也会波动;也就是说,两个回路的振荡频率沿同一方向变化。耦合振荡器的归一化电源灵敏度仅比单环的灵敏度低15%左右。

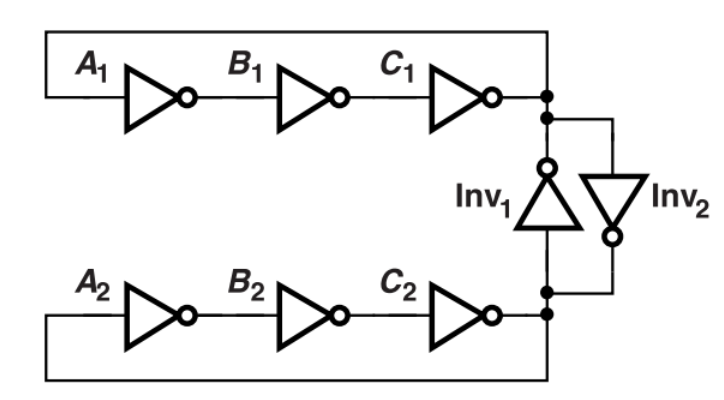

直接正交生成

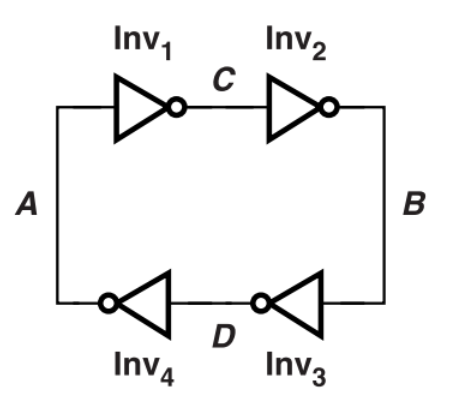

可以从基于逆变器的环形振荡器中获得互补的正交相位。暂时忽略每个级提供的反转,以频率f0 = 1/(8Td)振荡,其中Td表示门延迟。因此,A和B携带互补的波形,C和D也同样。而且,后两者相对于前两者是90°的异相。从另一个角度来看,环路由四个单极级组成,从而在连续节点之间产生90◦相分离。不幸的是,电路倾向于锁存:环路可以无限期地保持a = B = 1和C = D = 0。

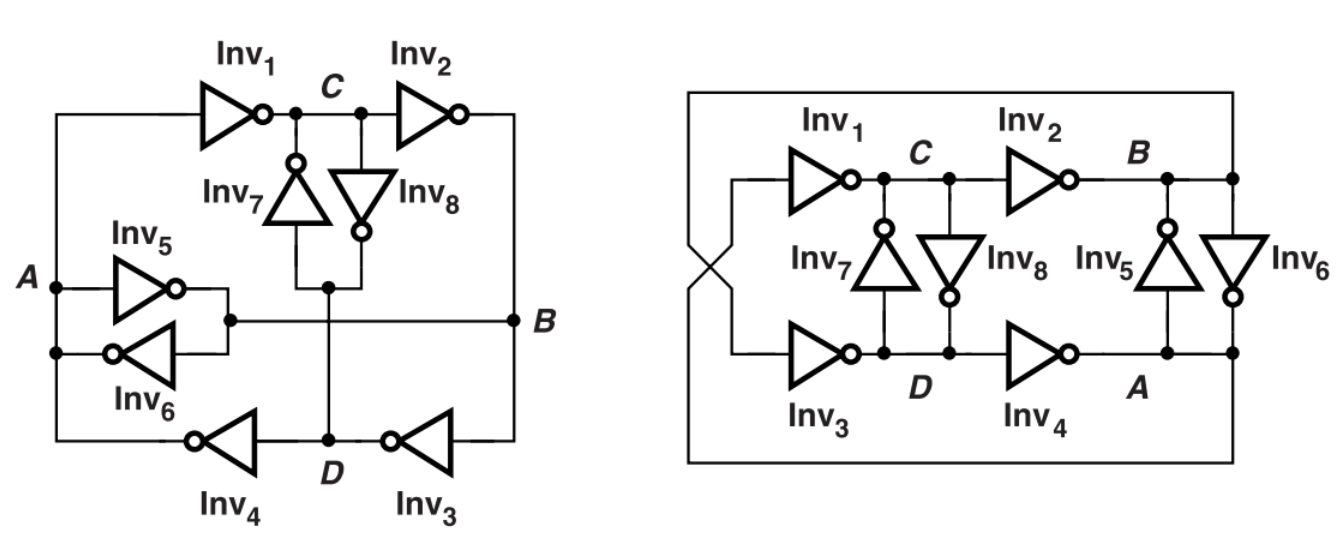

一对交叉耦合逆变器可以在其输入和输出节点之间对抗相等状态。在这里,交叉耦合逆变器足够强大,以确保主回路不会锁存。

相对于主回路中的逆变器,交叉耦合逆变器的尺寸应该如何确定?如果Inv1-Inv4倾向于锁定,前者必须对抗后者。从这个角度来看,Inv5-Inv8应该足够强大。

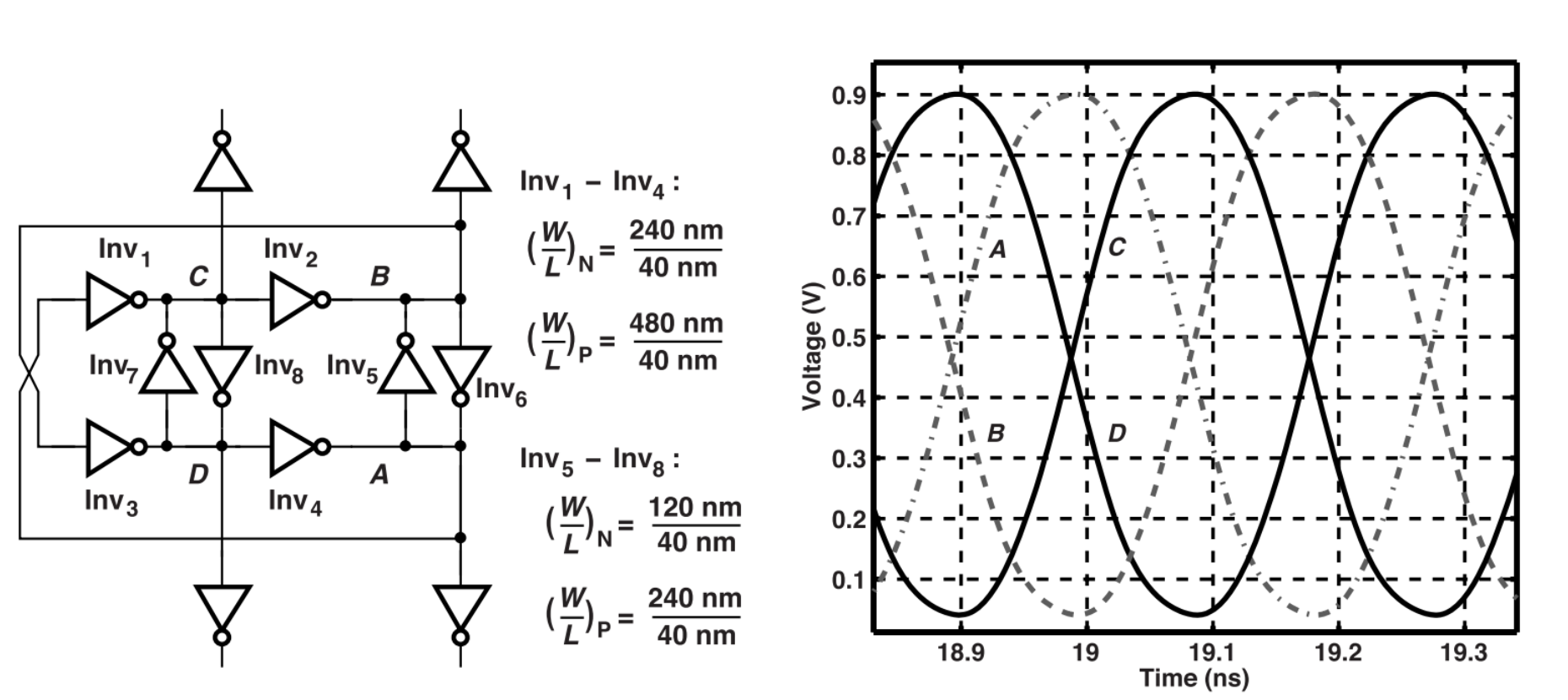

另一方面,这些逆变器也在过渡期间对抗Inv1-Inv4,既消耗功率又注入噪音。因此,Inv5-Inv8不应该太强。根据经验,我们选择Inv1-Inv4的强度与Inv5-Inv8的强度之比为2。在不匹配的情况下,较高的比率有可能导致锁定,而较低的比率则会降低优值。

假设晶体管的最小允许宽度为120 nm,我们选择主逆变器(W/L)N = 240 nm/40 nm, (W/L)P = 480 nm/40 nm,交叉耦合逆变器(W/L)N = 120 nm/40 nm, (W/L)P = 240 nm/40 nm。还将输出缓冲区附加到所有节点上。由于主逆变器和交叉耦合逆变器之间的争斗,正交波形表现出轻微的摆幅衰减。振荡频率f0为26.5 GHz。正交拓扑运行速度更快。电源电流为235µA。

在偏移量为1mhz时,相位噪声为- 50 dBc/Hz,比参考设计低3db。为了进行公平的比较,我们必须考虑(a)电源电流比,10 log(235 μ a /60 μ a) = 5.9 dB, (b)频率比,20 log(26.5 GHz/22.6 GHz) = 1.4 dB, (c)相位噪声差为3db。因此,正交设计优值差5.9−1.4−3 = 1.5 dB。这是产生正交相位的代价。

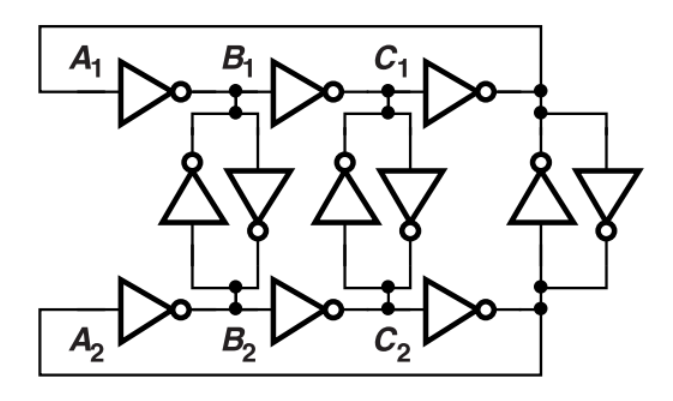

正交插值生成

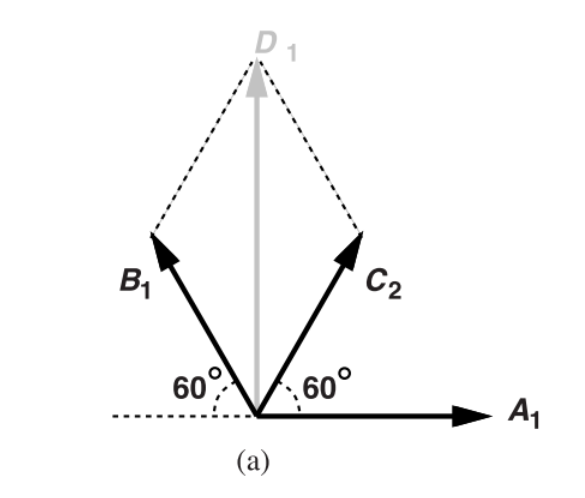

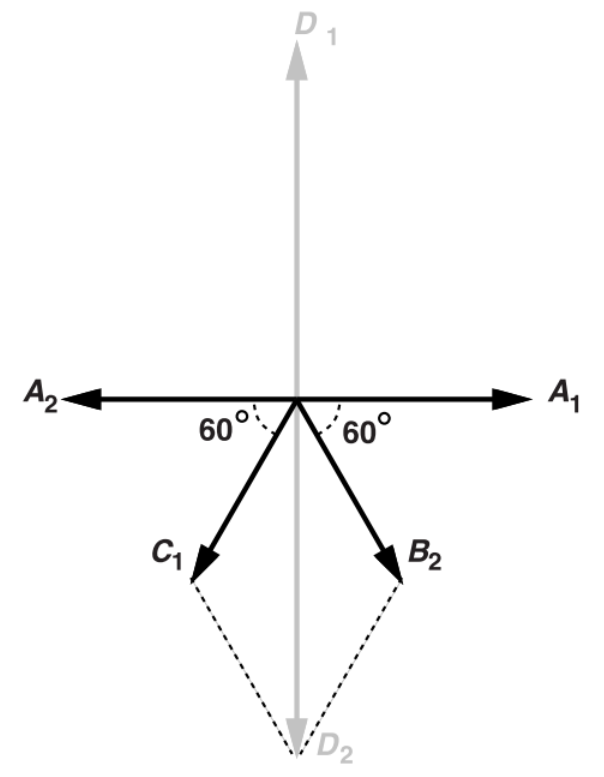

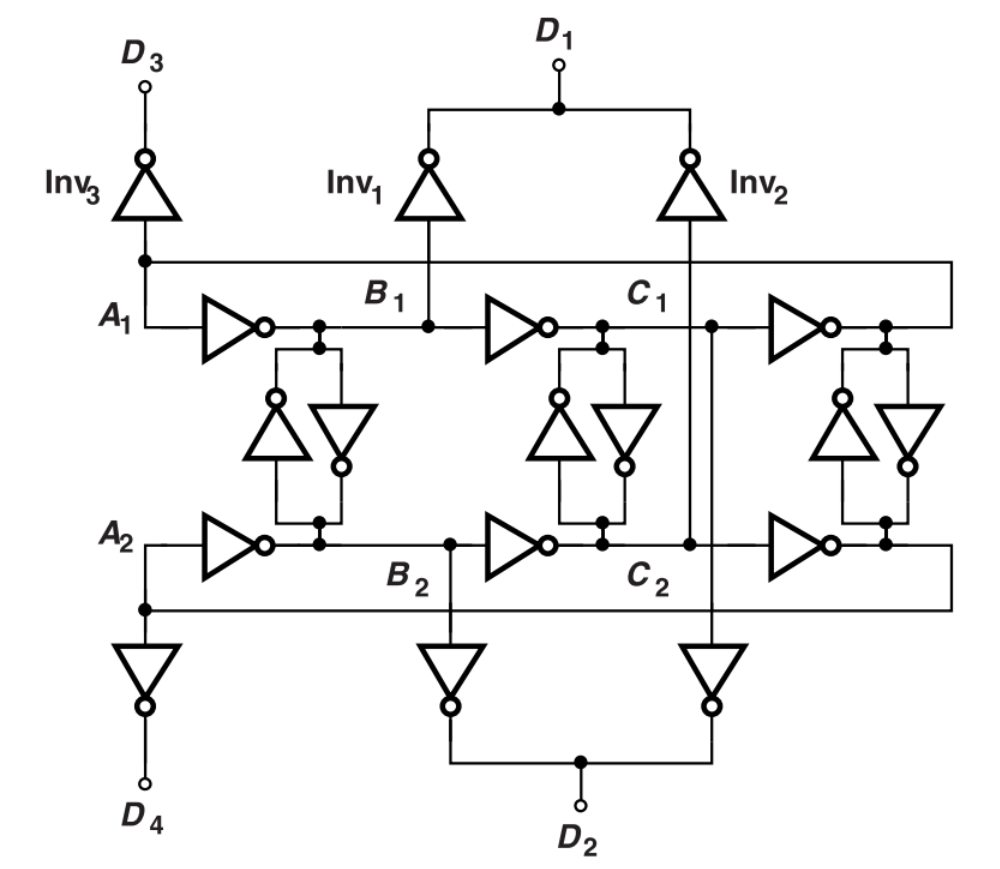

可以将同等权重的相量B1和C2相加,得到一个垂直于A1的插值相量。也可以对C1和B2重复进行,得到A1、D1、A2和D2作为期望的正交相。

考虑到B1和C2波形,我们认识到(B1 + C2)/2恰好位于两者之间。将B1和C2应用于两个逆变器并缩短其输出。暂时忽略信号反转,认为结果大致相当于(B1 + C2)/2。

inv1和Inv2是否会对抗和减弱(B1 +C2)/2的高低水平?不,当B1和C2都高或低时,两个逆变器不打架,内插输出接近供电轨道。

两个逆变器是否在t = t1附近打架?是的,它们必须斗争,这样它们才能在B1和C2之间产生插值输出。一个反相器中的NMOS器件和另一个反相器中的PMOS晶体管同时开启,产生内插输出电压。换句话说,电路在部分周期内吸收静电。

该电路还面临两个问题。首先,内插式逆变器引入的负载电容在B1和A1之间(以及B2和A2之间)造成相位失配。其次,Inv1和Inv2的有限延迟导致D1和A1(以及D2和A2)之间的另一个相位失配。

为解决上述问题,修改电路,四个输出,D1-D4,作为正交相。这种拓扑结构中的各种互连往往会引入明显的相位不匹配,需要仔细布局。

D1和D3驱动负载电容相等。在这种情况下,这两个信号是否经历了相位失配?是的。D1处的驱动强度大于D3处的驱动强度,因为D1由两个逆变器组成。为了纠正这种情况,我们应该确保在这些输出处看到的扇输出很小,即,Inv1-Inv3比后续阶段大几倍。

对相位噪声的降低可以忽略不计。由于内插逆变器位于振荡回路之外,因此它们的相位噪声不受(f0/f)^2函数的影响,因此仍然很小。由于这个原因,这些逆变器不需要使用大型晶体管。

参考文献

拉扎维,Design of CMOS Phase-Locked Loops

4669

4669

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?