Title:

[SystemVerilog]覆盖率——衡量IC验证完成程度

文章目录

1- 前言

在芯片验证过程中,已经为DUT设计了很多TC,经过了多次回归,回归中出现的Bug都一一修复。 但我们的验证程度究竟到达了什么样的程度,是否需要继续进行,又该怎样进行,是否有量化的标准指导验证工作接下来的方向?接下来就系统的介绍一下覆盖率——衡量IC验证完成程度。

2- 覆盖率类型

覆盖率通常分为以下3种:

代码覆盖率,功能覆盖率,断言覆盖率;其中前两项必须关注。

2.1- 代码覆盖率

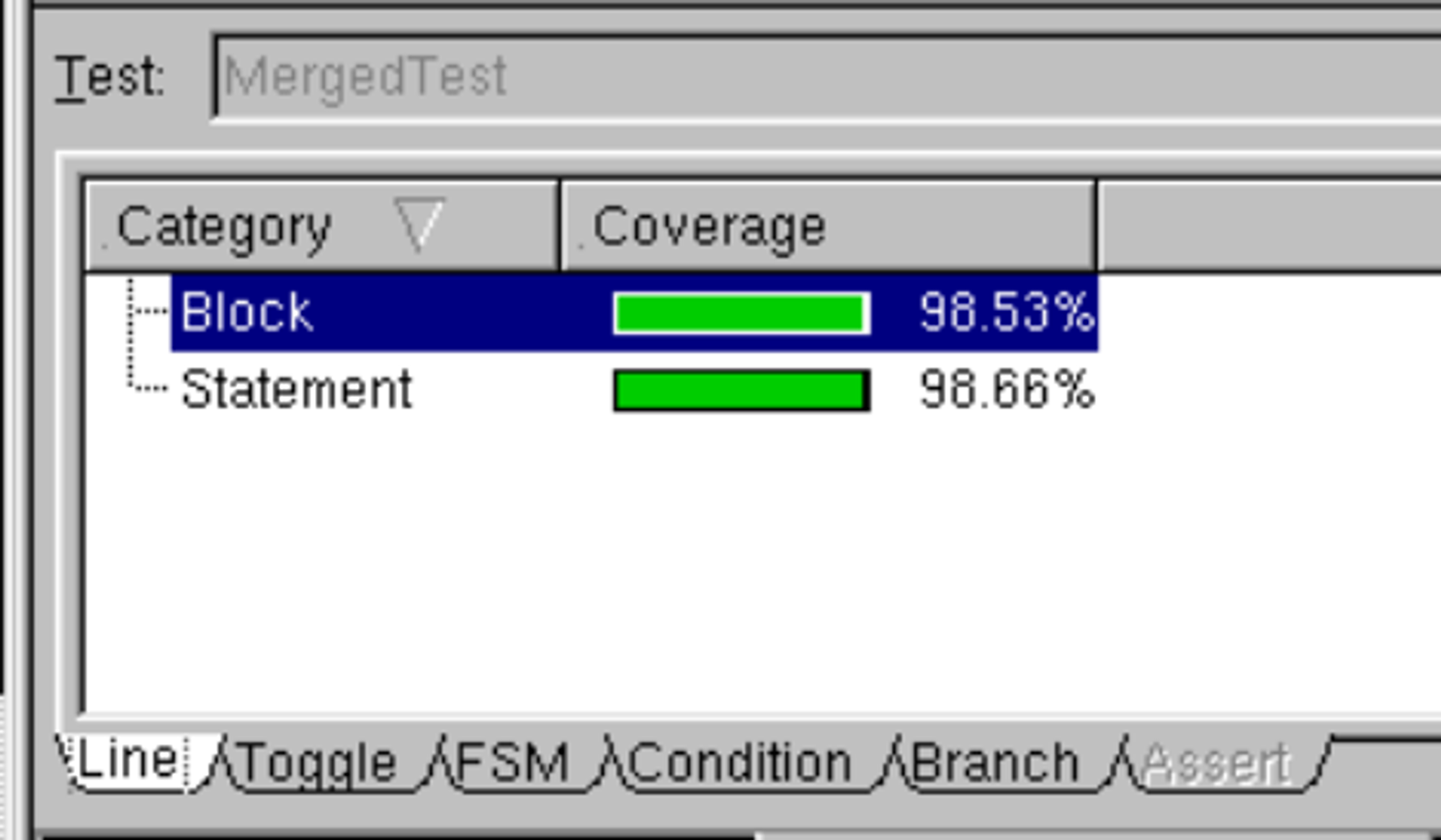

代码覆盖率包括 Line, Toggle, FSM, Condition, Branch覆盖率。

2.1.1- Line(行覆盖率)

定义:表示多少行代码已经被执行过;

分析:

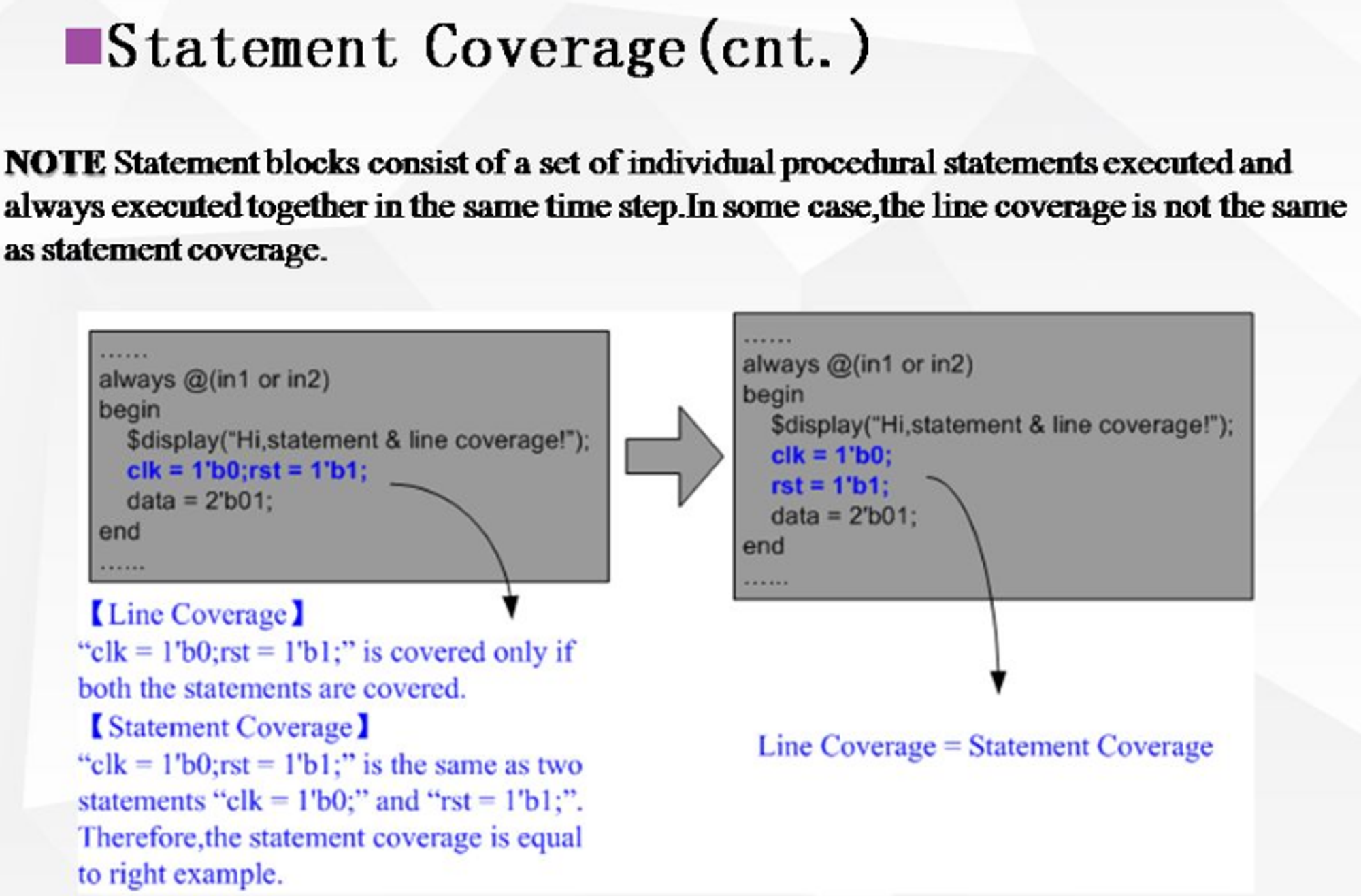

- Block: 表示代码块,包含在语句块间(eg begin…end);

- Statement:表示非Block代码;

- Statement Coverage 不全等于 Line Coverage;

2.1.2- Toggle(翻转覆盖率)

定义:表示对应bit是否完成了 0→1 和1→0的翻转;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

878

878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?