1-前言

IC后仿中出现了一个Timing violation问题, 在此做出分析,并给出解决方案。

2-问题描述与分析

IC后仿中发生Timing violation问题:

后仿log:

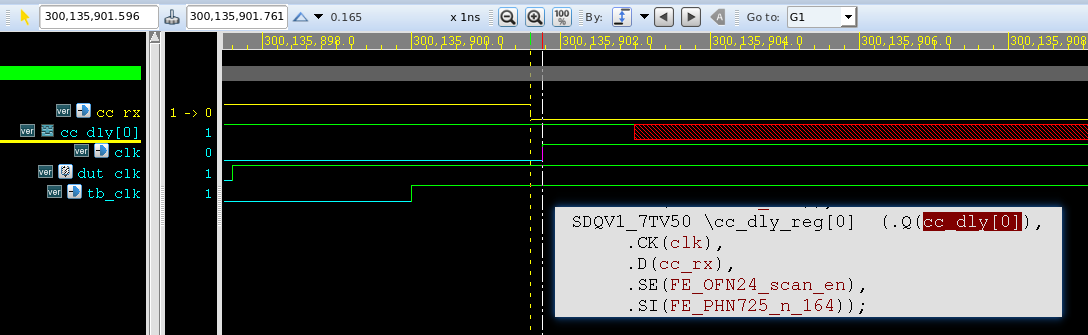

"/home/xx/xx.v", 15691: Timing violation in tb_top.xx\cc_dly_reg[0]

$setuphold( posedge CK &&& (ENABLE_NOT_SE == 1'b1):314047001.763ns, negedge D &&& (ENABLE_NOT_SE == 1'b1):314047001.596ns, limits: (0.409ns,0.017ns) );

后仿fsdb:

信号说明:

cc_rx: dut的input,cc_rx由testbench按intf.cb1驱动给dut;cc_dly[0]: 某一D触发器的输出;dut_clk/tb_clk: Testbench产生的时钟,一个给dut,

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

827

827

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?