FPGA自学笔记(二)仿真文件tb

一、创建文件

创建 simulation sources ,命名为 tb_模块名。

二、代码

1、定义reg,wire

因为要测试一个模块,所以该模块的input应该在测试文件中被赋值,只有reg类型可以被赋值。该模块的output应该在测试文件中被作为连线连接到下一个模块,或者作为下一个模块的输入,所以一能改被定义为wire类型。

代码如下(被测试模块):

module led_twinkle(

input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output [1:0] led //LED灯

);

代码如下(tb文件):

module tb_led_twinkle();

reg sys_clk;

reg sys_rst_n;

wire [1:0] led;

2、赋初值

代码如下(示例):

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0; //复位信号为0有效

#200

sys_rst_n = 1'b1; //200ns后复位信号变1

end

3、翻转时钟

always #10 sys_clk = ~sys_clk;

4、例化被测试模块

例化名=u_被测试模块名。如果是例化IP核,可以去 *.veo文件中copy。

Ctrl选中多行可以多行操作。

led_twinkle u_led_twinkle(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.led (led)

);

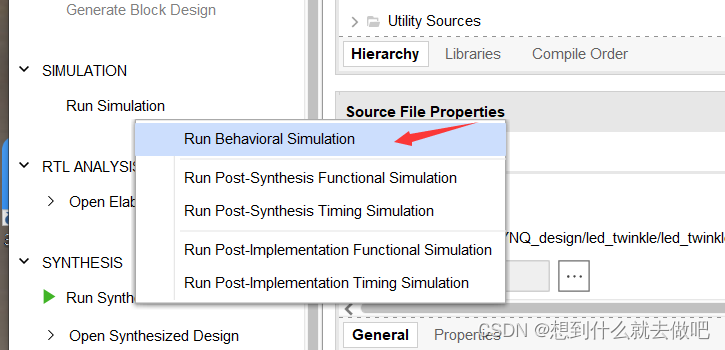

三、开始仿真

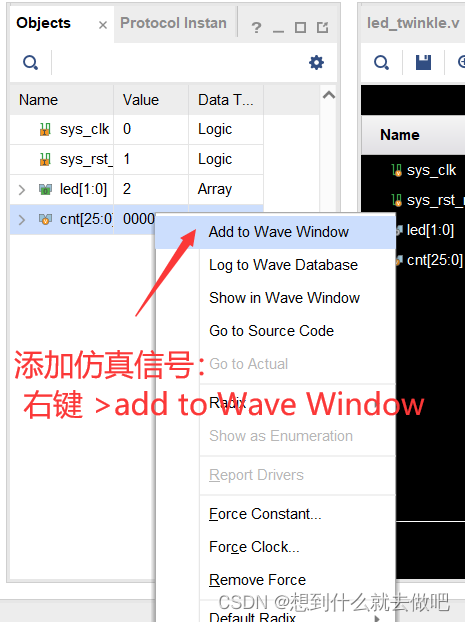

添加仿真信号

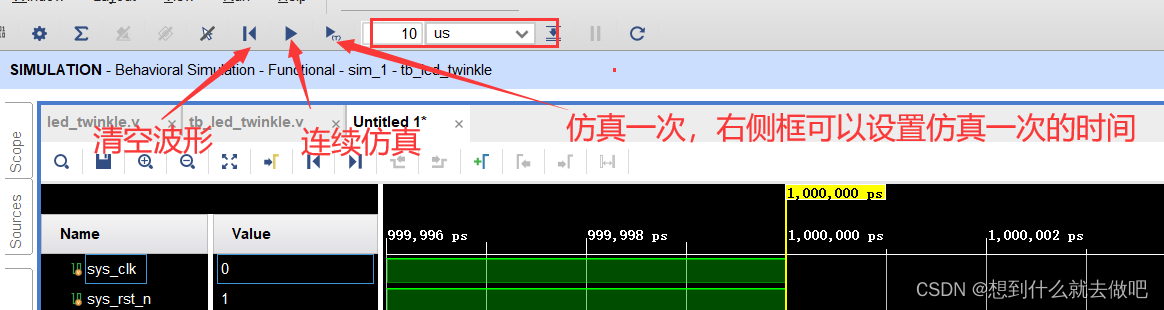

按钮含义

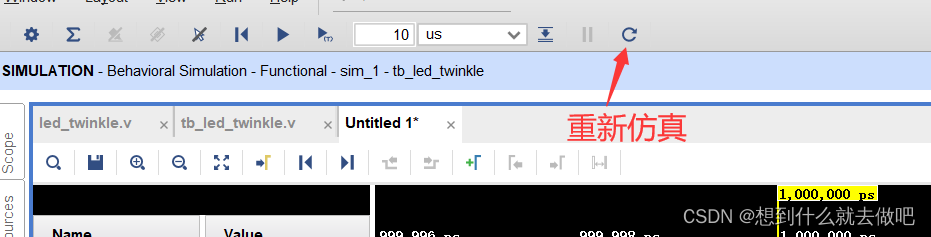

重新仿真

仿真过程中想要更改 .v 文件,直接改然后保存,点一下重新仿真即可。

6546

6546

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?