Vivado FPGA基础设计操作流程(2)

六、添加管脚约束

Synthesis结束之后,并且在Open Synthesized Design之后。用户可通过 I/O Planner 进行 IO 约束。

1. IO 约束有两种方式,第一种,在界面右上角选择I/O Planning;第二种,在菜单栏视图处下拉 I/O Planning view 点击进入 IO 规划视图界面

2. 选择之后会进入 IO 分配界面,根据开发板的说明手册,在I/O Ports给I/O端口分配引脚(Package Pin就是对应的FPGA芯片的引脚)和电平标准(I/O Std)。

1)开发板用的电平均为3.3v。点击每一个端口的下拉三角,选择3.3的电平(直接输入也可以)

2)设置端口管脚位置。点击每一个端口的下拉三角,根据开发板的说明手册,选择相应的管脚(直接输入也可以)进行设置。

3.点击左上角保存按钮(或者ctrl+s),选择OK继续。此时会弹出保存约束文件窗口,设置管脚约束的名字,与工程名保持一致。

此时,Sources的Constraints中会出现刚刚建立的管脚设置的文本mux_2.dxc文件。

七、设计实现

1. 在 Flow Navigator 下找到并展开Implementation。单击 Run Implementation 选项,开始执行实现过程。点击求和符号,能够查看实现过程。

2. 实现过程完成后会出现如图所示的 Implementation Completed 对话框。选择 Open Implemented Design,单击 OK 按钮。

八、比特流文件的生成与下载

将 Vivado 实现产生的网表文件转化为比特流文件,并且将比特流文件下载到 FPGA 芯片中。比特流文件用于完成对 FPGA 进行配置。

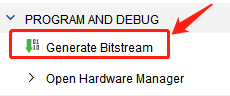

1. 在 Flow Navigator 窗口下找到 Program and Debug 选项并展开。单击Generate Bitstream 选项,开始生成比特流文件。

2. 比特流文件生成后,会出现如图所示的 Bitstream Generation Completed 对话框,选择 Open Hardware Manager 选项,单击 OK 按钮。

3.在图中,Open Hardware Manager 变为 Hardware Manager;如果没有,则单击Open Hardware Manager 打开 Hardware Manager。

4. 在左侧 Open Hardware Manager下,单击Open Target,然后单击 Auto Connect 连接设备(或者在Hardware Manager 界面中,单击Open Target,点击Auto Connect 连接设备)

5. 在 Hardware Manager 界面下出现选中的设备。

6.在 Hardware Manager 界面中找到并右键单击 xc7a35t_0(1),在浮动菜单中单击Program Device选项。

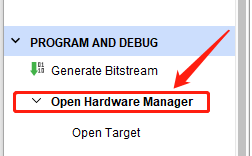

<font color=#999AAA 7.出现 Program Device 对话框。默认情况下比特流文件会自动选中;如果没有单击“…”按钮,找到并选中 mux_2.bit 文件。在 Program Device 对话框中单击 Program 按钮,开始下载。

<font color=#999AAA 8.在开发板上验证该设计。验证方法:程序下载完成后,根据引脚的设置,去查看开发板对应的功能。

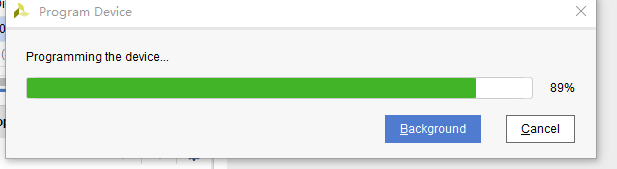

九、Vivado 工程文件的结构

上述步骤建立好工程后,自动生成的文件

project_name.cache:Vivado 软件的运行缓存

project_name.hw:所有波形文件

project_name.ip_user_files:用户关于 IP 的文件

project_name.runs:编译与综合结果,.\impl_1 文件夹中的.bin 和 .bit 即为编译生成的可执行文件

project_name.sdk:SDK 环境代码,一般是 ZYNQ 设计中关于 PS 端的代码

project_name.sim:仿真结果

project_name.srcs:所有用户编写的源码、仿真文件与约束文件

project_name.tmp:自制 IP 核时的临时工程文件夹,IP 核设计完成后会自动清理

project_name.xpr:Vivado 工程启动文件

后记:那些不记得过去的人,注定要重复过去。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?