背景:我本人没有怎么接触过FPGA,但是这次一上来就被要求做FPGA的工作,实在是让我感到无从下手,前前后后忙活了好几天才第一次上电成功,所以把整个经过整理了一下,以便方面后来人。

开发平台:Vivado 2015.2

FPGA :Xilinx Virtex-7系列芯片

一上来就碰到这种高端FPGA芯片,没有什么资料,至于下面的FPGA的板子也是自制的(上面没有按钮,没有数码管,只有2个led灯),所以感到无从下手。那么针对这种情况怎么办呢?下面将全面介绍一下。

//************************************************************//

1.时钟:时钟是驱动FPGA工作的关键,首先我们来看怎么引入时钟。

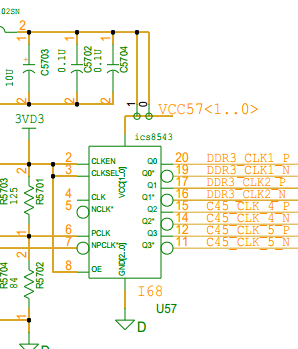

从图中可以看出,使用了ICS8543芯片,查看该芯片的datasheet,可以知道该芯片的输出为4对差分口,IO标准为LVDS,并且通过查看原理图可以知道Q3和Q3*是作为FPGA工作的时钟,此时记下在FPGA中的引脚。

//************************************************************//

2.建立工程:这一步网上有很多教程,我在这里就略过了

//************************************************************//

3.调用Clocking wizard:为了得到稳定的适合XilinxFPGA的时钟,需要使用Xilinx提供的一个IP核

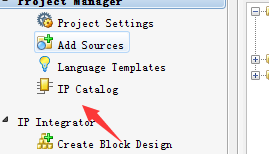

选择IP Catalog

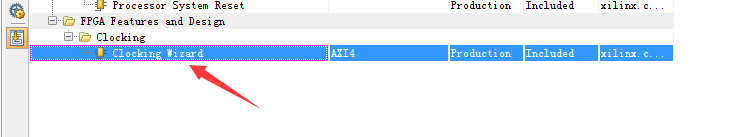

双击Clocking Wizard

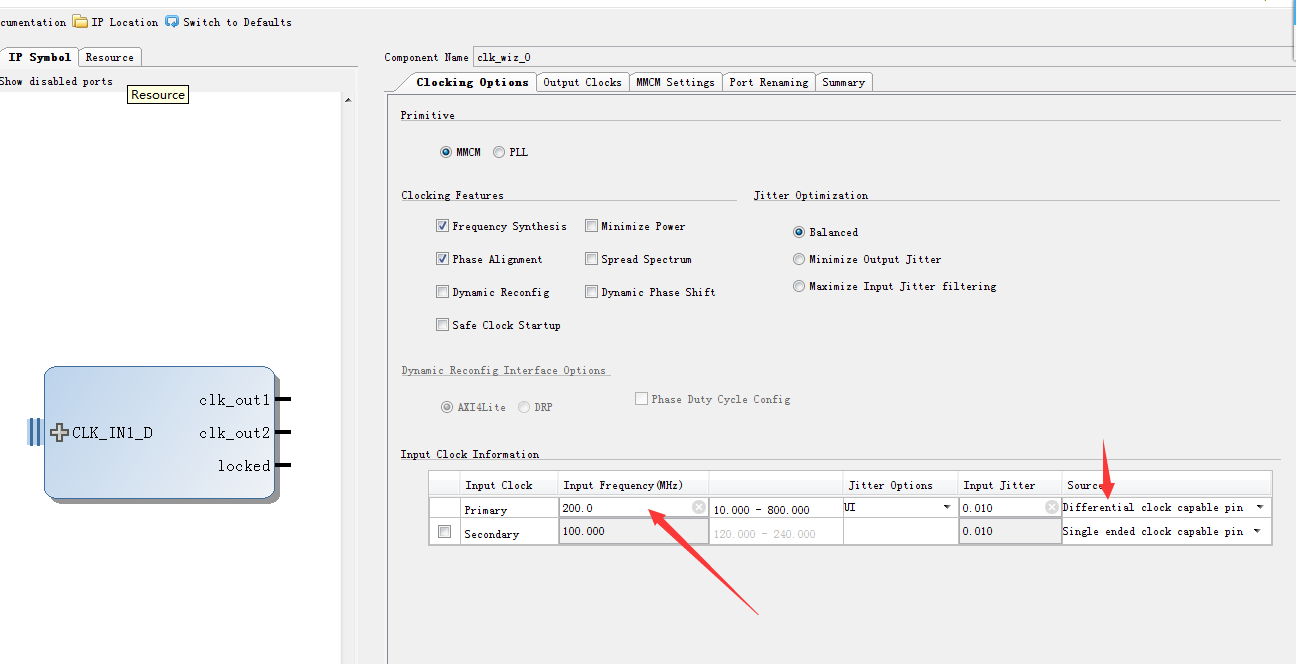

设置外部时钟的输入频率,我这里是200M的时钟,由于时钟使用的是差分传输,所以我在这里选择了Differential clock capable pin

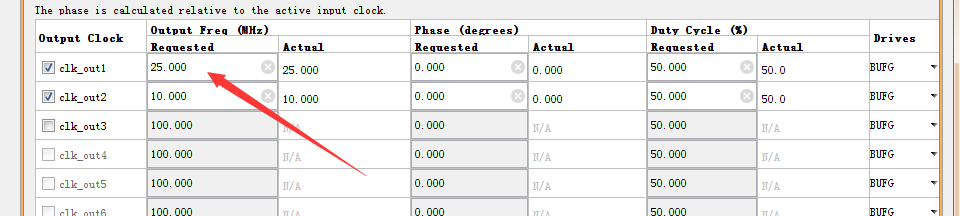

这里是填写输出时钟,根据需要选择即可

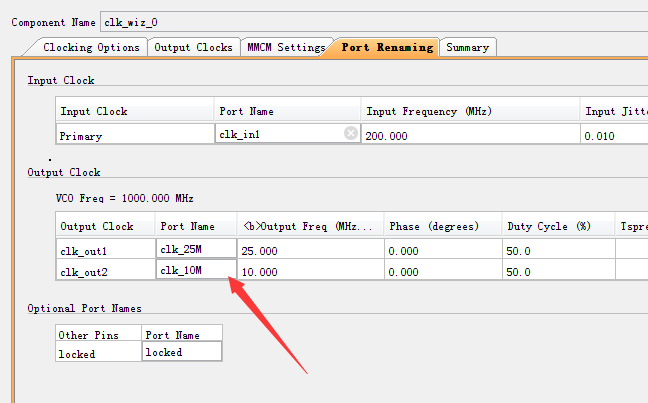

这里是对实例化的IP core的输出端口的重命名,方便自己记忆

//************************************************************//

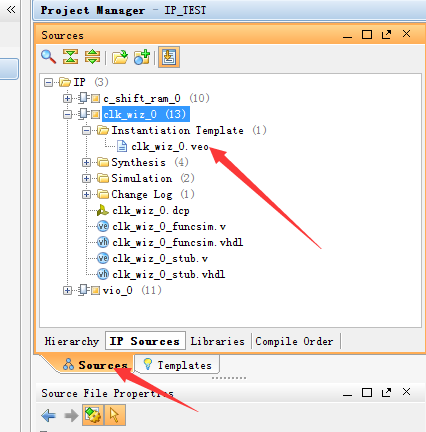

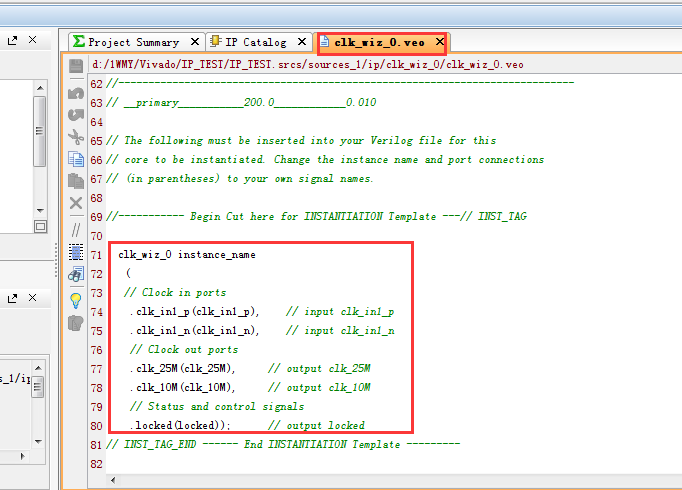

4.使用IP Core:使用Vivado提供的例化模版在v文件中实例化

复制红框中的内容,粘贴到自己的工程文件中

//************************************************************//

5.编写代码:

在代码很简单,就是利用输出的25M时钟,做了一个分频,点亮一盏LED灯,由于我使用的平台没有外部按键,所以又调用一个VIO的IP core来做复位控制,关于VIO这个IP Core我会在以后的文章中提到。

module top(

input clk_in1_p,

input clk_in1_n,

output reg flag,

output led

);

wire clk_25M,clk_10M;

wire locked,rst_n;

reg [31:0] cnt_r;

clk_wiz_0 instance_name

(

// Clock in ports

.clk_in1_p(clk_in1_p), // input clk_in1_p

.clk_in1_n(clk_in1_n), // input clk_in1_n

// Clock out ports

.clk_25M(clk_25M), // output clk_25M

.clk_10M(clk_10M), // output clk_10M

// Status and control signals

.locked(locked)); // output locked

always @ (posedge clk_10M, negedge rst_n) begin

if(rst_n == 0)begin

cnt_r <= 0;

end

else begin

if (cnt_r == 32'b1111_1111_1111_1111_1111_1111_1111_1111) begin

cnt_r <= 0;

end

else cnt_r <= cnt_r +1;

end

end

always @ (posedge clk_10M)begin

if(cnt_r < 32'b1000_0000_0000_0000_0000_0000_0000_0000) flag <= 1;

else flag <= 0;

end

vio_0 your_instance_name (

.clk(clk_10M), // input wire clk

.probe_in0(cnt_r), // input wire [31 : 0] probe_in0

.probe_out0(rst_n), // output wire [0 : 0] probe_out0

.probe_out1(led)

);

endmodule//************************************************************//

6.配置管脚:代码编写好之后,为了让FPGA能够工作,需要将module的输出输入管脚配置到实际的地方才能正常工作

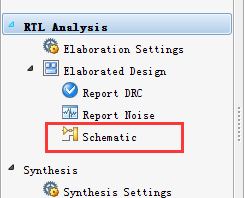

打开Schematic

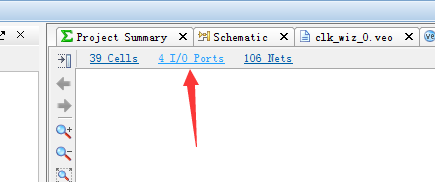

点击IO Ports

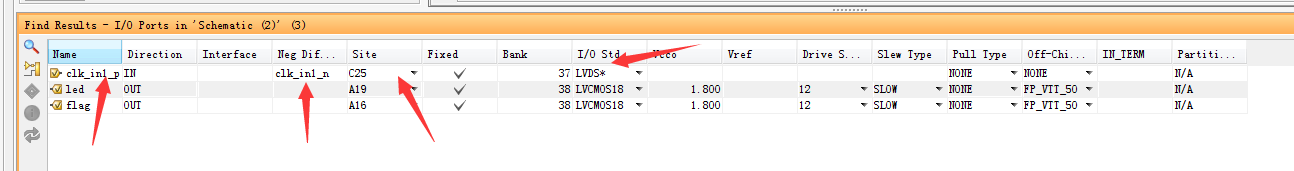

这里就是配置管脚的地方,可以看到我将clk_in1_p配置为了C25(由于是差分管脚的关系,Vivado能够自动识别,自动的把clk_in1_n配置为了C26),根据之前ICS8543的datasheet,IO std应该设置为LVDS。flag是我用来控制led灯的管脚,分配到了a16(不同板子位置不一样,这个需要查看原理图才能知道),至于还有一个名为“led”的引脚,这个大家可以暂时忽略,这个引脚是直接被VIO控制的,在以后会讲到。

7.生成bit文件:这就是最后一步了,虽然过程看起来简单,但是要成功的来到这一步也是很困难的,如果一切顺利的话,这里就能够生成bit文件了(因为没有配置vio核,所以如果直接用我的代码的话,是会报错的,需要删除vio,并且对相应的输入输出进行修改)

这里吐槽一下Vivado,我用的电脑是I7-4790+16G内存+SSD,从头跑一次也要快10分钟的时间,简直太慢了。

931

931

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?