一、 什么是奇偶校验

奇偶校验是一种串行数据传输校验数据传输正确性的重要方法。根据传输的二进制数位中“1”的个数是奇数或偶数来进行校验。采用奇数的称为奇校验,采用偶数的称为偶校验。采用哪种校验是事先定好的。一般使用奇偶校验都会在传输数据的停止位之前设置一个奇偶校验位,用它使这组二进制数中“1”的个数为奇数或偶数。若使用奇校验,则当接收端收到这组二进制数时,校验“1”的个数是否为奇数,从而确定传输代码的正确性。

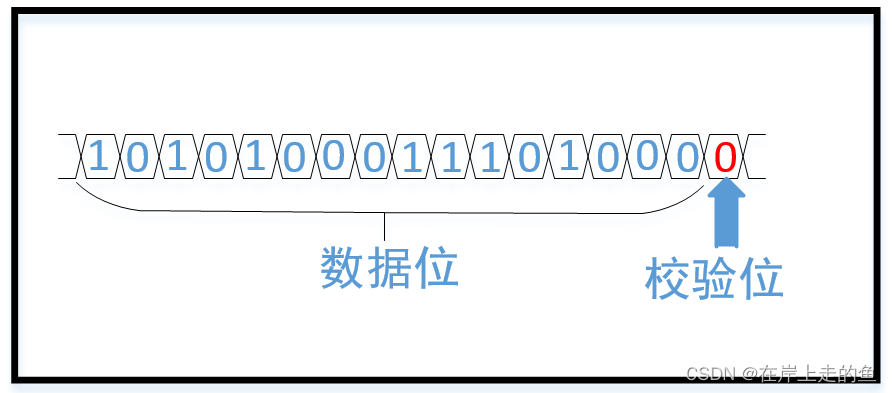

例如,输出一组16bit二进制数据,为“10101000 11101000”,该组数据共有7个“1”。若使用奇校验,则校验位应为0,传输数据实际为16bit数据+1bit奇校验位,即“10101000 11101000 0”;若使用偶校验,则校验位应为1,传输数据实际为16bit数据+1bit偶校验位,即“10101000 11101000 1”。

数据位和校验位中的“1”的总个数是靠校验位的填充来实现。

数据位和校验位中的“1”的总个数是靠校验位的填充来实现。

二、如何实现输入数据的奇偶校验

根据输入串行数据二进制数据流,实时生成所输入数据的奇/偶校验位。如果设置的是偶校验,则

订阅专栏 解锁全文

订阅专栏 解锁全文

777

777

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?