Verilog快速入门

(1) 四选一多路器

(2)异步复位的串联T触发器

(3)奇偶校验

(4)移位运算与乘法

(5)位拆分与运算

(6)使用子模块实现三输入数的大小比较

(7)4位数值比较器电路

(8)4bit超前进位加法器电路

(9)优先编码器电路①

(10)用优先编码器①实现键盘编码电路

(11)8线-3线优先编码器

(12)使用8线-3线优先编码器实现16线-4线优先编码器

(13)用3-8译码器实现全减器

(14)使用3-8译码器①实现逻辑函数

(15)数据选择器实现逻辑函数

(16)状态机

(17)ROM的简单实现

(18)边沿检测

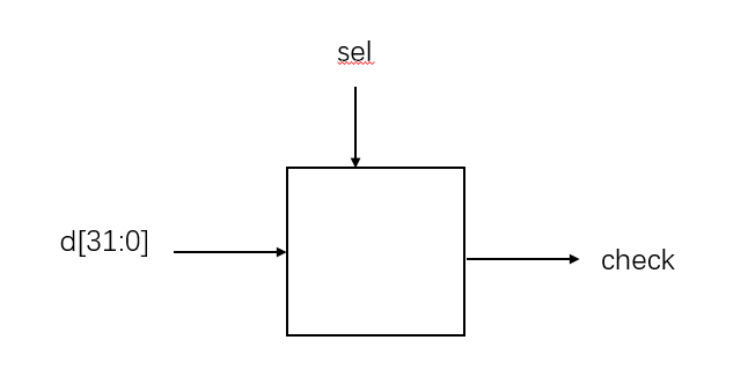

一、题目描述

现在需要对输入的32位数据进行奇偶校验,根据sel输出校验结果(1输出奇校验,0输出偶校验)

二、解析与代码

1. 奇偶校验

- 简单理解奇偶校验

奇校验:原始码流+校验位 总共有奇数个1

偶校验:原始码流+校验位 总共有偶数个1

- 计算奇偶校验的方法

按位求异或得到奇校验结果,对其求反得到偶校验结果

- 连续进行异或 odd = ^bus 对bus进行异或位操作

2. 代码如下:

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

//*************code***********//

assign check = (^bus)^(~sel);

//or

//even_bit = ^bus;

//odd_bit = ~even_bit;

//check = sel ? even_bit : odd_bit;

//*************code***********//

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?